Наиболее близким к изобретению по технической сущности является устрой- ство для управления вводом-выводом, содержащее три блока синхронизации обмена, блок памяти, исполнительный регистр, узел модификации, регистр ввода, первый блок приоритета, первый и второй буферы, узел запуска, блок управления, блок связи с памятью, входные и выходные интерфейсные шины, входные шины данных, шину строба, шину команды, выходные шины адреса -данных, шины запросов в оперативную память и шины запросов в

центральный процессор, информацион- 1 ные входы блоков синхронизации обмена соединены с информационным, выходо первого буфера, интерфейсные входы блоков синхронизации обмена являются входными интерфейсными шинами, информационные выходы блоков синхронизации обмена соединены с информационным входом регистра ввода и входом запросов первого блока приоритета, управляющие выходы блоков синхронизации обмена соединены с входом состояния блока управления, инiтерфейсные выходы блоков синхронизации обмена соединены с выходными интерфейсными шинами, третьи информационные входы блока памяти и вторые информационные входы узла модификации подключены к выходу регистра ввода, выход первого блока приоритета подключен к управляющему входу регистра ввода, адресному входу блок Ьамяти и входу подтверждения блоков синхронизации обмена, информационный выход блока памяти соединен с первым информационным входом исполнительного регистра, выход которого соединен с первыми информационными вхо.дами блока памяти и узла модификации, выход которого подключен к второму информационному входу блока памяти, первый управляющий выход блока управления соединен с управляющими входами первого, второго и третьего блоков синхронизации обмена, выход запросов блока управления явля- |ется выходной шиной запроса в цент- ральный процессор, командно-запросный выход блока управления соединен вторым вхбдам запроса первого блока приоритета, первым командным входом регистра ввода, установочный выход блока управления подключен к установочному входу узла запуска ка;

5

налов, управляющий выход которого подключен к установочному входу блока управления, ёторой информационный вход которого и второй командный вход регистра ввода соединены с информационным выходом первого буфера, информационный выход которого со- {единен с входной шиной данных, вход- ная шина строба от центрального процессора соединена с входом строби- рования блоке управления, а входная шина команды - с командным входом блока управления, информационный выход блока связи с памятью соединен с выходной шиной адреса-данных, выход запроса блока связи с памятью подключен к шине запроса в оперативную память.

Однако в известном устройстве модификация адресов и данных при передаче информации с внешних устройств в оперативную память выполняется в узле модификации, который является общим для всех каналов и используется в разделении времени. При эффективном использовании оборудования это не позволяет обслуживать внешние устройства с высокой скоростью обме

на, например накопители на магнитных

дисках емкостью 100, 200 и 317 Мбайт. Цель изобретения - повышение быстродействия устройства для управления вводом-выводом.

Поставленная цель достигается тем, что в устройство, содержащее m блоков синхронизации обмена, блок памяти, исполнительный регистр, узел модификации, регистр ввода, первый

блок приоритета, первый и второй буферы, узел запуска каналов, блок управления, блок связи с памятью,входные и выходные интерфейсные шины, входные шины данных, шины строба от

центрального процессора, шины команды, выходные шины адреса-данных, шину запросов в оперативную память и шину запросов в центральный процессор, информационные входы блоков

синхронизации обмена соединены с информационным выходом первого буфера, интерфейсные входы блоков синхронизации обмена соединены с входными интерфейсными шинами, информационные выходы блоков синхронизации обмена соединены с информационным входом регистра ввода и входом запросов первого блока приоритета, управляющие выходы блоков синхронизации обмена соединены с входом состо- i яния блока управления, интерфейсные выходы блоков синхронизации обмена соединены с выходными интерфейсными ,

шинами, третьи информационные входы блоков памяти и вторые информационные входы узла модификации подключены к выходу регистра ввода, выход первого блока приоритета подключен к управляющему входу регистра ввода, адресному входу блока памяти и входу подтверждения блоков синхронизации обмена, информационный выход блока памяти соединен с первым информационным в ходом исполнительного регистра, выход которого соединен с первыми информационными входами блока памяти и узла модификации, выход которого подключен к второму информационному входу блока памяти, первый управляющий выход блока управления соединен с управляющими входами блоков синхронизации обмена, выход запроса блока управления соединен с выходной шиной запроса в центральный процессор, командно-запросный

выход блока управления соединен с вторым входом запроса первого блока приоритета, первым командным входом регистра ввода, установочный выход блока управления подключен.к установочному входу узла запуска каналов, управляющий выход которого соединен с установочным входом блока управления, второй информационный вход которого и второй командный вход регистра ввода соединены с информационным выходом первого буфера, информационный вход которого подключен к входной шине данных, входная шина строба от центрального процессора соединена с входом стробирова- ния блока управления, а входная шина команды подключена к командному входу блока управления, информационный выход блока связи с памятью соединен с выходной шиной адреса-дан- ных, выход запроса блока связи с памятью соединен с шиной запроса в оперативную память, введены коммутатор памяти, второй блок приоритета и п селекторных каналов с п входными и п выходными интерфейсными шинами, причем адресный вход второго буфера Ч подключен к выходу исполнительного регистра, информационный вход - к- вы ходу регистра ввода, адресный и ин- ;

0

5

0

5

0

5

формационный выходы второго буфера соединены с первыми адресными и информационными входами коммутатора, памяти, к вторым информационному и адресному входам которого подключены адресные и информационные выходы п селекторных каналов соответственно, к установочному входу коммутатора памяти и к второму входу запроса блока связи с памятью подключен выход подтверждения второго блока приоритета, а выход коммутатора памяти соединен с информационным- входом блока связи с памятью, первый вход запроса второго блока приоритета, второй информационный вход исполнительного регистра, вход модификации узла модификации и управляющий вход блока памяти соединены с командно-запросным выходом блока управления, а второй вход запросов второго блока приоритета подключен к третьим выходам запросов п селекторных каналов, информационные с запросом выходы которых соединены с информационным входом регистра ввода и первым входом запросов первого блока приоритета, выходы состояний п селекторных каналов подключены к входу состояния блока управления, вход подтверждения соединен с выходом подтверждения второго блока приоритета, командные входы п селекторных каналов соединены с выходом регистра ввода, входы подтверждения п селекторных каналов подключены к выходу первого блока приоритета, информационные входы п селекторных каналов соединены с выходом

0 первого буфера, управляющие входы п селекторных каналов подключены к управляющему выходу блока управления,, интерфейсные входы и выходы п селекторных каналов соединены с входными

5 и выходными интерфейсными шинами, при этом каждый селекторный канал содержит дополнительный блок синхронизации обмена, блок развязки, счетчик адреса, счетчик количества байтов,

0 буферный усилитель, при этом информационный вход дополнительного блока синхронизации обмена соединен с информационным входом селекторного канала, интерфейсный вход дополнитель5 ного блока синхронизации обмена подключен к интерфейсному входу селекторного канала, управляющий вход до- полнительного блока синхронизации

к управляющему входу селекторного канала, вход подтверждения дополнительного блока синхронизации обмена соединен с выходом подтверждения блока управления каналом, информационный и управляющий выходы дополнительного блока синхронизации обмена соединены соответственно с информационным и управляющим входами блока развязки, первый вход подтверждения которого подключен к первому входу подтверждения селекторного канала, второй вход подтверждения блока развязки соединен с вторым входом подтверждения селекторного канала, выходы состояния, информационный с запросом, информационный и запроса блока развязки соединены с одноименными выходами селекторного канала соответственно, выход сдвига блока развяки подключен к входам сдвига счетчика адреса и счетчика количества байтов, информационные входы которых соединены со стробирующим входом селекторного канала, к командному входу которого подключены управляющие входы счетчика адреса и счетчика количества байтов, выход счетчика адреса соединен с адресным входом буферного усилителя, вход подтверждения которого соединен с вторым входом подтверждения селекторного канала, а выход буферного усилителя подключен к адресному выходу селекторного канала, выход счетчика количества байтов соединен с управляющим входом дополнительного блока синхронизации обмена.

Второй блок приоритета, коммутатор памяти и га селекторных каналов каждый состоит из блока синхронизации обмена., коммутатора данных, бло- ,ка управления каналом, регистра адреса, регистра количества байтод, узла модификации адреса, узла модификации количества байтов и блока анализа количества байтов.

Введение этих блоков в указанной связи с остальными блоками устройства для управления вводом-выводом обеспечивает обмен информацией между внешними устройствами и памятью вычислительной машины параллельно с работой центрального процессора.

Устройство состоит из каналов, позволяющих одновременно выполнять обмен с различными внешними устрой- ствами.

o

S

0

5

0

5

0

5

O

5

Предлагаемое устройство является групповым, его оборудование исполь- зуется несколькими каналами в раз- делении времени. Блоки синхронизации обмена являются индивидуальными для каждого канала.

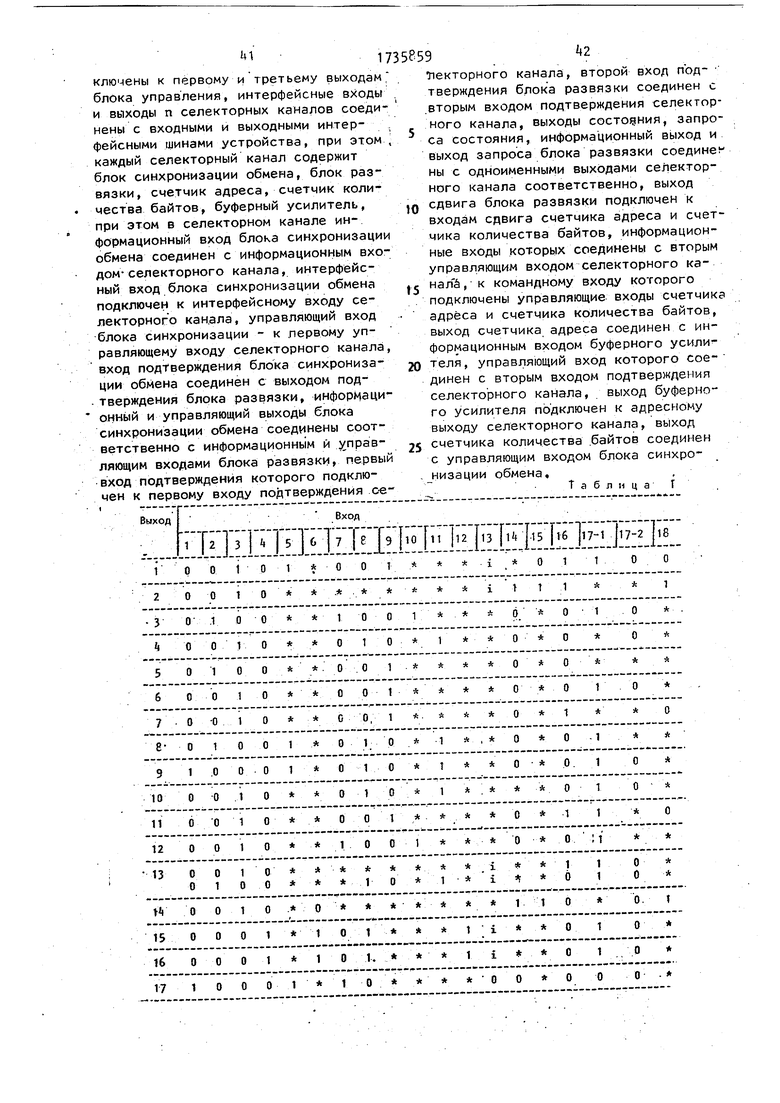

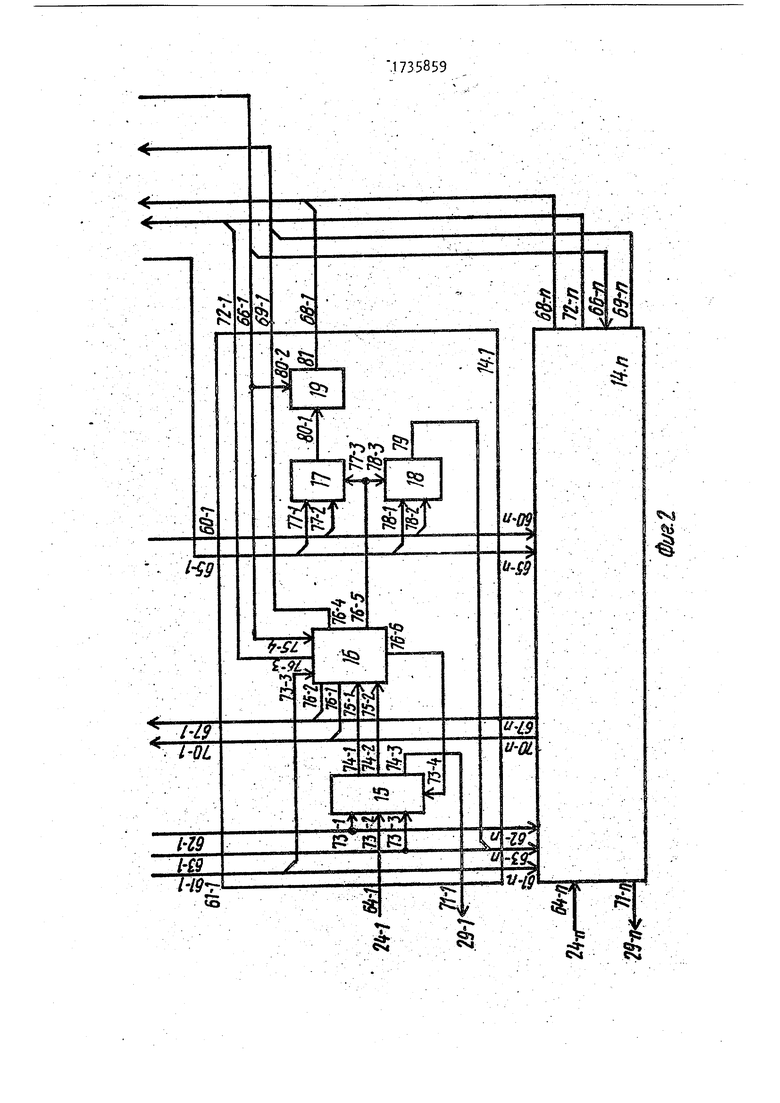

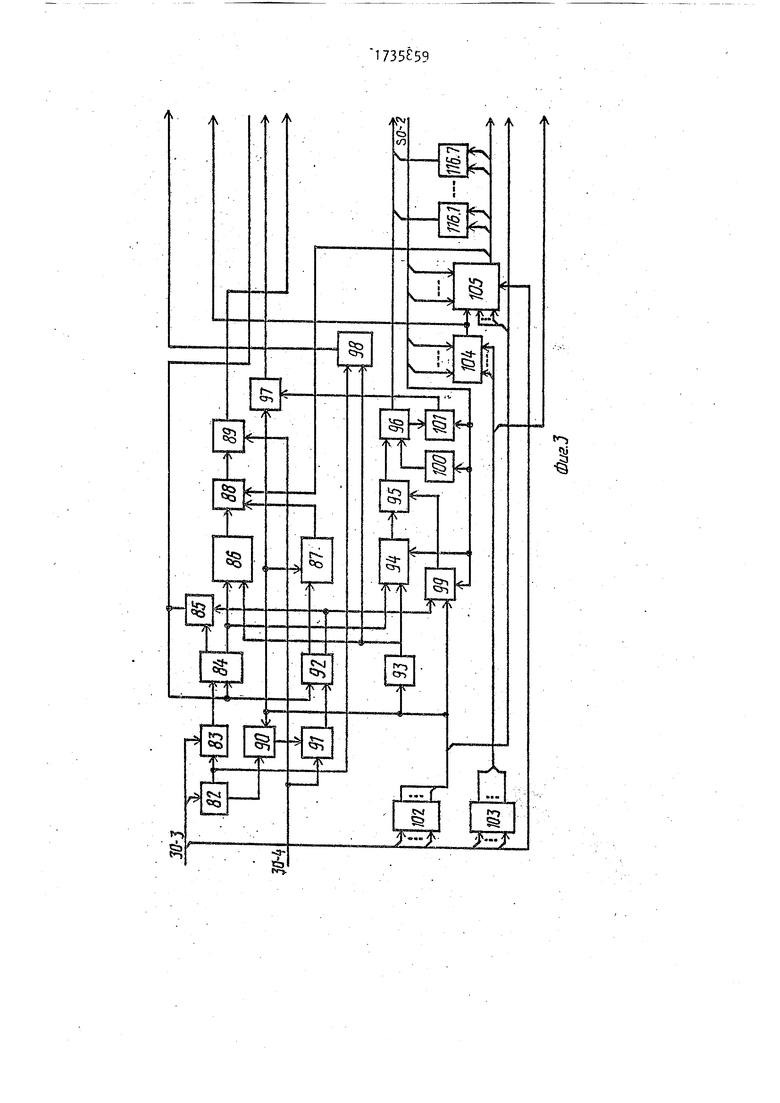

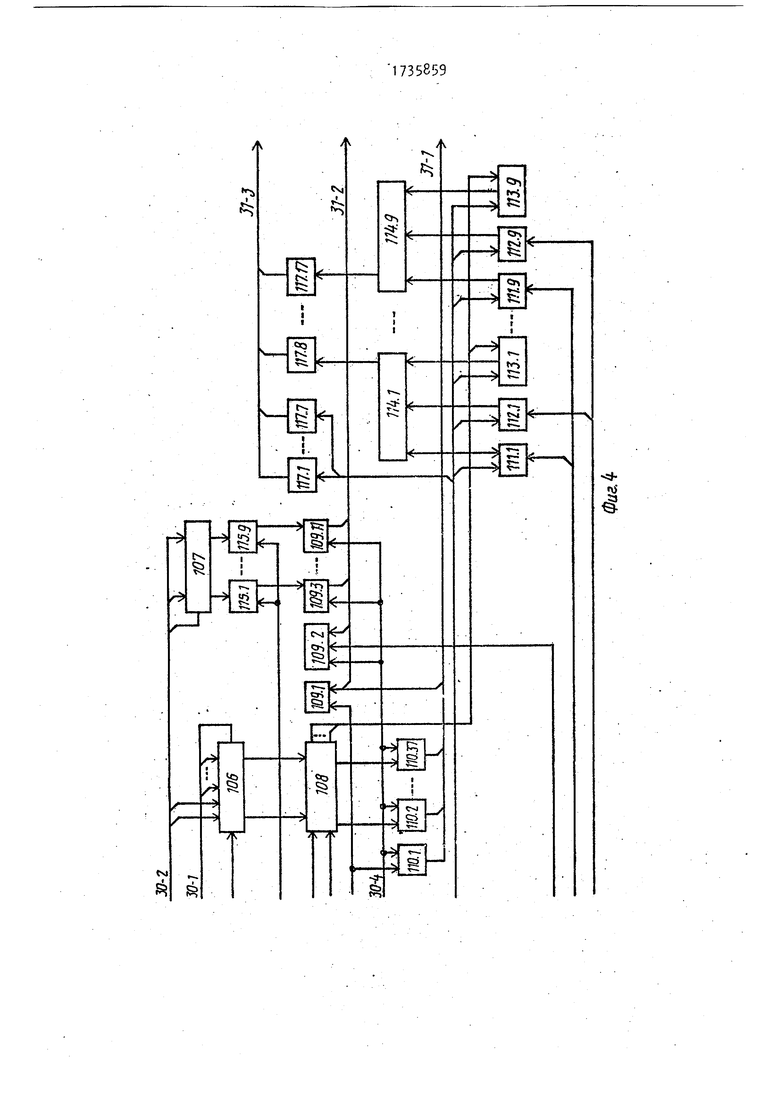

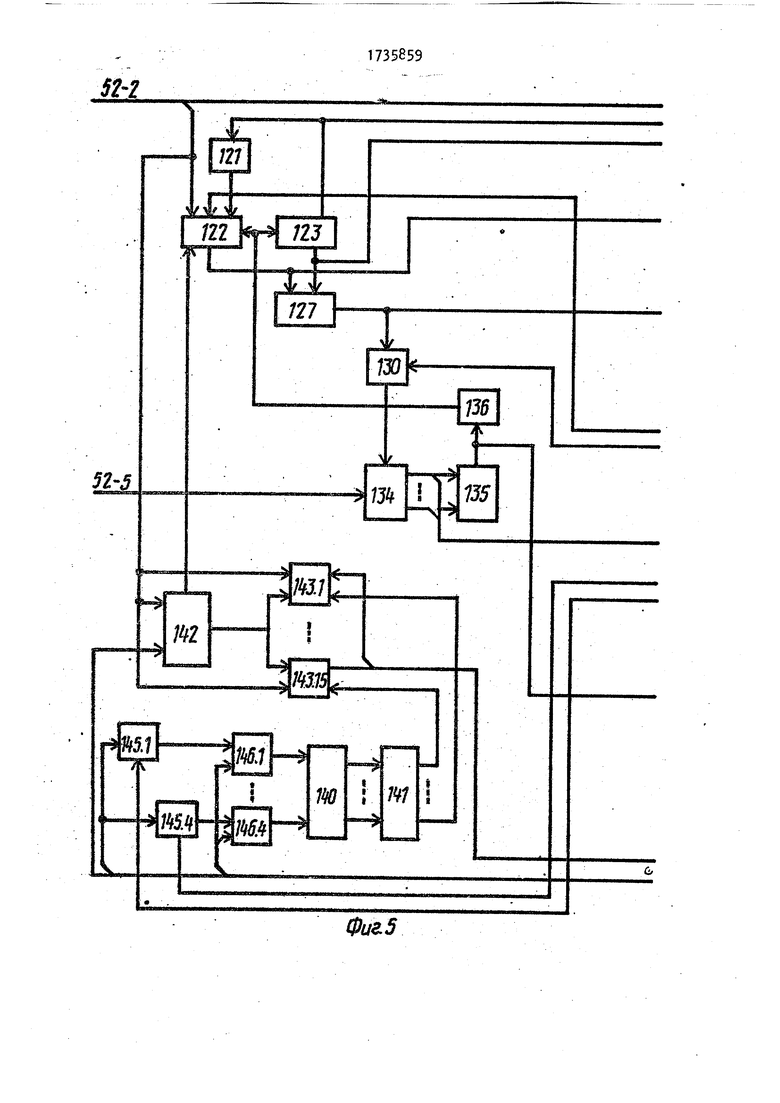

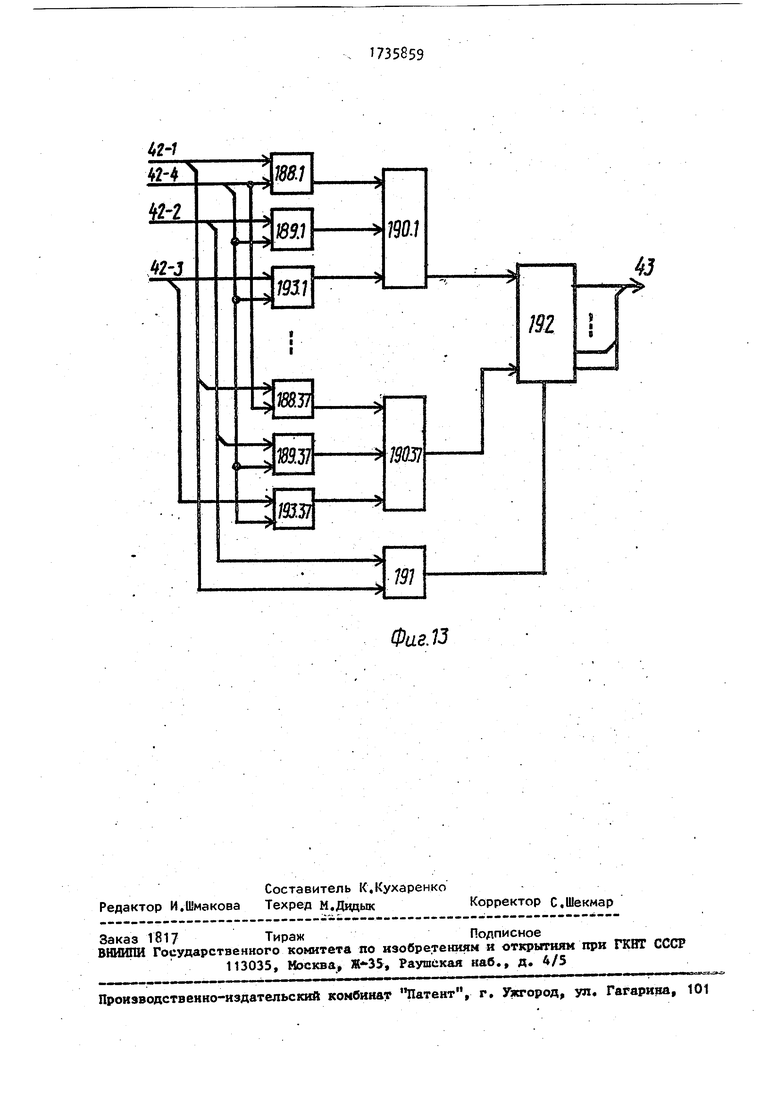

На фиг.1 и 2 представлена блок- схема устройства для управления вводом-выводом; на фиг.З и 4 - блок- схема блока синхронизации обмена; на фиг,5 и 6 - блок-схема блока управления; на фиг.7 - блок-схема первого блока приоритета; на фиг.8 - блок связи с памятью; на фиг.9 - блок управления каналами; на фиг.10 - блок памяти; на фиг.11 - узел модификации; на фиг.12 - узел запуска каналов, на фиг.13 - регистр ввода.

Устройство для управления вводом- выводом (фиг.1 и 2) содержит блоки 1.1 - 1,т синхронизации обмена, блок 2 памяти, исполнительный регистр 3, узел 4 модификации, регистр 5 ввода, первый 6ло,к 6 приоритета, первый 7 и второй 8 буферные регистры, узел 9 запуска каналов, блок 10 управления, блок 11 связи с памятью, коммутатор 12 памяти, второй блок 13 приоритета и селекторные каналы 14,1 - 14.п.

Каждый селекторный канал 1 содержит дополнительный блок 15 синхронизации обмена, блок 16 управления каналом, счетчик 17 адреса, счетчик 18 количества байтов и буферный усилитель 19.

В устройстве имеются: входные интерфейсные шины 20-1 - 20-т, входная шина 21 данных, входная шина 22 стро- ба, входная шина 23 команды, входные интерфейсные шины 24-1 - 24тп селекторных каналов, выходные интерфейсные шины 25-1 - 25-т, выходная шина 26 адреса данных, выходная шина 27 запросов в оперативную память, выходная шина 28 запросов в центральный процессор, выходные интерфейсные шины 29-1 - 29-п селекторных каналов.

Блок 1.1 синхронизации обмена имеет входы: информационный 30-1, интерфейсный 30-2, управляющий ЗО&З, подтверждения 30-4 и выходы: информационный 31-1, управляющий 31-2, интерфейсный 31-3.

Блок 1.2 синхронизации обмена име ет входы: информационный 32-1, интерфейсный 32-2, управляющий 32-3 подтверждения 32-4 и выходы: информационный , управляющий , и терфейсный .

Блок 1 .tn синхронизации обмена имеет входы: информационный 34-1, интерфейсный 34-2,. управляющий 34-3, подтверждения 34-4 и выходы: информационный 35-1, управляющий 35-2, интерфейсный .

Блок 2 памяти имеет входы: первый, второй и третий информационные 36-1 - 36-3, адресный 36-4, управляющий 36-5 и информационный выход 37.

Исполнительный регистр 3 имеет первый и второй информационные входы 38-1 и 38-2 и выход 39.

Узел 4 модификации имеет входы: первый и второй информационные 40-1 и 40-2 и модификации 40-3 и выход 4

Регистр 5 ввода имеет входы: информационный 42-1, первый и второй командные 42-2 и 42-3, .управляющий 42-4 и выход 43.

Первый блок 6 приоритета имеет первый 44-1 и второй 44-2 входы запроса и выход 45.

Первый буферный регистр 7 имеет информационный вход 46 и информационный выход 47.

Второй буферный регистр 8 имеет адресГный 48-1 и информационный 48-2 входы и выходы 49-1 и 49-2..

Узел 9 запуска каналов имеет установочный вход 50 и управляющий выход 51.

Блок 10 управления имеет входы: первый 52-1 и второй 52-2 информационные, командный 52-3, состояния 52-4, стробирования 52-5, установочный 52-6, подтверждения 52-7 и выходы: управляющий 53-1, запроса 53-2, командир-запросный 53-3, установочный 53-4.

Блок 11 связи с памятью имеет входы: информационный 54-1, запроса 54-2 и выходы: информационный 55-1, запроса

Коммутатор 12 памяти имеет входы первый адресный 56-1, первый и второй информационные 56-2 и 56-3, второй адресный 56-4, установочный 56-5 и выход 57.

Второй блок 13 приоритета имеет первый 58-1 и второй 58-2 входы запроса и выход 59 подтверждения.

Селекторные каналы 14,1 - 14 «п. имеют входы: командные 60-1 - бОгп первые подтверждения 61-1 - 61-п ин

735859 °

формационные 62-1 - 62-п, управляю--;, , щие 63-1 - 63-п, интерфейсные 64-1 - 64-п стробирующие 65-1 65-п, вторые подтверждения 66-1 - 66-п и выходы: информационные с запросом 67-1 - 67-ti, адресные 68-1 - 68-п, запросов 69-1 - 69-п, состояний 70-1 - 70-п,интерфейсные j0 71-п, информационные 72-1 - 72-п.

Дополнительный блок 15 синхронизации имеет входы: информационный 73-1f интерфейсный 73-2 управляющий 73тЗ, подтверждения 73-4 и выходы: информационный 74-1, управляющий 74-2, интерфейсный 74-3.

Блок 16 развязки имеет входы: . информационный 75-1 управляющий 75-2, первый 75-3 и второй 75-4 под- 20 тве рждения, выходы: состояния 76-1 информационный с запросом 76-2, информационный 76-3, запроса 76-4, сдвига 76-5,подтверждения .

Счетчик 17 адреса имеет информа- 25 ционный , управляющий 77-2 и сдвиговый входы.

Счетчик 18 количества байтов имеет информационный 78-1, управляю щий 78-2, сдвиговый 78-3 входы и выход 79.

30 Буферный усилитель 19 имеет входы: адресный 80-1, подтверждения 80-2 и выход 81.

В состав блока 1.1 синхронизации обмена (фиг. 3 и 4) входят счетчик 35 82 байтов, элементы ИЛИ 83, 88, 91Л 114 и 115, элементы И 85-87, 90, 94, 97-99, 101 и 111 -113, триггер 84 наличия информации на регистре приема, триггер 69 запроса, -триггер 4Q 92 наличия информации на регистре выдачи, элементы НЈ 93 и 100, триггер 96 информации от канала, регистр 102 кода операции, регистр 103 номера внешнего устройства, схе- 45 ма 104 сравнения номеров внешних устройств, формирователь 105 сигналов управления интерфейсом, регистр 106 приема, регистр 107 байта состояния, регистр 108 выдачи, бу- 50 Ферные усилители 109.1 - 109.11 и 110.J - 110.37, триггеры 116.1 - 116.7 и усилители 117.7 - 117.17.

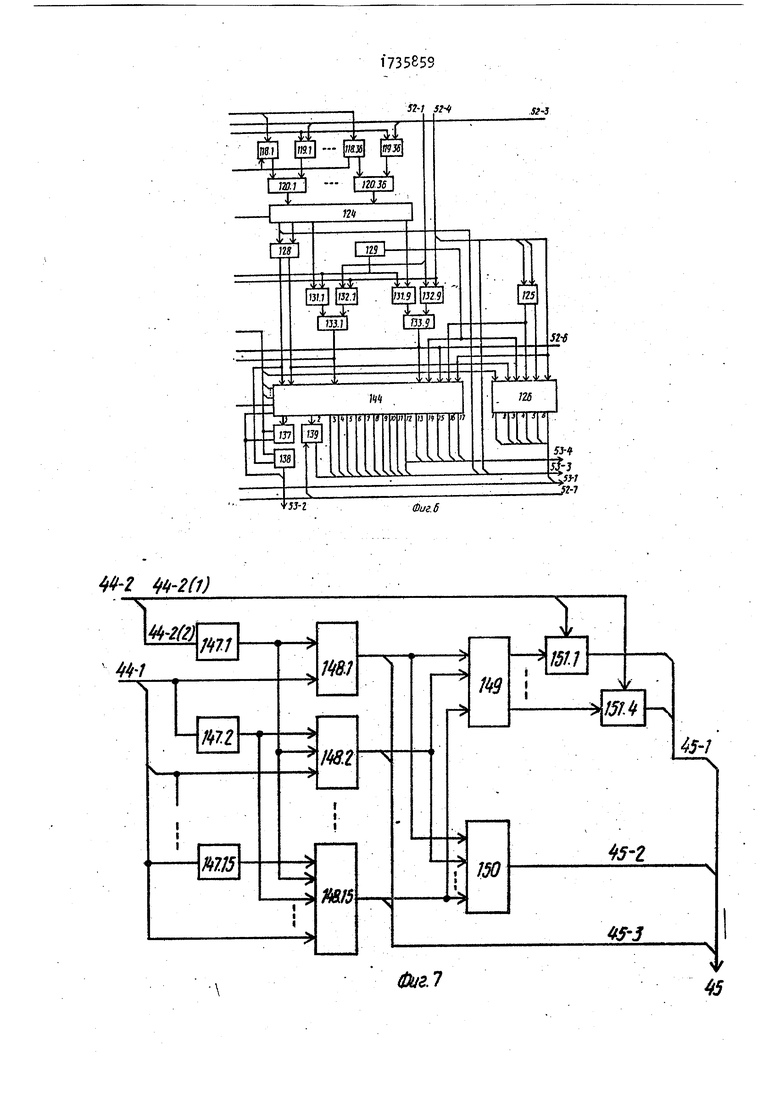

В состав блока 10 управления (фиг, 5 и 6) входят элементы И 118.1 55 118.36, 119.1 - 119.36, 122, 123, 131.1 - 131.9, 132.1 - 132.9, -143.1 I 143.15, 145.1 - 145.15, элементы ИЛИ 120.1- 120.36, 127, 130, Ш.1 133.9, 135 и .1 - ., элемен- ты НЕ 121, 129 и 136, регистр 12 команд, дешифратор 125 байта состояния, формирователь 126 сигналов управления блоком синхронизации обмена, дешифратор 128 кода операции, генератор 13 тактовых импульсов, триггер 137 прерывания, триггер 138 ответа в центральный процессор, тригер 133 запроса во второй блок приоритета, буферный регистр номера канала, дешифратор номера канала, триггер занятости буферного регистра номера канала и формирователь 1 управляющих сигналов

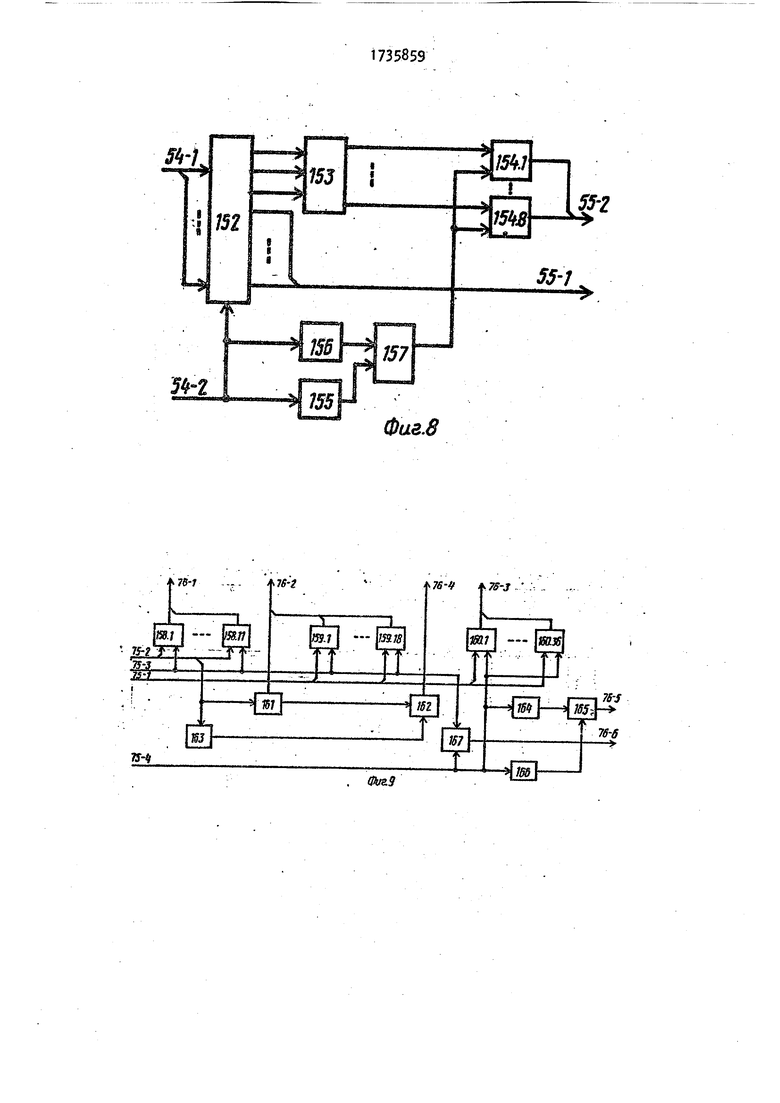

В состав первого блока 6 приоритета (фиг. 7) входят элементы НЕ .1 - .15, элементы И 148.1 - .15, элементы ИЛИ 150 и 151.1 - 151.4 и шифратор номера канала.

В состав блока 11 связи с память (фиг,8) входят выходной регистр 152 дешифратор 153 номера куба памяти, элементы И 15.1 - 15.8 и 157, D- триггер 155 и элементы НЕ 156.

В состав блока 16 развязки (фиг. входят буферные усилители 158.1 - 158,11, 159.1 - 159.16 и 160.1 - 160.36, элементы И 161, 162 и 1б5, элементы НЕ 163 и 16, элементы ИЛИ 1б7 и D-триггер 166.

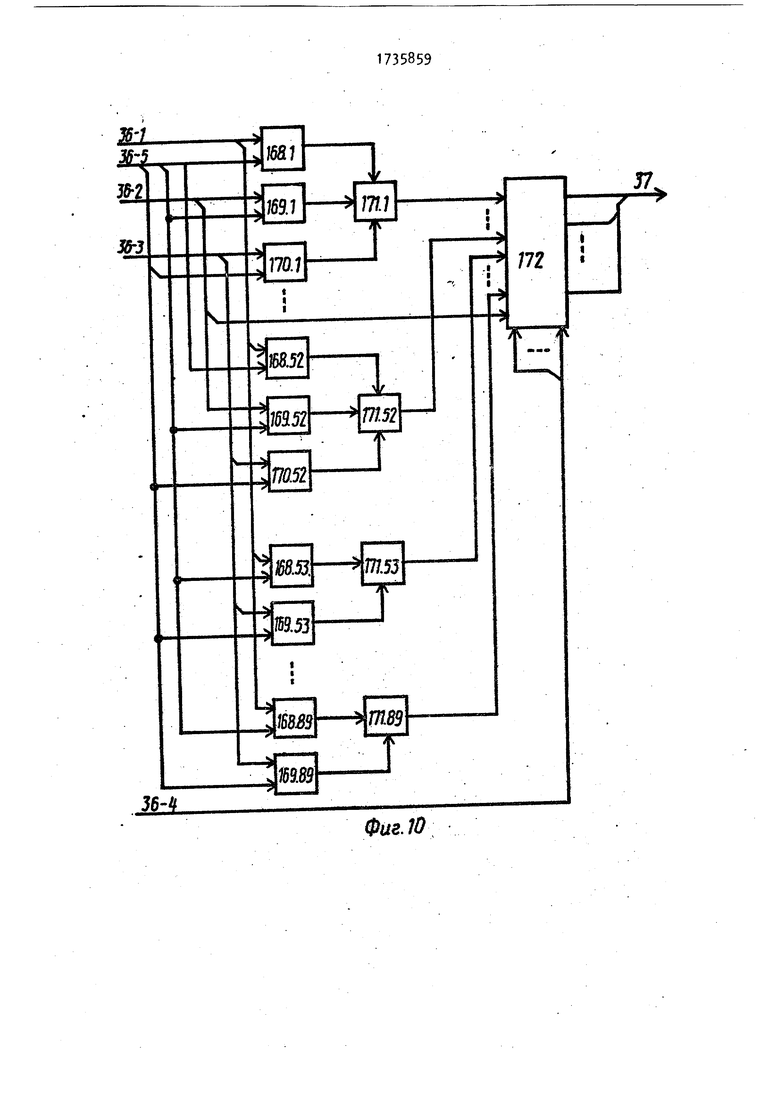

В состав блока 2 памяти (фиг.10) входят элементы И 168.1 - 168.89, 169,1 - 169.89 и 170.1 - 170.52, элементы ИЛИ 171.1 171.89 и память 172,

В состав узла модификации (фиг, 11)- входят элементы И 173.1 - 173.20, 17.1 - 17.20, 175.1 - 175.20 и 176.1 - 176.20, элементы ИЛИ 177J - 177.20 и 178, элементы НЕ 179 и сумматор 1бО.

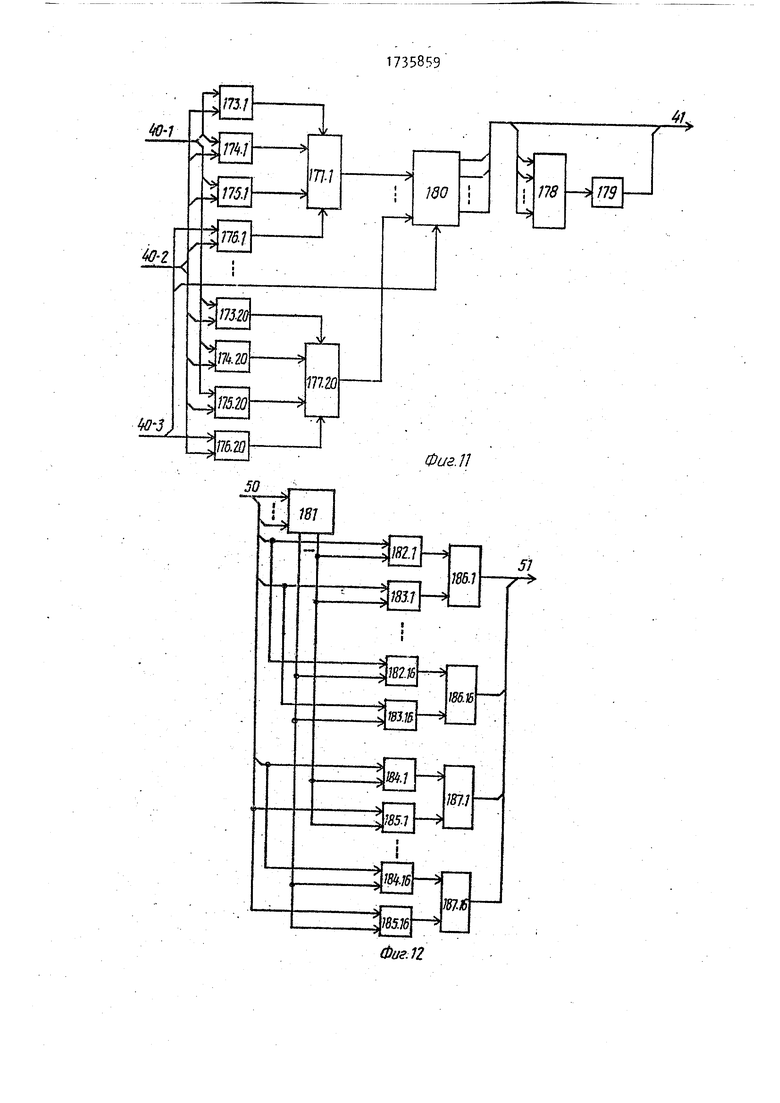

В состав узла 9 запуска канала (фиг, 12) входят дешифратор 181 номера канала, элементы И 182.1 - 182.16, 183.1 - 183.16, 18.1 - 184,16 и 1&5.1 - 185.16, триггеры 186,1 - 186.16 работы и триггеры 187.1 - 187.16 прерывания.

В состав регистра 5 ввода (фиг.1 входят элементы И 188,1 - 188.37, 189.1 - 189.37 и 193.1 - 193.37, элементы ИЛИ 190.1 - 190.37 и 191 и регистр 192.

Устройство для управления вводом выводом (УУВВ) обеспечивает обмен информацией между внешними устройствами (ВУ) и оперативной памятью

0

5

0

5

вычислительной машины параллельно с работой центрального процессора,

В состав вычислительной машины ц входят, например, центральный процессор (ЦП), оперативная память, центральный генератор синхронизации, устройство для управления вводом- выводом.

Устройство для управления вводом- выводом состоит из каналов, позволяющих одновременно выполнять обмен с различным ВУ. К каналам подключаются внешние устройства, имеющие стандартный интерфейс и работающие в монопольном режиме.

Предлагаемое устройство является групповым,- его оборудование используется несколькими каналами в разделении времени. Блоки синхронизации обмена являются индивидуальными для каждого канала.

Система команд устройства включает команды трех типов. Команды первого типа поступают из ЦП и служат для запуска канала на выполнение программы - команда Рдрес программы или для опроса состояния канала - команда Состояние канала. Команды второго и третьего типов считываются в устройство самостоятельно независимо от работы центрального процессора. Команды второго типа предназначены для управления работой каналов. Гни позволяют начать и остановить работу каналов, провести контроль и выполнить переходы в канале. Команды третьего типа предназначены для управления работой ВУ и указывают, какую операцию ввода-вывода надо выполнить.

Работа устройства по обмену информацией начинается с посылки центральным процессором в устройство команды Адрес программы, указывающей адрес команды второго типа в 5 оперативной памяти. По этому адресу в устройство считывается команда второго типа Начать обмен, в которой указан номер запускаемого кана- ла и устройства в канале. Затем считывается команда третьего типа, указывающая код операции, выполняемой внешним устройством, адрес массива обмена и его размер. После оконча- . ния операции обмена считывается ко- манда второго типа Остановить обмен, после выполнения которой дальнейшее считывание команд из оперативной памяти прекращается. О резуль0

5

0

0

тате выполнения обмена можно судить по слову состояния канала, записываемому в фиксированные ячейки оперативной памяти после завершения обмена. Слово состояния записывается при наличии в команде указателя о необходимости такой записи или при возникновении аварийной ситуации в канале, например при несовпадении номеров устройств в начальной выборке.

В качестве примера реализации рассмотрим устройство для управления вводом-выводом, содержащее 16 каналов. Четыре канала являются выделенными селекторными, остальные каналы реализуют монопольный режим работы.

Работа устройства состоит в выполнении процедур запуска каналов и далнейшего обмена данными,

При запуске канала выполняется последовательность команд первого, второго и третьего типов. Обмен данными выполняется по командам третьего типа.

Команды первого типа поступают в устройство из центрального процессора.

Через входную шину 23 команда, сопровождаемая сигналом записи, поступает в блок 10 управления на командный вход 52-3 на входной коммутатор, образованный элементами И 118,1- - 118.36, 119.1 - 119.36 и ИЛИ 120.1 - 120.36.

С выхода коммутатора команда поступает на регистр 124.

Сигнал записи поступает на схему приоритета, образованную элементами И 122, 123, НЕ 121 и ИЛИ 127. Схема приоритета предназначена для выборки одного запросчика при одновременном поступлении команд из ЦП и из первого буферного регистра 7, причем процессор имеет более высокий приоритет. Для предотвращения приема команды в блок управления, занятый отработкой текущей команды или запроса блока синхронизации обмена, сигнал записи через элемент НЕ 121 блокирует на элементе И 122 запрос первого буферного регистра 7. Прием команды в работающий блок 10 запрещается сигналом с выхода генератора 13 тактовых импульсов через элементы ИЛИ 135 и НЕ 136, Этот же сигнал блокирует схему приоритета. Генератор 13 тактовых импульсов представляет собой синхронный сдвиговый рет

o

0

5

гистр разрядности К, Сдвиг проиа во- дится каждый такт синхронизации. Импульсы синхронизации поступают в блок 10 управления от центрального генератора синхронизации вычислительной машины через входную шину 22 строба на вход 52-5 блока 10. Тактовые импульсы с выхода генератора 13 поступают на формирователи 126 и 144 и на входы сброса триггеров 137 и 138, Пока генератор 13 вырабатывает тактовые импульсы, на выходе элемента ИЛИ 135- поддерживается высокий уро, венГь сигнала, означающий, что блок 10 занят отработкой запроса. Пуск генератора 134 выполняется при каждом обращении к блоку 10 с выходов элементов И 122 и 123 через элементы ИЛИ 127 и 130, На второй вход элемен та ИЛИ 130 поступает запрос от блока 1.1 синхронизации обмена через вход 52-4 состояния блока 10, Одновременно с пуском генератора 134 сигналом с элемента ИЛИ 127 производится прием команды на регистр 124 через группу элементов И 119.1 - 119.36, открытых сигналом с выхода элемен- . та И 123, и элементы ИЛИ 120,1 - 120.36.

С регистра 12 команда поступает на дешифратор 128, выходы которого связаны с входами формирователя 144. Формирователь 144 представляет собой схему, выполненную на элементах И, ИЛИ, НЕ.

На формирователь 144 поступают . дешифрированный код команды с дешифратора 128, управляющие признаки и номер канала с регистра 124 команд

0 или с первого информационного входа 52-1 через элементы И 131.1 - 131.9, 132.1 - 132.9 и ИЛИ 133.1 - 133.9, тактовые импульсы с генератора 134, признак занятости с

5 элемента ИЛИ 135, признак прерывания с выхода триггера 137, признак состояния и запрос от блока синхронизации обмена с входа 52-4 блока 10, дешифрированный аварийный байт

0 состояния с дешифратора 125.

Иа этих входных сигналов на формирователе 144 вырабатываются сигналы установки и сброса триггеров работы и прерывания в узле 9 запуска , сигналы управления приемом в регистры ввода 5 и исполнительный 3, сигналы управления входными коммутаторами в узле 4 модификации и бло

0

5

5

15

ке 2 памяти, а также инкремент для узла 4 и номер канала для блока 2 памяти.

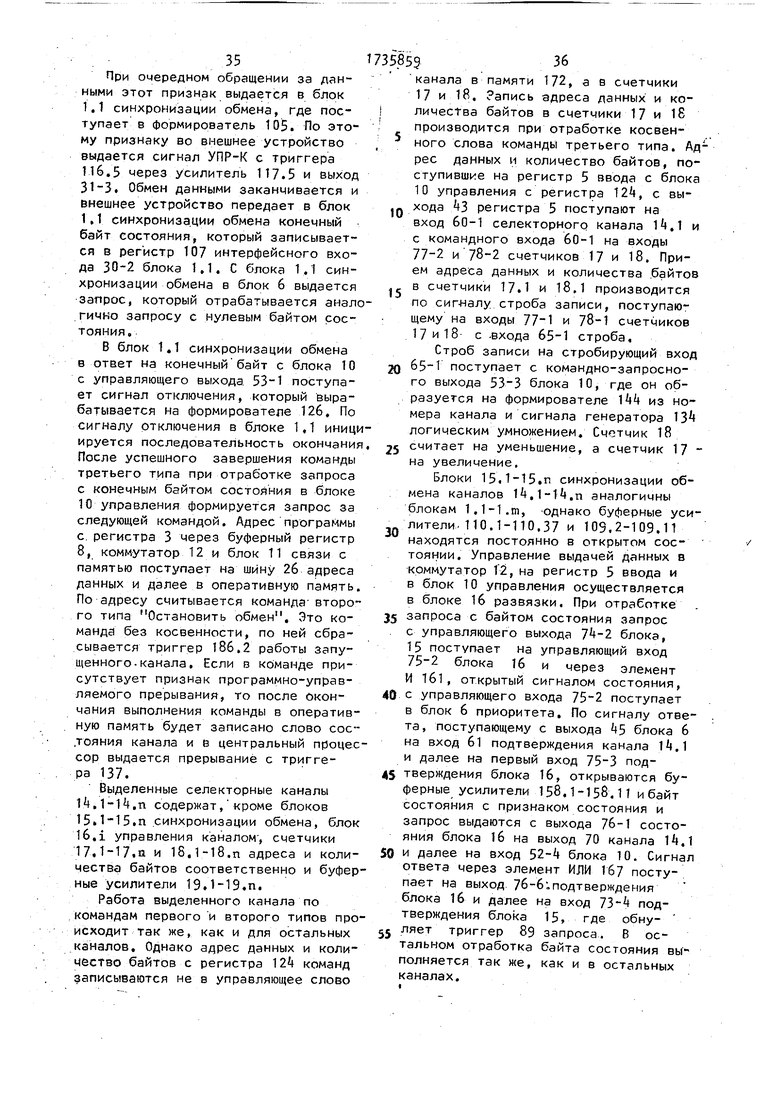

В табл. 1 представлена таблица истинности для формирователя 144.

На входах формирователя вырабатываются сигналы 1-4 - сигналы генератора , 5 сигнал с элемента ИЛИ 135; 6 - сигнал с триггера 137 прерывгжия, - сигналы с дешифратора 128 о дешифрации кода, 7 - команда первого типа; 8 - команда второго типа; 9 команда третьего типа; 10 - команда Адрес программы ; 11 - команда Начать обмен,

12- команда Остановить обмен);

13 номер канала, 14 - признак цепочки команд; 15 - сигнал с выхода дешифратора 125 о поступлении байта состояния с кодом FF16; 16 - запрос БСО; 17 сигналы с триггеров работы и прерывания канала из узла 3, 18 - признак состояния из БСО.

На выходах формирователя 144 вырабатываются сигналы: 1 и 2 - установка триггеров 137 и 138; сигналы управления приемов в узел 4 модификации ад реса программы с регистра 5, адреса программы, адреса данных и количества байтов с регистра 3; 7 - инкремент; 8 и 9 стробы записи в регистры 3 и 5, Ю-12 - сигналы управления приемом в блок 2 памяти из исполнительного регистра 3 узла 4 модификации и регистра 5 ввода; 13 номер канала для блока 2 памяти; 14 и 15 сигналы установки триггеров 186.1 и 187.1, 16 и 17 сигналы сброса триггеров 186,1 и 187.1.

17

Каждый сигнал формируется в определенный момент времени, задаваемый тактовыми сигналами с выхода генератора 134. Отработка временной диаграммы любой команды занимает постоянное число тактов.

Формирователь 126 построен аналогично формирователю 144 и представляет собой комбинационную схему. На входы формирователя 126 поступают сигнал запроса блока синхронизации обмена с входа 52-4 блока 10, сигналы с генератора 134, признаки дешифрации команд второго и третьего типов с дешифратора 128, признаки дешифрации нулевого, сбойного, конечного и аварийного байтов состояния

s

, 73585916

и признак состояния с входа 52-4 блока 10.

На формирователе 126 вырабатываются стробы записи номера внешнего устройства, кода операции и запуска блоков синхронизации обмена, признаки продолжения команды третьего типа и отключения, а также

JQ строб записи кода в блоки синхронизации обмена, которые поступают на управляющий выход блока 10 управления.

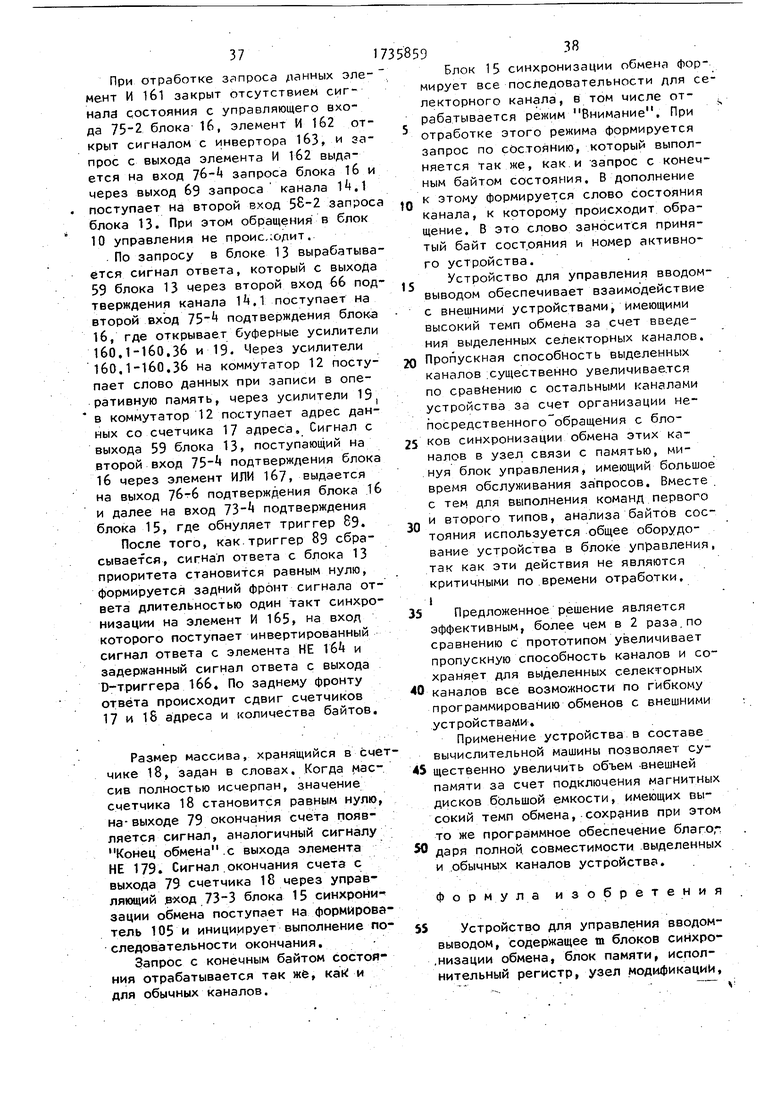

В табл. 2 представлена таблица

jc истинности формирователя 126.

Одновременно с взведением триггера 138 на вход 50 узла 9 запуска каналов поступают нулевой номер канала и сигнал установки с выхода

20 формирователя 144. Нулевой номер канала поступает на вход формирователя 144 с регистра 124 через элементы И 131.1-131.9, открытые сигналом с инвертора НЕ 129, и эле25 менты ИЛИ 133.1-133.9. Сигнал установки образуется логическим умножением сигналов с генератора 134 и дешифратора 128 в формирователе 144, В узле 9 запуска каналов нулевой номер канала поступает на дешифратор

30 181.

Сигнал с выхода дешифратора 181 и сигнал установки с входа 50 узла

9логически умножаются на элементе

И 182,1 и устанавливают в единичное .

35 состояние триггер 186,1 работы нулевого канала. Команды первого типа всегда выполняются в нулевом канале. Сигнал с выхода триггера 186.1 работы нулевого канала поступает на вы40 ход 51 узла 9 запуска каналов и через установочный вход 52-6 блока

10управления поступает на вход формирователя 144.

Адрес программы с регистра ко- 45 манд через командно-запросный выход блока 10 управления поступает на управляющий вход 42-4 регистра 5 ввода, В регистре 5 ввода адрес поступает на элементы И 189.1-189.37, 50 открытые сигналом с выхода 45 блока 6, и через элементы ИЛИ 190.1- 190,37 записывается в регистр 192 по сигналу записи, поступающему с выхода элемента ИЛИ 91. На элемент 55 ИЛИ 91 сигнал записи поступает с пер-( вого командного входа 42-2 регистра 5. На первый командный вход 42-2 регистра 5 сигнал записи поступает с командно-запросного выхода бло171

ка 10, в котором он вырабатывается на формирователе 144 логическим ум- ножением сигнала с выхода генератора 13, кода операции Адрес програ мы и сигнала работы нулевого канала (из узла 9).

На первый командный вход 44-2 блка 6 поступает сигнал с командно-запросного выхода 53-3 блока 10, в ко тором он формируется на элементе ИЛИ 135.

Если сигнал равен единице, т.е. блок 10 занят отработкой команды, то запросы блоков 1.1-1.т и кана- лов 14.1-14.п, поступающие через второй вход 44-2 первого блока 6 приоритета на элементы И 148.1- 148.15. блокируются низким уровнем сигнала с выхода элемента НЕ 147.1. В этом случае на регистр 192 может поступить только команда с блока 10 управления с командно-запросного выхода на первый командный вход 42-2 регистра 5 и элементы И 189.1- 189.37 открытые сигналом с выхода 45.

Адрес программы с выхода 43 регистра 5 ввода поступает на информационный вход 48-2 буферного регисра 8 и на второй информационный вход 40-2 узла 4 модификации.

Буферный регистр 8 организован по принципу первый пришел - первый вышел и имеет глубину буферизации, равную четырем. Разрядность буфер- ного регистра равна 60. На буферный регистр 8 адрес поступает с исполнительного регистра 3 на адресный вход 48-1 буферного регистра 8 или с регистра 5 ввода на информацион- ный вход 48-2 буферного регистра 8.

С регистра 5 ввода на информационный вход 48-2 буферно го регистра 8 поступают также и данные, если они были записаны в регистр 5 ввода с блока 1Д синхронизации обмена.

Для того, чтобы отличить адрес, поступающий в буферный регистр 8t от данных, адрес сопровождается специальным признаком адреса. По признаку адрес программы записывается в нужное поле буферного регистра 8. С адресного выхода 49-1 буферного регистра 8 адрес попадает на первый- адресный вход коммутатора 12 и с выхода 57 коммутатора 12 поступает на

0

5 0

5

0

18

информационный вход 54-1 блока 11 связи с памятью.

Коммутатор 12 имеет две группы информационных и две группы адресных входов и вход 56-5 управления. Коммутатор выполнен на двухвходовых элементах И, ИЛИ и пропускает на выход 57 адрес и данные с одной из двух групп входов адреса и данных 56-1, 56-2 или 56-3, 56-4, Управление коммутатором осуществляется сигналом с выхода 59 подтверждения блока .13 приоритета. Блок 13 приоритета аналогичен блоку 6 приоритета. Отличие состоит в том, что запрос блока 10, поступающий на первый запросный вход 58-1 блока 13 с командно-запросного выхода блока 10 управления, имеет не высший, а низший приоритет и обслуживается при отсутствии запросов от выделенных селекторных каналов. В блоке 10 управления запрос выдается с триггера 139 запроса, который взводится по сигналу с формирователя 144. Этот сигнал образуется так же, как и признак адреса, но с задержкой на такт работы генератора 134.

Триггер 139 запроса сбрасывается по сигналу с выхода 59 блока 13 приоритета, поступающему на вход 52-7 подтверждения блока 10, Одновременно на генераторе 134 образуется нулевой код, так как выданы все тактовые сигналы. На выходе элемента ИЛИ 135 сигнал становится равным нулю и отработка, команды первого типа в блоке 10 заканчивается.

Сигнал с выхода 59 блока 13 приоритета поступает на вход 54-2 запро

са блока 11, на первый информационный вход 54-1 которого поступает адрес программы с выхода 57 коммутатора 12. По сигналу с входа 54-2 запроса блока 11 производится запись адреса

с информационного входа 54-1 блока 11 в регистр 152. Старшие три разряда

адреса регистра поступают в дешифратор 153 номера куба памяти. Младшие

разряды адреса с регистра 152 поступают непосредственно на информационный выход блока 11 и с него на шину 26 адреса данных, выходную. После дешифрации номер куба памяти поступает на первые входы группы элементов И 154.1-154,8, на вторые входы которых поступает сигнал с вы г. хода элемента И 157. Этот .сигнал представляет собой задний фронт сигn

нала разрешения,который имеет дли- л тельность один такт и формируется на схеме, состоящей из В-триггера 155 и элементов НЕ 156 и И 157. По сигналу с выхода элемента И 157 отИ 154.1крывается один из элементов

154.8 и на выход устройства выдается

запрос в нужный куб памяти.

Адрес программы с выхода 43 регистра 5 ввода через второй вход узля 4 модификации попадает на группу элементов И 17б.1-176.20, открытых сигналом разрешения записи адреса, поступающим на третий вход узла 4 с командно-запросного выхода 53-3 блока 10.

С выходов элементов И 176.1- 176.20 через элементы ИЛИ 177.1- 177.20 адрес поступает на первый вхо сумматора 180. На второй вход сумматора 180 поступает мисло с блока 10 управления, на которое необходимо увеличить адрес (инкремент). Сигнал разрешения записи адреса и инкремент выдаются на командно-запросный выход блока 10 управления с формирователя 144, где они вырабатываются аналогично признаку адреса. Сигнал разрешения записи адреса поступает на элементы И 168.1-168,20 и разрешает прием инкрементированного адрес программы в память через элементы ИЛИ 171.1-171.20 в поле адреса программы управляющего слова 0-го канала ,

Каждому каналу в памяти соответствует управляющее слово канала (УСК), имеющее следующие поля: поле адреса программы - 20 разрядов, поле адреса данных - 20 разрядов, поле размера массива (количества байтов) - 12 разрядов, поле управляющих признаков - 5 разрядов, поле номера устройства - 9 разрядов поле код операции - 9 разрядов, поле байта состояния - 9 разрядов, поле номера канала - 4 разряда.

Информация с выхода 43 регистра 5 ввода поступает на третий информационный вход 36-3 блока 2 и записывается в память 172 через элементы И 170,1-170.52 и ИЛИ 171,1-171.89 Информация с выхода 39 регистра 3 поступает на первый вход 36-1 блока 2 и записывается в память 172 через элементы И I68.1-i68.8g и ИЛИ 171,1-171.89, Модифицированный адрес с выхода kl узла 4 поступает на вто1

д а

. to

73585920

рой информационный вход 36-2 блока 2 и записывается в память 172 через элементы И 169.1-169.5,2 и ИЛИ 171.1- 171.52. апись в память 172 осуществляется по номеру канала, поступающему на адресный вход 36-4 блока 2 с выхода 45 блока 6,

В блоке 6 приоритета номер канала выдается с выходов элементов ИЛИ 151.1-151.4. На входы элементов ИЛИ 151,1-151.4 номер канала поступает с входа 44-2 запроса (вход 44-2(1) на фиг.4) блока 6, на который он поступает с командно-запросного выхода блока 10, где хранится в регистре 124.

При отработке запроса блока 1,i синхронизации обмена позиционный

2Q номер блока 1.1 синхронизации с выходов элементов И 148.1-148.15 на . шифраторе 149 преобразуется в двоичный номер канала и через элементы ИЛИ 151.1-151.4 поступает на выход

25 45 блока 6 приоритета (выход 45-1

15

30

на фиг,7).

По адресу программы, выданному в оперативную память с информационного выхода блока 11 связи с памятью по выходной шине 26 адреса данных, в устройство по шине 21 на информационный вход 46 буферного регистра 7 поступает команда второго типа. С выхода 47 буферного регистра 7 команда поступает на второй ин-

35 формационный вход 52-2 блока 10 управления. Буферный регистр 7 построен аналогично буферному регистру 8, но глубина буферизации равна двум. С второго информационного входа 52-2

40 блока 10 управления команда через элементы И 118.1-118.36 и ИЛИ 120.1- 120,36 поступает на регистр 124 команд. Команда сопровождается сигналом запроса, который с второго ин45 формационного входа 52-2 блока 10 открывает через элемент И 122 группу элементов И 118.1-118.36. Сигнал с выхода элемента И 122 через элемент ИЛИ 127 стробирует прием коман50 ды в регистр 124 и через элемент ИЛИ 130 запускает генератор 134 тактовых импульсов. С регистра 124 код операции поступает на дешифратор 128.

Разряды команды, содержащие управ ляющие признаки, с выхода регистра команд через элементы И 131.1-131.9, открытые сигналом с инвертора 129, указывающим на отсутствие запроса

21

блока 1.1 синхронизации обмена, и элементы ИЛИ 133.1-133.9 поступают на формирователь 144 для выбора сигналов управления блоком 2 памяти, регистром 3 и узлом 4 модификации.

Лешифрирова-нная команда Начать обмен может быть с косвенностью и без косвенности. Если дешифрируется команда, отличная от Начать обмен, то возникает сигнал программной ошибки в формирователе 144. Если дешифрирована команда без косвенности, то обращение за следующей командой выполняется по адресу, хранящемуся в управляющем слове нулевого канала. По сигналу с триггера 186,1 работы, поступающему с управляющего выхода 5 узла 9 на установочный вход 52-6 блока 10, в формирователе 144 формируется нулевой номер канала и через командно-запросный выход блока 10 выдается на второй запросный вход 44-2 блока 6 приоритета.

Далее через элементы ИЛИ 151.1 151.4 номер канала поступает на выход 45 блока 6 приоритета и на адресный вход 36-4 блока 2.

По кулевому номеру канала из памяти 172 считывается управляющее слово канала, с выхода 37 поступает на первый информационный вход 38-1 регистра 3 и записывается в регистр 3 по стробу записи. Строб записи поступает на второй информационный вход 38-2 регистра 3 с командно-запросного выхода блока 10 управления, где вырабатывается на формирователе 144 как логическое произведение сигналов с дешифратора 128 и генератора 134. С выхода 39 регистра 3 адрес поступает на адресный вход 48-1 буферного регистра 8 и с адресного выхода буферного регистра 8 на первый адресный вход 56-1 коммутатора 12,

Одновременно с выдачей адреса с регистра 3 в буферный регистр 8 в блоке 10 управления номер канала с выхода формирователя 144 поступает на установочный выход 53-4 блока 10 управления и с него на установочный вход 50 узла 9 заяуска каналов. С установочного входа 50 узла 9 запуска каналов номер канала поступает на вход дешифратора 181 номера канала и на его выходе появляется сигнал, открывающий элемент И l8l,i, на другой вход которого поступает

10

15

20

735859 22

сигнал установки триггера работы с входа 50 узла 9. На вход 50 этот сигнал поступает с установочного выхода 53-4 блока 10 управления,где вырабатывается на формирователе 144 так же, как и строб записи в регистр 3, но по следующему такту гене ратора 134. По сигналу с выхода элемента И 182 Л устанавливается триггер 186,1 работы запускаемого канала. Сигнал с выхода триггера 186.1 работы поступает на управляющий выход 51 узла 9 и через установочный вход 52-6 блока 10 заводится на формирователь 144. Номер запущенного канала с выхода формирователя 144, где он образуется логическим умножением номера канала с регистра 124 и сигнала работы с триггера 186,1, выдается на командно-запросный выход блика 10. С выхода номер канала поступает на второй запросный вход 44-2 блока 6 приоритета. 25 Номер канала с второго запросного входа 44-2 через элементы ИЛИ 151.1 151.4 поступает на выход 45 (45-1) блока 6 приоритета и далее на адрес-, ный вход 36-4 блока 2 памяти. Адрес с исполнительного регистра через элементы И 174.1-174.20, открытые по вторым входам сигналом разрешения записи адреса, и через элементы ИЛИ 177.Ы77.20 поступает на вход сумматора 180 и инкрементирует- . 35 ся. Сигнал разрешения записи адреса и инкремент вырабатываются так же, как и при выполнении команды первого типа.

Инкрементированный адрес с выхо- 40 да 41 узла 4 поступает на второй информационный вход 36-2 блока 2 памяти и с него через элементы И 1б9.1 169,20 и ИЛИ 171.1-171.20 на вход памяти 172 и записывается а поле ад- 45 реса программы управляющего слова за пускаемого канала, так как на адресном входе 36-4 блока 2 установлен номер канала.

Номер устройства и номер канала . 50 с регистра 124 поступают на командно-запросный выход 53-3 блока 10, с которого заводятся на ЁТОРОЙ запросный вход 44-2 блока бис выхода 45 блока 6 на адресный вход 36-4 55 блока 2. Сигнал разрешения записи номера устройства с выхода формирователя 144 поступает на третий выход 53-3 блока 10 и с него на управляю+ - - -.

30

23

щи и вход блока 2. С третьего информационного входа Зб-З блока 2 номер устройства и номер канала через элементы И 169.58-169.70 и ИЛИ 171.58-171170 записываются в память 172.

Номер устройства с регистра Г24 команд поступает на управляющий выход блока 10 и далее на управляющий вход блока 1 синхронизации обмена, где записывается в регистр 103 номера устройства. Номер устройства сопровождается стробом с формирователя 126, который вырабатывается по сигналу с генератора 134 и коду операции второго типа с дешифратора 128 логическим умножением.

Одновременно с записью адреса в буферный регистр 8 в блоке 10 по сигналу с формирователя Й4 взводится триггер 139 запроса, сигнал с которого через командно-запросный выход блока 10 поступает на первый запросный вход 58-1 блока 13 приоритета.

В случае отсутствия более приоритетных запросов сигнал запроса с блока 10 поступает на выход 59 блока 13 и далее на установочный вход коммутатора 12 и на вход 54-2 запроса блока 11. С выхода 57 коммутатора 12 адрес поступает на информационный вход 54-1 блока 11 и с информационного выхода выдается в ш ину 26 адреса данных. Одновременно на за просном выходе 55-2 блока 11 появляется сигнал запроса, который выдается в шину 27.

Работа блока 11 связи с памятью при выдаче адреса ведется так же, как и при выполнении команды первого типа Адрес программы. . Триггер 139 запроса сбрасывается по сигналу ответа, который с выхочто и сигнал оонуления, выдаются на установочный выход 53-4 блока 10 и далее через установочный вход 50 узла 9 поступают на элемент И 183.1 и дешифратор 181 соответственно. Сигнал с выхода дешифратора 181 поступает на второй вход элемента И 183.1 и сбрасывает триггер 186.1, нулевой IQ сигнал с которого поступает на управляющий выход 51 блока 9. С выхода 51 сигнал поступает на установочный вход 52-6 блока 10, где принимается в формирователь 144 и блокирует выда- U чу сигнала обнуления и нулевого номера канала.

В случае, если дешифрирована команда Начать обмен с косвенностью,

25

30

Начать обмен необходимо произвести обращение .в оп2Q оперативную память за косвенным словом по адресу из полученной команды. Выполнение команды Начать обмен с косвенностью состоит из двух фаз. В первой фазе принимается первое слово команды, содержащее адрес косвенного слова команды. Обращение за косвенным словом выполняется так же, как и команда первого типа Адрес программы. Из оперативной памяти по шине 21 на вход 46 буферного регистра 7 поступает косвенное слово, которое с выхода 47 буферного регистра 7 подается на второй информационный вход 52-2 блока 10 управления. С второго информационного входа 52-2 косвенное слово записывается в регистр 124 через элементы И 118.1- 118.36 и ИЛИ 120.1-120.36, открытые сигналом строба, сопровождающим косвенное слово. Косвенное слово.со40 держит номер запускаемого канала, номер внешнего устройства и алрес следующей команды. По номеру запускаемого канала в узле 9 запуска каналов взводится триггер 186,1 работы.

35

да 59 блока 13 поступает на вход 52-7 45 Установка триггера 186.1 выполняется

так же, как и при выполнении команды Начать обмен без косвенности. Номер внешнего устройства с выхода регистра 124 поступает на управляющий 50 выход 53-1 блока 10 управления. С управляющего выхода 53-1 номер поступает на управляющий третий вход 30-3 блока 1.1 синхронизации обмена. Для примера рассмотрим запуск блока 1,1 синхронизации обмена.

подтверждения блока 10, Временная диаграмма обработки команды Начать обмен заканчивается, выдача тактовых импульсов с генератора 134 прекращается, С формирователя 144 выдается сигнал обнуления триггера 186.1. Сигнал обнуления образуется на формирователе 144 по отсутствию сигналов с генератора 13 и коду операции с дешифратора 128, Сигнал обнуления с формирователя 144 вместе с нулевым номером канала, выработанным на формирователе 144 по тем же условиям,

7358592/|

что и сигнал оонуления, выдаются на установочный выход 53-4 блока 10 и далее через установочный вход 50 узла 9 поступают на элемент И 183.1 и дешифратор 181 соответственно. Сигнал с выхода дешифратора 181 поступает на второй вход элемента И 183.1 и сбрасывает триггер 186.1, нулевой IQ сигнал с которого поступает на управляющий выход 51 блока 9. С выхода 51 сигнал поступает на установочный вход 52-6 блока 10, где принимается в формирователь 144 и блокирует выда- U чу сигнала обнуления и нулевого номера канала.

В случае, если дешифрирована команда Начать обмен с косвенностью,

25

30

Начать обмен необходимо произвести обращение .в оп2Q оперативную память за косвенным словом по адресу из полученной команды. Выполнение команды Начать обмен с косвенностью состоит из двух фаз. В первой фазе принимается первое слово команды, содержащее адрес косвенного слова команды. Обращение за косвенным словом выполняется так же, как и команда первого типа Адрес программы. Из оперативной памяти по шине 21 на вход 46 буферного регистра 7 поступает косвенное слово, которое с выхода 47 буферного регистра 7 подается на второй информационный вход 52-2 блока 10 управления. С второго информационного входа 52-2 косвенное слово записывается в регистр 124 через элементы И 118.1- 118.36 и ИЛИ 120.1-120.36, открытые сигналом строба, сопровождающим косвенное слово. Косвенное слово.со40 держит номер запускаемого канала, номер внешнего устройства и алрес следующей команды. По номеру запускаемого канала в узле 9 запуска каналов взводится триггер 186,1 работы.

35

Установка триггера 186.1 выполняется

так же, как и при выполнении команды Начать обмен без косвенности. Номер внешнего устройства с выхода регистра 124 поступает на управляющий выход 53-1 блока 10 управления. С управляющего выхода 53-1 номер поступает на управляющий третий вход 30-3 блока 1.1 синхронизации обмена. Для примера рассмотрим запуск блока 1,1 синхронизации обмена.

С управляющего входа 30-3 блока 1.1 номер внешнего устройства записывается на регистр 103.

25

Адрес программы с регистра 12 команд выдается на командно-запросный, выход блока 10 и далее на первый командный вход 2-2 регистра 5. С выхода 3 регистра 5 адрес поступает на информационный вход 48-2 буферного регистра 8 и с адресного выхода буферного регистра 8 на информационный вход 5&-2 коммутатора 12, открытого по установочному входу 56-5 сигналом с выхода 59 блока 13 приоритета. С выхода 57 коммутатора адрес поступает на информационный вход 54-1 блока 11 и с.информационного выхода 55-1 блока 11 выдается на выходную шину 26 .адреса данных. Одновременно с записью адреса с регистра 5 в буферный регистр 8 взводится триггер 139 запроса, сигнал с которого через командно-запросный выход 53-3 блока 10 поступает на первый запросный вход 58-1 блока 13, сигнал с выхода 59 которого поступает на блоки 12 и 11 на установочный и запросный входы и 54-2 соответственно. Так же, как и для команды Адрес программы, одновременно .с выдачей на буферный регистр 8 адрес с выхода 43 регистра 5 поступает на второй информационный вход 40-2 узла 4, где инкрементирует ся, и с выхода 41 узла 4 поступает на второй информационный вход 36-2 блока 2. В блоке 2 адрес с второго информационного входа 36-2 через элементы И 169,1-169.20 и ИЛИ 171.1- 171.20 записывается в память 172.

Выработка всех управляющих CHI- налов при этом выполняется так же, как и для команды Адрес программы.

Следующей выполняемой командой является команда третьего типа Запись, Она поступает с выхода 47 буферного регистра 7 через второй информационный вход 52-2 блока 10 управления и элементы И 118.1-118.36 и 120.1-120.36 на регистр 12 команд. Команда третьего типа всегда с косвенностью. Код операции внешнего устройства и управляющие признаки из регистра 124 команд заносятся в управляющее слово запускаемого канала . Номер канала из команды с регистра 124 поступает на командно-запросный выход 53-3 блока 10 и далее на второй запросный вход 44-2 блока 6 приоритета, В блоке 6 номер ка- нала с второго запросного входа 44-2

35859 . . 2б

через элементы ИЛИ 151.1-151.4 пос-. тупает на выход 45 блока 6 приоритет, и с него на адресный . вход 36-4 блока 2,. где определяет номер управляющего слова, в которое производится запись. . .

Адрес косвенного слова с регистра 124 передается, в блок 11 связи .Q с памятью через регистр 5t буферный регистр 8, коммутатор 12 так же, как и при выполнении обращения за косвенным словом команды Начать . обмен с косвенностью, С информаци- ., онного выхода блока 11 адрес поступает на выходную шину 26 адреса данных. Одновременно с записью в управляющее слово канала код операции внешнего устройства с регистра 20 124-поступает на управляющий выход 53-1 блока 10 и с него на управляющий вход 30-3 блока 1.1 синхронизации обмена и далее на регистр 102. Косвенное слово с выхода 47 бу 25 ферного регистра 7 поступает на второй информационный вход 52-2 блока 10 и через элементы И 118.1-118.36, и ИЛИ 120.1-120.36 записывается на регистр 124.. Косвенное слово содер- о жит адрес данных - адрес начала массива обмена в оперативной памяти и размер массива в байтах (количество байтов). Адрес данных и количество, байтов записываются в управляющее слово запускаемого канала, так же, 35 как и номер внешнего устройства при выполнении команды Начать обмен,.

Одновременно с записью адреса данных и количества байтов в блок 2- сигналом запуска с.выхода формиро- . 0 вателя 126 осуществляется запуск блока 1.1 синхронизации обмена на выполнение операции ввода-вывода. Сигнал запуска на формирователе 126 образуется из сигнала с выхода де- 45 шифратора 128, указывающего на прием косвенного слова команды третьего типа, и сигнала с выхода генератора 13V логическим умножением. На этом временная диаграмма отработ- 50 ки команды третьего типа заканчивается. .

По сигналу запуска с управляюще-. го входа 30-3 блока 1,1, поступающему на формирователь 1Q5, начина- 55 ется взаимодействие с внешним устройством..

Формирователь 105 сигналов интерфейса представляет собой комбинациейную схему из элементов И, ИЛИ, НЕ, на которой вырабатываются сигналы интерфейса. На входы формирователя 105 поступают сигналы от внешнего устройства, код операции с регист- ра 102 кода операции и сигнал со схемы 104 сравнения адресов. Из этих сигналов в формирователе 105 в соответствии с известным алгоритмом фор- мируются сигналы установки и сброса триггеров 116,1-116,Ь, с которых сигналы интерфейса через усилители 117.1-117.7 выдаются к внешнему устройству. На формирова- теле вырабатываются сигналы установки и сброса триггеров 116.1-116.6 сигналов интерфейса РАБ-К, РВС-К, ВБР-К, АЛ.Р-К, УПР-К, БЛК-К.

На формирователе 105 также об- разуется признак состояния, поступающий через усилитель 109.2 на управляющий выход 31-2 блока 1,1 и далее на вход 52-4 состояния блока 10. С входа 52-4 состояния признак сое- тояния поступает на формирователь 126. Признак состояния является логической суммой сигнала УПР-А с интерфейсного входа 30-2 блока 1,1 сигнала несравнения адресов со схемы 104, По включению питания сигналом с выхода формирователя 105 взводится триггер 116,1 РАБ-К,

Взаимодействие с внешним устройством начинается с выполнения по-.| следовательности начальной выбор- ки, В формирователе 105 вырабатывается сигнал установки триггера 116.4 АДР-К. По этому же сигналу на интерфейсный выход блока 1.1 с регистра 103 через элементы И 112.1-112.9, ИЛИ 114..9 и усилители 117.8-117.17 выдается номер внешнего устройства. Затем с формирователя 105 взводятся триггеры 116, и 116,3 РВБ-К, ВБР-К и через усили- тели 117.2 и 117,3 состояния триггеров выдаются на интерфейсный выход, 31-3 блока 1.1 и далее на выходную интерфейсную шину 25.1. По сигналу РАБ-А, поступающему по шине 20-1 .на интерфейсный вход 30-2 блока 1,1 и далее на формирователь 105, на формирователе вырабатывается сигнал обнуления триггера 116.4. На интерфейсный вход 30-2 с шины 20-1 поступает номер внешнего устройства, который с входа 30-2 поступает на схему 10 сравнения адресов, на другие входы

e

5

5 ® 5 ® 5

0

которой с регистра 103 поступает номер устройства. В случае совпадения номеров сигнал на выходе схемы 104 равен нулю и начальная выборка продолжается. В противном случае она прекращается. В оперативную память записывается слово состояния запущенного канала. По .сигналу с выхода схемы 104 через элемент ИЛИ 88 взводится триггер 89 запроса, сигнал с которого через усилитель 109.1 поступает на информационный выход 31-1 блока 1,1 синхронизации обмена и с него через первый вход 44-1 запроса блока 6 приоритета на элемент И 148.1.

Если блок 10 управления не занят отработкой текущего запроса, то сиг1 нал на выходе элемента ИЛИ Г35 равен нулю. Этот нулевой сигнал с командно-запросного выхода блока 10 поступает на второй вход 44-2 запроса блока 6 и через инвертор 147.1 разрешает прохождение запроса блока 1.1 через элемент И 148.1. Сигнал с выхода элемента И 148.1 поступает на выход 45 блока 6 и далее на вход 30-4 подтверждения блока 1,1. Сигнал входа 30-4 подтверждения поступает на вход управления третьим состоянием буферных усилителей 109.2 - 109,11 и на вход установки в О триггера 89 запроса. На вход усилителей поступает аварийный байт состояния из всех единиц с выходов элементов ИЛИ 115.1-115.9, на входы которых подается сигнал с выхода схемы. 104 сравнения. Байт состояния с выхода буферных усилителей 109.3- 109.11 поступает на второй выход 31-2 блока 1.1 и далее на вход 52-4 состояния блока 10, С входа 52-4 состояния байт состояния поступает на дешифратор 125. Признак состояния поступает на формирователь 144,

Аварийный байт состояния дешифрируется на дешифраторе 125, Сигнал с выхода дешифратора 125 поступает на входы формирователей 126 и 144. Одновременно с байтом состояния на вход 52-4 состояния блока 10 поступает запрос, по которому через элемент ИЛИ 130 запускается генератор 134 и открываются элементы И 132.-1 - 132.9, на вторые входы которых пос-. тупают сигналы с первого информацией ного входа 52-1 блока 10. На этот вход с регистра 3 поступают поля уп29

равляющих сигналов и номера канала из управляющего слова работающего канала через элементы ИЛИ 133.1 - 133.9, они поступают в формирователь 144. Считывание управляющего слова с блока 2 памяти выполняется в соответствии с номером канала, поступающим на адресный вход 36-4 блока 2. Номер канала выдается с выхода 45 блока 6 приоритета, где он образуется на шифраторе 149 по сигналу запросов .блока 1,1 с выхода элемента И 148.1.

Номер канала с выхода шифратора через элемент ИЛИ 151.1-151.4 поступает на выход 45 блока 6 и далее на адресный вход 36-4 блока 2.

При получении аварийного байта состояния дальнейшее взаимодействие с внешним устройством прекращается. На формирователе 126 по сигналу с дешифратора 125 вырабатывается сигнал отключения, который выдается на управляющий выход 53-1 блока 10 и далее на управляющий вход 30-3 блока 1.1,

В блоке 1.1 сигнал отключения поступает на формирователь .105 и инициирует последовательность отключения от внешнего устройства; триггеры 1l6. 116,3 сбрасываются.

В оперативную память записывается слово состояния запущенного канала, которое содержит аварийный байт состояния, адрес программы и признак прерывания. Слово состояния записывается по адресу, равному номеру канала. Остальные разряды адреса дополняются нулями. Адрес формируется из номера канала, хранящегося в управляющем слове запущенного канала, Номер канала поступает на адресный вход 48-1 буферного регистра 8 с выхода 39 регистра 3. Слово состояния канала формируется в буферном регистре содержит адрес программы из управляющего слова канала и байт состояния. Адрес программы пос- тупает на адресный вход 48-1 буферного регистра 8 с выхода 39 регистра 3, байт состояния поступает на инфорЯа- ционный вход 48-2 буферного регистра 8 с выхода 43 регистра 5. На информационный вход 42-2 регистра 5 байт состояния поступает с командно-запросного выхода блока 10, На этот выход байт состояния попадает с первого- информационного входа 52-1 блокд 10, j

.

1735 -5930

По признаку состояния и сигналу с дешифратора 125 в формирователе 144 1 образуется сигнал, устанавливающий триггер 137 прерывания и триггер 139

0

5

0

5

0

запроса, Запрос через командно-запросный выход блока 10 поступает на первый вход 58-1 запроса блока 13. Сигнал с выхода блока 13 поступает на установочный вход коммутатора 12 и вход запроса блока 11 связи с памятью. Сигнал прерывания с триггера 138 поступает на выход 53-2 запроса, блока 10 и далее через выходную шину 28 в регистр прерываний центрального процессора. Сигнал с формирователя 144, устанавливающий триггер 137, поступает на установочный выход 53-4 блока 10 и далее на установочный вход 50 узла 9. Одновременно с этим сигналом в узел 9 выдается номер работающего канала.

Номер канала поступает на дешифратор 181, сигнал с выхода которого открывает элементы И 183.2 и 184.2, на вторые входы которых поступает сигнал установки триггера 137 с входа 50 узла 9, По сигналам с выходов элементов И 183,2 и 184.2 сбрасывается триггер 186,2 работы канала и взводится триггер 187.2 прерывания канала. Сигналы с выходов триггеров 186,2 и 187,2 через выход 51 узла 9 поступают на вход 52-6 блока 10 и далее в формирователь 144,

5 где образуются сигналы сброса триггеров 137 и 139. Триггеры 137 и 139 сбрасываются, сдвиг генератора 134 прекращается, отработка аварийного байта состояния заканчивается.

Начальная выборка при сравнении номеров внешних устройств продолжается выдачей кода операции с регистра 102 кода операции блока 1.1 через элементы И 111,t-111,9, открытые

5 сигналом с выхода формирователя 105 через триггеры 116, через элементы ИЛИ 114.1 - 114.9 и усилители 117.8- 117.Т7 на третий выход 31-3 блока 1.1. Код операций сопровождается

0 сигналом УПР-К с усилителя 117,5, на который он поступает с триггера 116,5, установленного сигналом с выхода формирователя 105. В ответ на код операции на интерфейсный вход

5 30-2 блока 1.1 от внешнего устройства поступает байт состояния, который записывается на регистр 107 байта состояния по сигналу УПР-А,

0

31

По сигналу УПР-А на формирователе 105 вырабатывается признак состояния, который поступает на элемент ИЛИ 88 и устанавливает триггер 89 запроса. Запрос через усилитель 109. поступает на информационный выход 31-1 блока 1.1 и далее в блок 6 приоритета. Запрос по байту состояния внешнего устройств отрабатывается так же, как и запрос по несравнению номеров устройства Если байт состояния, поступивший на дешифратор 125 байта состояния, не нулевой, то обмен с устройством заканчивается, слово состояния канала записывается в оперативную память, а в блоке 1.1 выполняется отключение от интерфейса.

Если байт состояния равен нулю, то по сигналу с дешифратора 125 в формирователе 126 вырабатывается сигнал продолжения операции ввода-вывода и выдается на управляющий выход блока 10, с которого поступает на управляющий вход 30-3 блока 1.1, Сигнал с управляющего входа поступает на формирователь 105 и вызывает продолжение операции обмена. Одновременно с блока 2 памяти с выхода 37 на регистр 3 считывается управляющее слово канала так же, как и при отработке аварийного байта состояния. С регистра 3 номер канала и управляющие признаки через первый информационный вход 52-1 блока 10 и элементы И 132.1-132.9 и ИЛИ 133.1- 133.9 поступают в формирователь 144, Адрес данных с регистра 3 с выхода 39 поступает на адресный вход 48-1 буферного регистра 8 и первый ин- формационный вход 40-1 узла 4,

С входа 40-1 узла 4 адрес данных через элементы И 173.1-173.20 и ИЛИ 177.1-177.20 поступает на сумматор 180 где инкрементируется на единицу. С выхода сумматора адрес данных заносится в УСК через эле- - менты И 169.21-169.41 и ИЛИ 171.21- 171.41, Сигналы, открывающие элементы И 173 и ИЛИ 171| и инкремент, поступают с командно-запросного выхода 53-3 блока 10, где они выраба- Чываются на формирователе 144, После того, как адрес данных модифицирован и записан в память 172, модифицируется поле КБ, размер массива уменьшается на 4. Размер массива с регистра 3 через элементы И 175.1 175,12 и ИЛИ 177.1-177.12 поступа-173585932

ет на сумматор 180, на второй вход которого с входа 40-3 модификации уз ла 4 поступает код четырех с команд, но-запросного выхода 53-3 блока 10 управления, где вырабатывается в формирователе 144,

Код четырех выдается также на управляющий выход 53-1 блока 10 уп10 равления и поступает на управляющий вход блока 1.1 синхронизации обмена, где записывается в сметчик 82. Размер массива, уменьшенный на четыре, с выхода сумматора 180 поступает йа

15 второй информационный вход 36-2 блока 2, Через элементы И 169.41-169.52 и ИЛИ 171.41 - 171.52 размер массива заносится в память 172,

Одновременно размер массива посту20 пает на элемент ИЛИ 178. Если массив исчерпан, то сигнал на выходе элемента ИЛИ 178 равен нулю. Этот сигнал инвертируется на элементе НЕ 179 и записывается в управляющее

25 слово канала в поле признака Конец обмена. При следующем запросе блока 1.1 синхронизации обмена этот признак будет выдан в блок 1.1 на формирователь 105, где по нему будет сформиjn рована последовательность окончания. Одновременно с модификацией адреса данных, предыдущее значение адреса с адресного выхода 49-1 буферного регистра 8 поступает на первый адресный вход 56-1 коммутатора 12. В

35 блоке 10 управления взводится триггер 139 запроса, который через блок 13 приоритета поступает на вход 56-5 коммутатора 12 и в блок 11 связи с памятью на вход 54-2. Одновременно с

® взведением триггера 139 запроса номер канала, поступающий в блок 10 управления с регистра 3 с выходов элементов ИЛИ 133.6-133.9, записывается в буферный регистр 140 номера нала через элементы И 145.1-145.4 и ИЛИ 146.1 - 146,4, Элементы И 145.1 145.4 открыты сигналом с входа 52-7 подтверждения блока 10, на который сигнал поступает с выхода 59 под тверждения блока 13. Этим же сигналом устанавливается триггер 142 занятости регистра ЙО номера канала. Сигнал с прямого выхода триггера 142 занятости поступает на элемен55 ты И 143.1-143.4, на вторые входы которых поступают сигналы с выхода дешифратора 141 номера канала, связанного с выходом регистра 140. Ин331

версный выход триггера 142 блокиру- ет запуск генератора 134 и прием кода в регистр 124 команды сигналом с выхода элемента И 123, так как с буферного регистра 7 поступает не команда, а слово данных для блока 1,1 синхронизации обмена. Строб, сопровождающий слово данных с второго входа блока 10 управления, поступает на третьи входы элементов И , 143.1-143.15. На выходе элемента И 143.1, открытого сигналом с выхода дешифратора 141, появляется сигнал ,строба, который с управляющего выхода блока 10 поступает в блок 1.1 синхронизации обмена, выдавший запрос с байтом состояния, на управляющий вход 30-3. Строб сопровождает слово данных с выхода 47 буферного регистра 7. В блоке 1.1 синхронизации обмена слово с информационного входа 30-1 блока записывается в регистр 106 по стробу, сопровождающему слово, поступающему на вход управления записью регистра 106 приема.

Одновременно через элемент ИЛИ 83 взводится триггер 8 наличия информации на регистре приема. Выход триггера 84 через элемент И 85, открытый .сигналом с инверсного выхода триггера 92, стробирует перепись ело1 ва данных с регистра 106 приема на регистр 108 выдачи. Байт данных с регистра 108 через элементы И 113.1- 113.9 и ИЛИ 114. 1-114.9 и усилители 117.8-117.17 поступает на интерфейсный выход блока 1,1 и с него на шину 25-1. Сигнал с выхода элемента И 85 взводит триггер 92 наличия информации на регистре 108, сигнал с инверсного выхода которого закрывает элемент И 85. Сигналом с триггера 92 через элемент И 99, открытый сигналом ИНФ-А с интерфейсного входа 30-2 блока 1,1 и кодом операции Запись с регистра 102 через элемент ИЛИ 95 взводится триггер 96 ИНФ-К. Сигнал ИНФ-К через усилитель 117.7 выдается на интерфейсный выход, блока 1.1 и далее на внешнее устройство по шине . Сигналом с выхода элемента И 101, на вход которого поступает сигнал ИНФ-А с интерфейсного входа 30-2 блока 1.1 и сигнал с инверсного выхода триггера 96 осуществляется сдвиг счетчика 82 и сдвиг регистра 108 выдачи через эле15

20

35С59-3

мент И 97, выход которого соединен с входом сдвига регистра ЮР выдачи. На выходные усилители 117.8-117.17 через элементы И 113.1-И 3.9 и ИЛИ , 11 Ц. .9 выдается новый байт данных с регистра 108 выдачи. Выдача байтов данных продолжается до тех г.ор, пока на выходе сметчика 82 JQ не появится сигнал, указывающий, что на счетчике 82 нулевое значение. Этот сигнал через элементы И 90 и ИЛИ 91 сбрасывает триггер 92, Регистр 108 выдачи свободен для.приема нового слова данных, которое находится на регистре 106 приема. Как только первое слово данных переписывается из регистра 106 приема на регистр 108 выдачи и триггер 84 сбрасывается сигналом с выхода.элемента И 85, взводится триггер 89 запроса сигналом с инверсного выхода триггера через элементы И 86 и ИЛИ 88.

Сигнал запроса с информационного 25 выхода 31-1 блока 1.1 поступает на первый вход 44-1 запроса блока 6. ,По сигналу с выхода 45 блока 6 с |блока 1,1 с управляющего выхода 31-2 в блок 10 выдается запрос с нулевым признаком состояния.

В блоке 6 по этому запросу формируется номер канала, по которому с блока 2 на регистр 3 считывается управляющее слово запускаемого канала. По адресу данных с регистра 3 через 35 буферный регистр 8, коммутатор 12 и блок 11 производится обращение в оперативную память по шине 26 так же, как и при отработке запроса с нулевым байтом состояния. Слово данных 0 с буферного регистра 7 записывается в регистр 106 блока 1,1 через информационные выход и вход 4 и 30-1 соответственно.

45 Первое слово данных с регистра 106 приема переписывается на регистр 108 выдачи, в счетчике 82 восстанавливается исходное значение. Операция записи продолжается; По освобож50 дению регистра 106 в блок 6 приоритета выдается очередной запрос данных Обмен продолжается до тех пор, пока не исчерпывается размер массива. При исчерпании массива все разряды

jj поля количества байтов становятся t. нулевыми и на выходе элемента HF. 179 появляется сигнал, который записы- вается в управляющее слово канала в поле признака Конец обмена.

30

При очередном обращении за данными этот признак выдается в блок 1.1 синхронизации обмена, где пос- тупает в формирователь 105. По этому признаку во внешнее устройство выдается сигнал УПР-К с триггера 116.5 через усилитель 117.5 и выход 31-3. Обмен данными заканчивается и внешнее устройство передает в блок 1.1 синхронизации обмена конечный байт состояния, который записывается в регистр 107 интерфейсного входа 30-2 блока 1.1. С блока 1.1 синхронизации обмена в блок 6 выдается запрос, который отрабатывается аналогично запросу с нулевым байтом состояния.

В блок 1.1 синхронизации обмена в ответ на конечный байт с блока 10 с управляющего выхода поступает сигнал отключения, который вырабатывается на формирователе 126. По сигналу отключения в блоке 1,1 инициируется последовательность окончания После успешного завершения команды третьего типа при отработке запроса с конечным байтом состояния в блоке 10 управления формируется запрос за следующей командой. Адрес программы с регистра 3 через буферный регистр 8, коммутатор 12 и блок 11 связи с памятью поступает на шину 26 адреса данных и далее в оперативную память. По адресу считывается команда второго типа Остановить обмен. Это команда без косвенности, по ней сбрасывается триггер 186.2 работы запущенного -канала. Если в команде присутствует признак программно-управляемого прерывания, то после окончания выполнения команды в оперативную память будет записано слово сос- .тояния канала и в центральный процессор выдается прерывание с триггера 137.

Выделенные селекторные каналы 14.1-1.п содержат, кроме блоков 15.1-15.п. синхронизации обмена, блок 16.i управления каналом, счетчики 17.1-17.п и 18.1-18.п адреса и количества байтов соответственно и буферные усилители 19.1-19.п.

Работа выделенного канала по командам первого и второго типов происходит так же, как и для остальных каналов. Однако адрес данных и количество байтов с регистра 12 команд записываются не в управляющее слово

o

5

0

5

0

5

0

5

0

5

канала в памяти 172, а в счетчики 17 и 18. апись адреса данных и количества байтов в счетчики 17 и 18 производится при отработке косвенного слова команды третьего типа. Ад1 рее данных и количество байтов, поступившие на регистр 5 ввода с блока 10 управления с регистра 12, с выхода 3 регистра 5 поступают на вход 60-1 селекторного канала 1.1 и с командного входа 60-1 на входы 77-2 и 78-2 счетчиков 17 и 18. Прием адреса данных и количества байтов в счетчики 17.1 и 18,1 производится по сиг-налу строба записи, поступающему на входы и 78-1 счетчиков 17 и 18 с -входа 65-1 строба.

Строб записи на стробирующий вход 65-1 поступает с командно-запросного выхода блока 10, где он образуется на формирователе из номера канала и сигнала генератора 13 логическим умножением. Счетчик 18 считает на уменьшение, а счетчик 17 на увеличение.

Блоки 15.1-15.л синхронизации обмена каналов 1.1-1А,п аналогичны блокам 1.1-1.т, однако буферные усилители. 1 10. 1-1 10.37 и 109.2-109.11 находятся постоянно в открытом состоянии. Управление выдачей данных в коммутатор 12, на регистр 5 ввода и в блок 10 управления осуществляется в блоке 16 развязки. При отработке запроса с байтом состояния запрос с управляющего выхода блока, 15 поступает на управляющий вход 75-2 блока 16 и через элемент И 161, открытый сигналом состояния, с управляющего входа 75-2 поступает в блок 6 приоритета. По сигналу ответа, поступающему с выхода kS блока 6 на вход 61 подтверждения канала 1.1 и далее на первый вход подтверждения блока 16, открываются буферные усилители 158.1-158.11 и байт состояния с признаком состояния и запрос выдаются с выхода 76-1 состояния блока 16 на выход 70 канала 1.1 и далее на вход 52-4 блока 10. Сигнал ответа через элемент ИЛИ 167 поступает на выход 76-6;подтверждения блока 16 и далее на вход 73- подтверждения блока 15, где обну- ляет триггер 89 запроса. В остальном отработка байта состояния выполняется так же, как и в остальных каналах.

37

При отработке запроса данных элемент И 161 закрыт отсутствием сигнала состояния с управляющего входа блока 16, элемент И 162 открыт сигналом с инвертора 163, и запрос с выхода элемента И 1б2 выдается на вход 7б- запроса блока 16 и через выход 69 запроса канала .1 поступает на второй вход 58-2 запрос блока 13. При этом обращения в блок 10 управления не проис.-одит.

По запросу в блоке 13 вырабатывается сигнал ответа, который с выхода 59 блока 13 через второй вход 66 подтверждения канала .1 поступает на второй вход 75- подтверждения блока 16, где открывает буферные усилители 160,1-160,36 и 19. Через усилители 160.1-160,36 на коммутатор 12 поступает слово данных при записи в оперативную память, через усилители 15, в коммутатор 12 поступает адрес данных со счетчика 17 адреса. Сигнал с выхода 59 блока 13, поступающий на второй вход 75 подтверждения блока

16через элемент ИЛИ 167, выдается на выход 6-6 подтверждения блока 16 и далее на вход 73- подтверждения блока 15, где обнуляет триггер 89.

После того, как триггер 89 сбрасывается, сигнал ответа с блока 13 приоритета становится равным нулю, формируется задний фронт сигнала ответа длительностью один такт синхронизации на элемент И 165, на вход которого поступает инвертированный сигнал ответа с элемента НЕ 16 и задержанный сигнал ответа с выхода D-триггера 166, По заднему фронту ответа происходит сдвиг счетчиков

17и 18 адреса и количества байтов.

Размер массива, хранящийся в счетчике 18, задан в словах. Когда массив полностью исчерпан, значение счетчика 18 становится равным нулю, на-выходе 79 окончания счета появляется сигнал, аналогичный сигналу Конец обмена с выхода элемента НЕ 179. Сигнал окончания счета с выхода 79 счетчика 18 через управляющий вход блока 15 синхронизации обмена поступает на формирователь 105 и инициирует выполнение последовательности окончания.

Запрос с конечным байтом состояния отрабатывается так же, как и для обычных каналов.

585938

Блок 15 синхронизации обмена формирует все последовательности для селекторного канала, в том числе отрабатывается режим Внимание, При отработке этого режима формируется запрос по состоянию, который выполняется так же, как и запрос с конечным байтом состояния. В дополнение

to

к этому формируется слово состояния

0

канала, к которому происходит обращение. В это слово заносится принятый байт состояния и номер активно- го устройства.

, Устройство для управления вводом- выводом обеспечивает взаимодействие с внешними устройствами, имеющими высокий темп обмена за счет введения выделенных селекторных каналов,

0 Пропускная способность выделенных каналов существенно увеличивается по сравнению с остальными каналами устройства за счет организации не- посредственного обращения с бло5 ков синхронизации обмена этих каналов в узел связи с памятью, минуя блок управления, имеющий большое время обслуживания запросов. Вместе с тем для выполнения команд первого и второго типов, анализа байтов состояния используется общее оборудование устройства в блоке управления, так как эти действия не являются критичными по времени отработки.

I

5 Предложенное решение является эффективным, более чем в 2 раза по сравнению с прототипом увеличивает пропускную способность каналов и сохраняет для выделенных селекторных

0 каналов все возможности по гибкому программированию обменов с внешними устройствами.

Применение устройства в составе вычислительной машины позволяет су5 щественно увеличить объем внешней памяти за счет подключения магнитных дисков большой емкости, имеющих высокий темп обмена, сохранив при этом то же программное обеспечение благо,0 даря полной совместимости выделенных и обычных каналов устройства.

Формула изобретения

5 Устройство для управления вводом- выводом, содержащее m блоков синхро- .низации обмена, блок памяти, исполнительный регистр, узел модификаций,

регистр ввода, первый блок приоритета, первый и второй буферные регистры, узел запуска каналов, блок управления, блок связи с памятью, информационные входы блоков синхрони- зации обмена соединены с выходом первого буферного регистра, интерфейсные входы блоков синхронизации обмена соединены с входными интерфейсными шинами устройства, информационные выходы блоков синхронизации обмена Соединены с информационным входом регистра ввода и первым входом запросов первого блока приоритета, управляющие выходы блоков синхронизации обмена соединены с входом состояния блока управления, интерфейсные выходы блоков синхронизации обмена соединены с выходными интерфейсными шинами устройства, первый информационный вход блока памяти и первый информационный вход узла модификации подключены к выходу регистра ввода, выход первого блока приоритета подключен к управляющему входу регистра ввода, адресному входу блока памяти и входам подтверждения блоков синхронизации обмена, выход блока памяти соединен с информационным входом исполнительного регистра, выход которого соединен с вторыми информационными входами блока памяти и узла модификации, выход которого подключен к третьему информационному входу блока памяти, первый выход блока управления соединен с управляющими входами блоков синхронизации обмена, второй выход блока управления является выходной шиной запроса в центральный процессор устройства, третий выход блока управления соединен с вторым входом запросов пер- кого блока приоритета, первым командным входом регистра ввода, четвертый выход блока управления подключен к установочному входу узла запуска каналов, выход которого соединен с установочным входом блока управления, первый информационный вход которого и второй командный вход регистра ввода соединены с выходом первого буферного регистра, информационный вход которого подключен к входной шине данных устройства, входная шина строба от центрального процессора устройства соединена с входом стробирования блока управления, входная шина команды устройст0

5

0

5

ва подключена к командному входу бло-, ка управления, информационный выход блока связи с памятью соединен с выходной шиной адреса данных устройства, выход запроса блока связи с памятью соединен с шиной запроса в оперативную память устройства, о т- личающееся тем, что, с целью повышения быстродействия, введены коммутатор памяти, второй блок приоритета и п селекторных каналов, причем адресный вход второго буферного регистра подключен к выходу исполнительного регистра, информационный вход - к выходу регистра ввода, адресный и информационный выходы второго буферного регистра соединены с первыми адресным и информационным входами коммутатора памяти, к вторым информационному и адресному входам которого подключены адресные и информационные выходы п селекторных каналов соответственно, к управляющему входу коммутатора памяти и к входу запроса блока связи с памятью подключен выход второго блока приоритета, выход коммутатора памяти соединен с информационным входом блока связи с памятью, первый вход запроса второго блока приоритета, управляющий вход исполнительного регистра, вход модификации узла модификации и управляющий вход блока памяти соединены с третьим выходом 5 блока управления, второй вход запросов второго блока приоритета подключен к выходам запросов п селекторных каналов, выходы запроса состояния которых соединены с информационным входом регистра ввода и первым входом запросов первого блока приоритета, выходы состояний селекторных каналов подключены к входу состояния блока управления, вход под- тверждения и второй информационный вход которого соединены с выходом второго блока приоритета и исполнительного регистра, командные входы п селекторных каналов соединены с выходом регистра ввода, первый и второй входы подтверждения п селекторных каналов подключены соответственно к выходам первого и второго блоков приоритета, информационные входы п селекторных каналов соединены с выходом первого буферного регистра, первый и второй управляющие входы п селекторных каналов под0

0

5

0

5

м

ключены к первому и третьему выходам блока управления, интерфейсные входы и выходы п селекторных каналов соединены с входными и выходными интерфейсными шинами устройства, при этом , каждый селекторный канал содержит блок синхронизации обмена, блок развязки, счетчик адреса, счетчик количества байтов, буферный усилитель, при этом в селекторном канале информационный вход блока синхронизации обмена соединен с информационным входом- селекторного канала, интерфейсный вход блока синхронизации обмена подключен к интерфейсному входу селекторного канала, управляющий вход блока синхронизации - к первому управляющему входу селекторного канала, вход подтверждения блока синхронизации обмена соединен с выходом подтверждения блока развязки, информационный и управляющий выходы блока синхронизации обмена соединены соот17

ветственно с информационным и управ-jj счетчика количества байтов соединен ляющим входами блока развязки, первый с управляющим входом блока синхро- вход подтверждения которого подклю- низации обмена, чен к первому входу подтверждения с-е Таблица Г

векторного канала, второй вход подтверждения блока развязки соединен с вторым входом подтверждения селекторного канала, выходы состояния, запроса состояния, информационный выход и выход запроса блока развязки соедине1-1 ны с одноименными выходами селекторного канала соответственно, выход