Изобретение относится к импульсной радиотехнике и автоматике и может быть использовано в управляющих устройствах чертежнографических автоматов, в частности для разгона и торможения шаговых двигателей.

Известны управляемые делители частоты, у которых изменение коэффициента деления задается извне либо по заданной программе, либо специальным блокам.

Одно из известных устройств содержит счетчики, устройства для заниси обратного кода и логические элементы.

Однако в таком устройстве изменение коэффициента деления задается извне по заданной программе, что требует дополнительной разработки специальных устройств для задания программ изменения коэффициента деления.

Другое из известных устройств более совершенно и содержит дешифратор, двоичный делитель частоты, первый вход которого подключен к входной шине, второй вход через блок заниси параллельного кода - к первому выходу реверсивного счетчика, а выход - к входу блока записи параллельного кода и к первым входам элементов И, выходы которых соединены с входами реверсивного счетчика.

Однако такое устройство непригодно для схем управления шаговыми двигателями при отработке последними количества шагов, не кратных удвоенному значению максимального

числа в реверсивном счетчике, например, в чсртежно-графических автоматах.

Цель изобретения - расширение функциональных возмон ностей делителя частоты. Это достигается тем, что в предлагаемый делитель частоты с автоматически изменяющимся коэффициентом деления введены блок сравнения, вычитающий счетчик и коммутатор, при этом первый вход вычитающего счетчика подключен к выходу двоичного делителя частоты, второй вход - к кодовой шине, а выход - к входу дешифратора и первому входу блока сравнения, второй вход которого соединен с .первым выходом реверсивного счетчика,

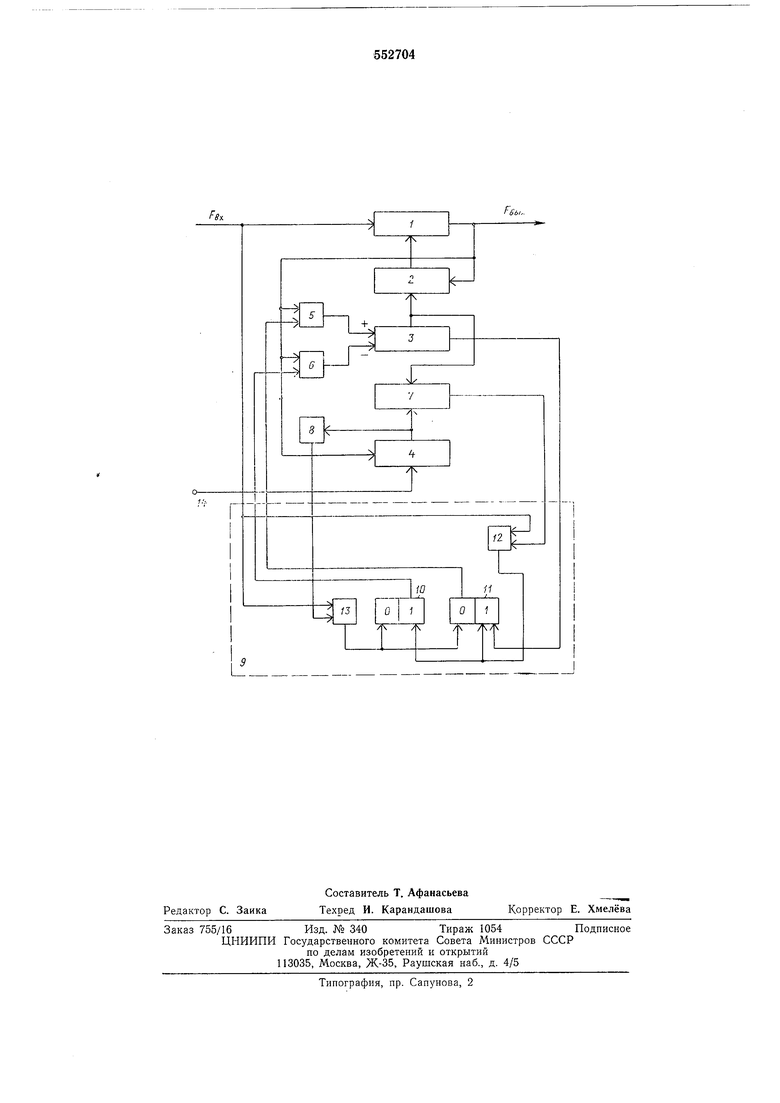

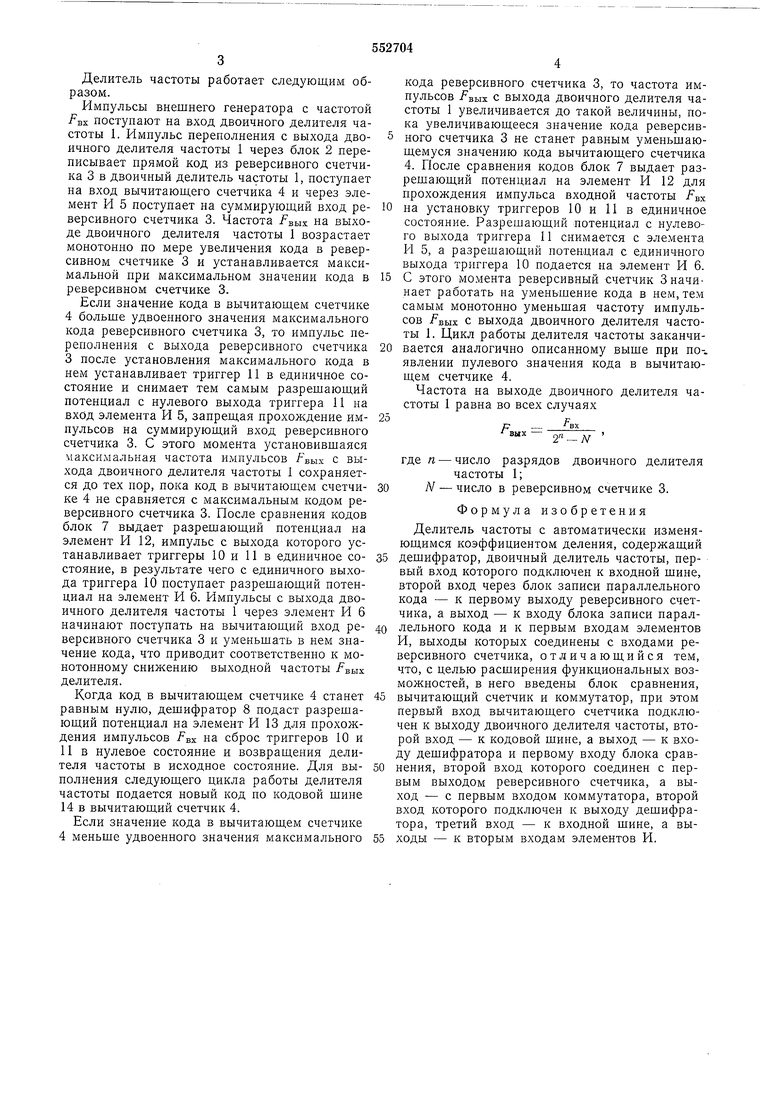

а выход - с первым входом коммутатора, второй вход которого подключен к выходу дешифратора, третий вход - к входной шине, а выходы - к вторым входам элементов И. На чертеже представлена структурная электрическая схема предлагаемого делителя частоты с автоматически изменяющимся коэффициентом деления.

Предлагаемое устройство содержит двоичный делитель частоты 1, блок 2 записи параллельного кода, реверсивный датчик 3, вычитающий счетчик 4, элементы И 5 и 6, блок 7 сравнения, дешифратор 8 и коммутатор 9, который содержит триггеры 10 и 11 и элементы И 12 и 13 (14-кодовая шина).

Делитель частоты работает следующим образом.

Импульсы внешнего генератора с частотой FB поступают на вход двончного делителя частоты 1. Импульс переполнения с выхода двоичного делителя частоты 1 через блок 2 переписывает прямой код из реверсивного счетчика 3 в двоичный делитель частоты 1, поступает на вход вычитающего счетчика 4 и через элемент И 5 поступает на суммирующий вход реверсивного счетчика 3. Частота /вых на выходе двоичного делителя частоты 1 возрастает монотонно по мере увеличения кода в реверсивном счетчике 3 и устанавливается максимальной при максимальном значении кода в реверсивном счетчике 3.

Если значение кода в вычитающем счетчике 4 больше удвоенного значения максимального кода реверсивного счетчика 3, то импульс переполнения с выхода реверсивного счетчика

3после установления максимального кода в нем устанавливает триггер 11 в единичное состояние и снимает тем самым разрешающий потенциал с нулевого выхода триггера 11 на вход элемента И 5, запрещая прохождение импульсов на суммирующий вход реверсивного счетчика 3. С этого момента установившаяся максимальная частота импульсов с выхода двоичного делителя частоты I сохраняется до тех пор, пока код в вычитающем счетчике 4 не сравняется с максимальным кодом реверсивного счетчика 3. После сравнения кодов блок 7 выдает разрешающий потенциал на элемент И 12, импульс с выхода которого устанавливает триггеры 10 и 11 в единичное состояние, в результате чего с единичного выхода триггера 10 поступает разрешающий потенциал на элемент И 6. Импульсы с выхода двоичного делителя частоты 1 через элемент И 6 начинают поступать на вычитающий вход реверсивного счетчика 3 и уменьшать в нем значение кода, что приводит соответственно к монотонному снижению выходной частоты /вых делителя.

Когда код в вычитающем счетчике 4 станет равным нулю, дешифратор 8 подаст разрешающий потенциал на элемент И 13 для прохождения импульсов FBK на сброс триггеров 10 и 11 в нулевое состояние и возвращения делителя частоты в исходное состояние. Для выполнения следующего цикла работы делителя частоты подается новый код по кодовой шине 14 в вычитающий счетчик 4.

Если значение кода в вычитающем счетчике

4меньще удвоенного значения максимального

кода реверсивного счетчика 3, то частота импульсов /вых с выхода двоичного делителя частоты 1 увеличивается до такой величины, пока увеличивающееся значение кода реверсивного счетчика 3 не станет равным уменьшающемуся значению кода вычитающего счетчика 4. После сравнения кодов блок 7 выдает разрещающий нотенциал на элемент И 12 для прохождения импульса входной частоты FB-S.

на установку триггеров 10 и И в единичное состояние. Разрешающий потенциал с нулевого выхода триггера 11 снимается с эле.мента И 5, а разрешающий нотенциал с единичного выхода триггера 10 подается на элемент И 6.

С этого мо.мента реверсивный счетчик 3 начинает работать на уменьшение кода в нем, тем самым монотонно уменьщая частоту импульсов .РБЫХ с выхода двоичного делителя частоты 1. Цикл работы делителя частоты заканчивается аналогично описанному выще при по-, явлении пулевого значення кода в вычитающем счетчике 4.

Частота на выходе двоичного делителя частоты 1 равна во всех случаях

р

77„ ВХ

вых-

где п - число разрядов двоичного делителя

частоты 1; Л - число в реверсивном счетчике 3.

Формула изобретения

Делитель частоты с автоматически изменяющимся коэффициентом деления, содержащий

дешифратор, двоичный делитель частоты, первый вход которого подключен к входной шине, второй вход через блок записи параллельного кода - к первому выходу реверсивного счетчика, а выход - к входу блока записи параллельного кода и к первым входам элементов И, выходы которых соединены с входами реверсивного счетчика, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены блок сравнения,

вычитающий счетчик и коммутатор, нри этом первый вход вычитающего счетчика подключен к выходу двоичного делителя частоты, второй вход - к кодовой шине, а выход - к входу дешифратора и первому входу блока сравнения, второй вход которого соединен с первым выходом реверсивного счетчика, а выход - с первым входом коммутатора, второй вход которого подключен к выходу дешифратора, третий вход - к входной шине, а выходы - к вторым входам элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следованияиМпульСОВ C АВТОМАТичЕСКи изМЕНяющиМСяКОэффициЕНТОМ дЕлЕНия | 1978 |

|

SU801253A1 |

| Многоканальное программное задающее устройство | 1986 |

|

SU1383297A1 |

| Делитель частоты следования импульсов с автоматически изменяющимся коэффициентом деления | 1984 |

|

SU1221746A1 |

| Устройство для программного управления с самоконтролем | 1983 |

|

SU1130832A1 |

| Устройство для сглаживания периодических случайных сигналов | 1983 |

|

SU1242987A2 |

| Устройство для управления шаговым электродвигателем | 1980 |

|

SU928592A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Измеритель переходных характеристик частотных прецизионных устройств | 1987 |

|

SU1620992A1 |

| Цифровой измеритель магнитной индукции | 1990 |

|

SU1755221A1 |

| Генератор пачек импульсов | 1979 |

|

SU834847A1 |

Авторы

Даты

1977-03-30—Публикация

1976-02-24—Подача