со оо оо го со

Изобретение относится к области автоматического регулирования и может быть использовано в устройствах управления производственными процессами по заранее заданной программе одновременно по нескольким каналам управления.

Целью изобретения является повышение точности многоканального программного задающего устройства и уменьшение числа линий связи.

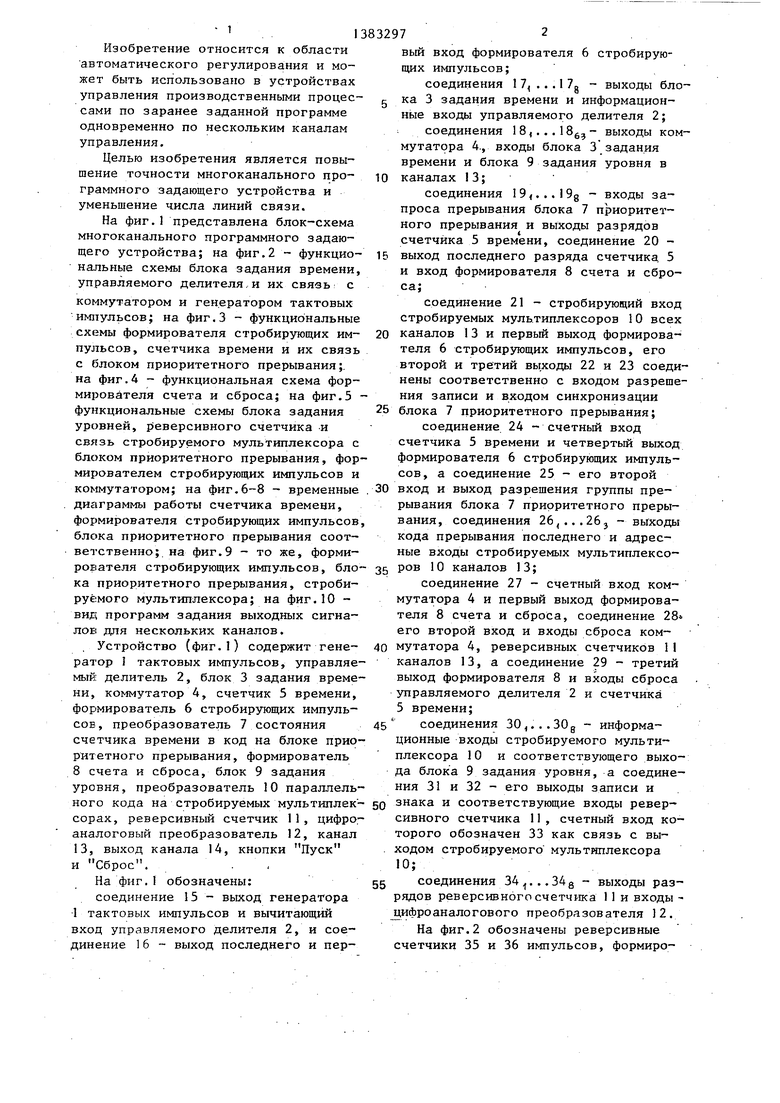

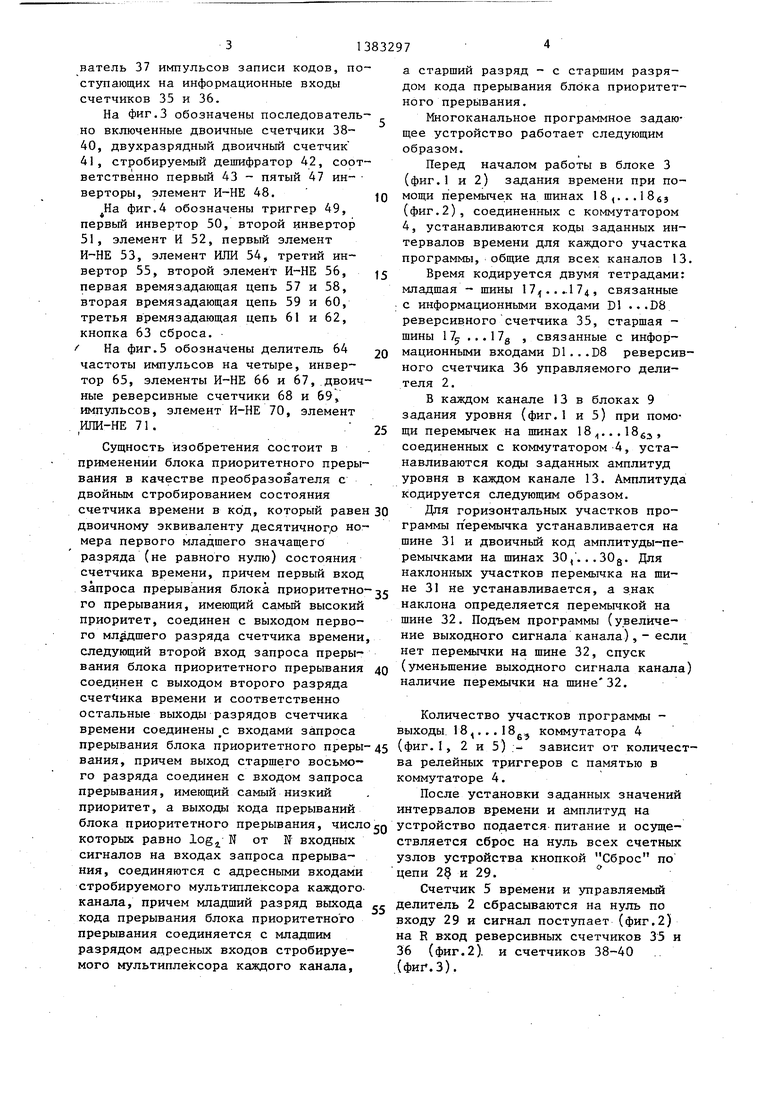

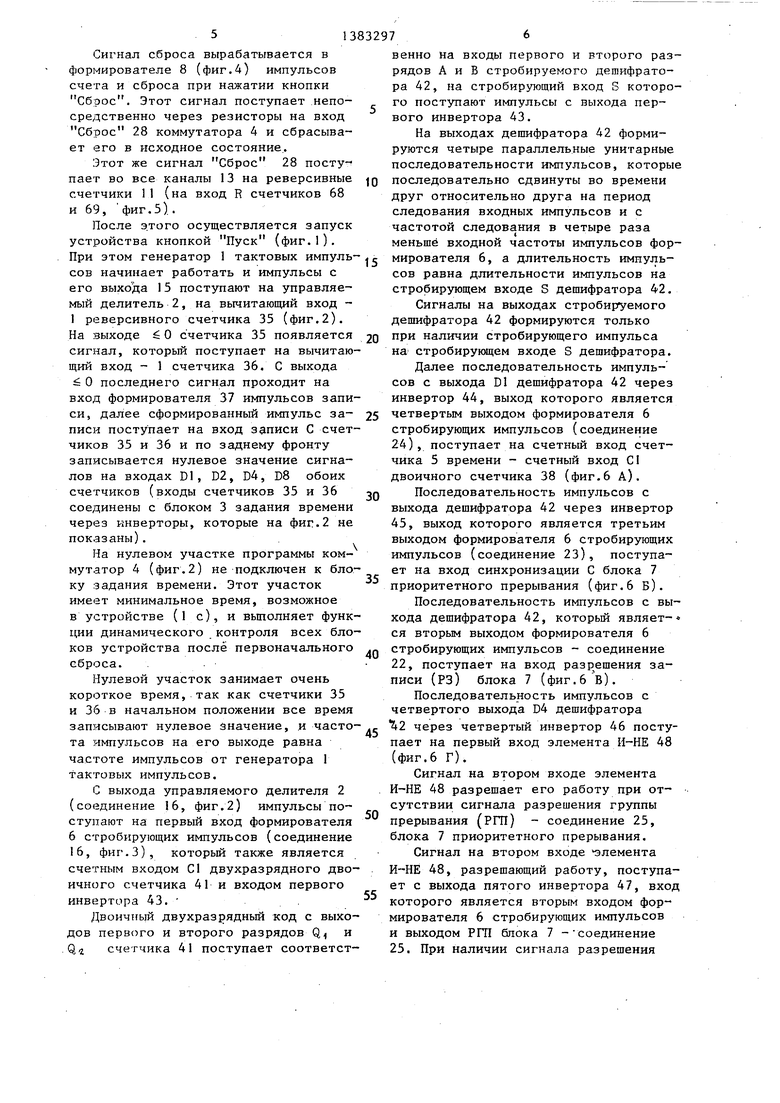

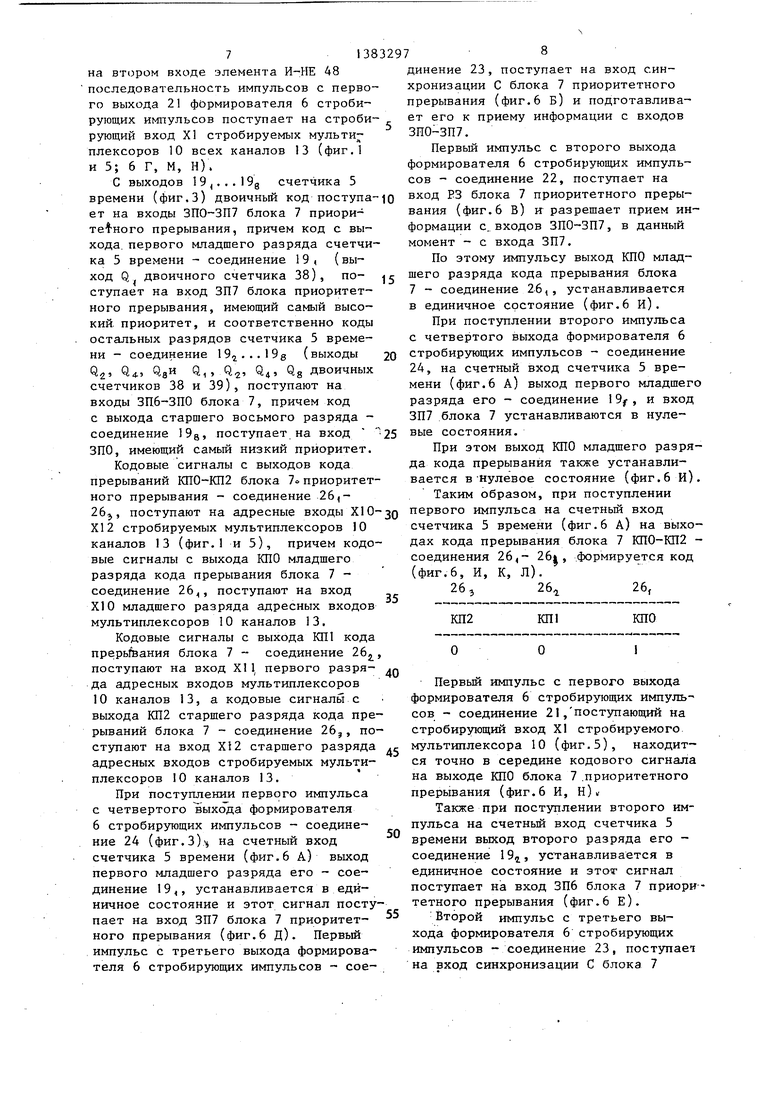

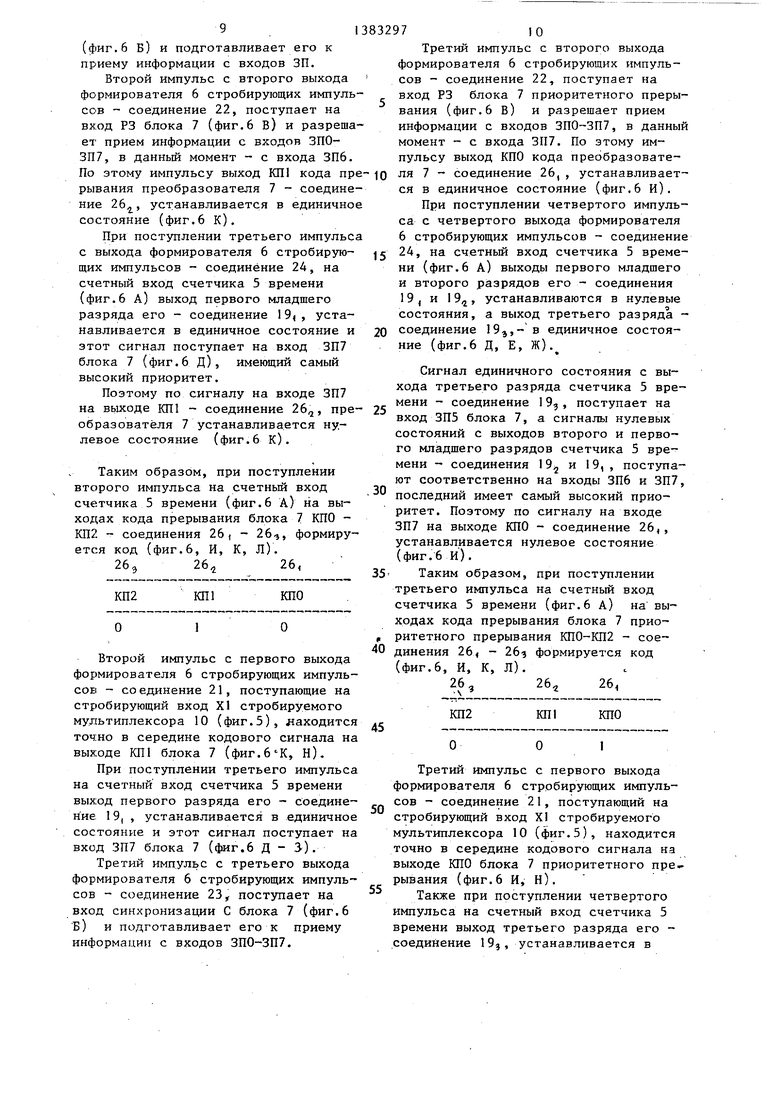

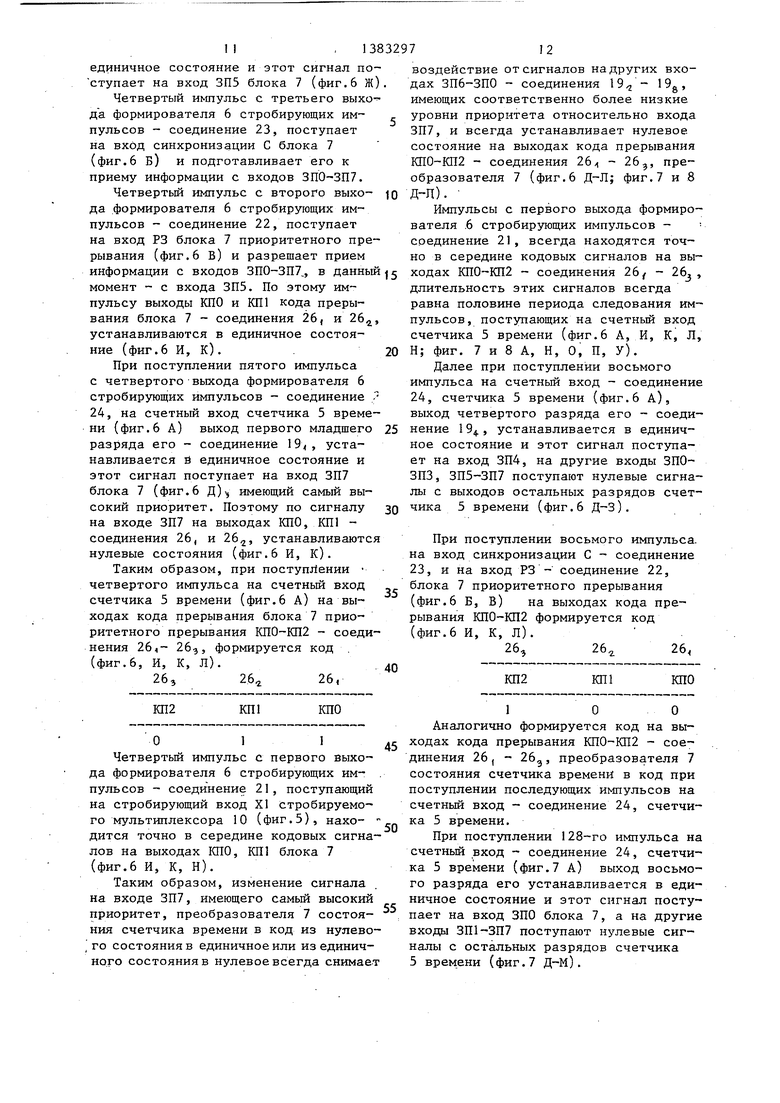

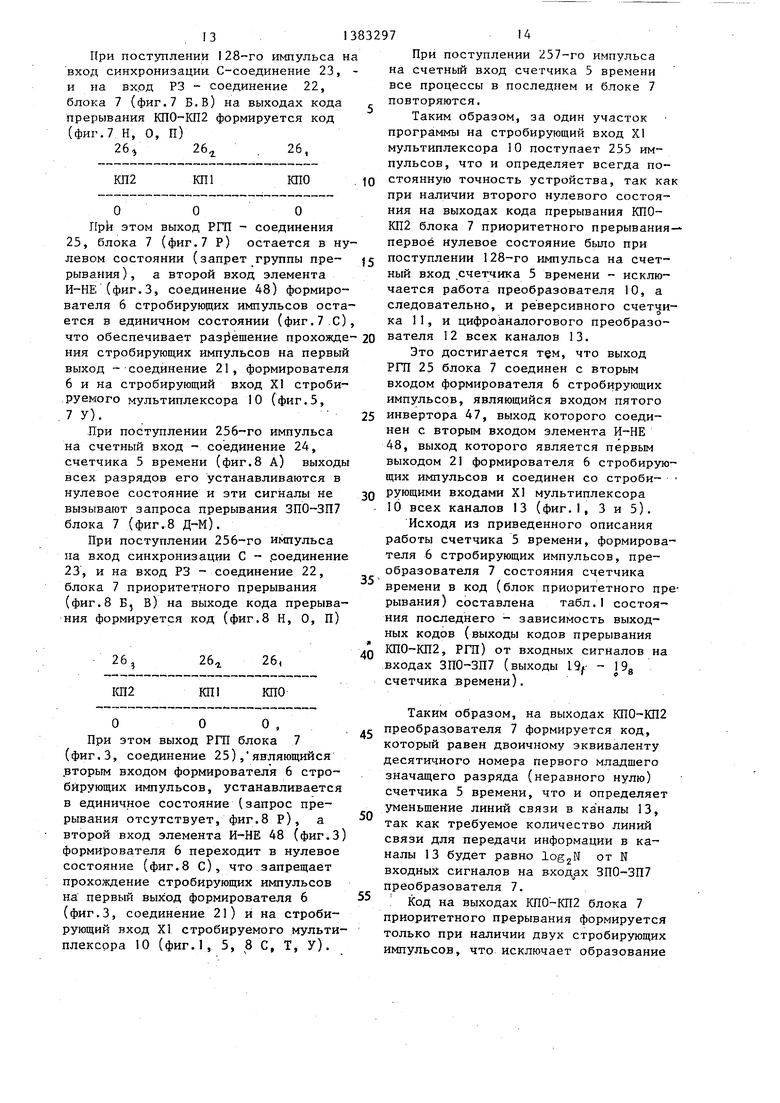

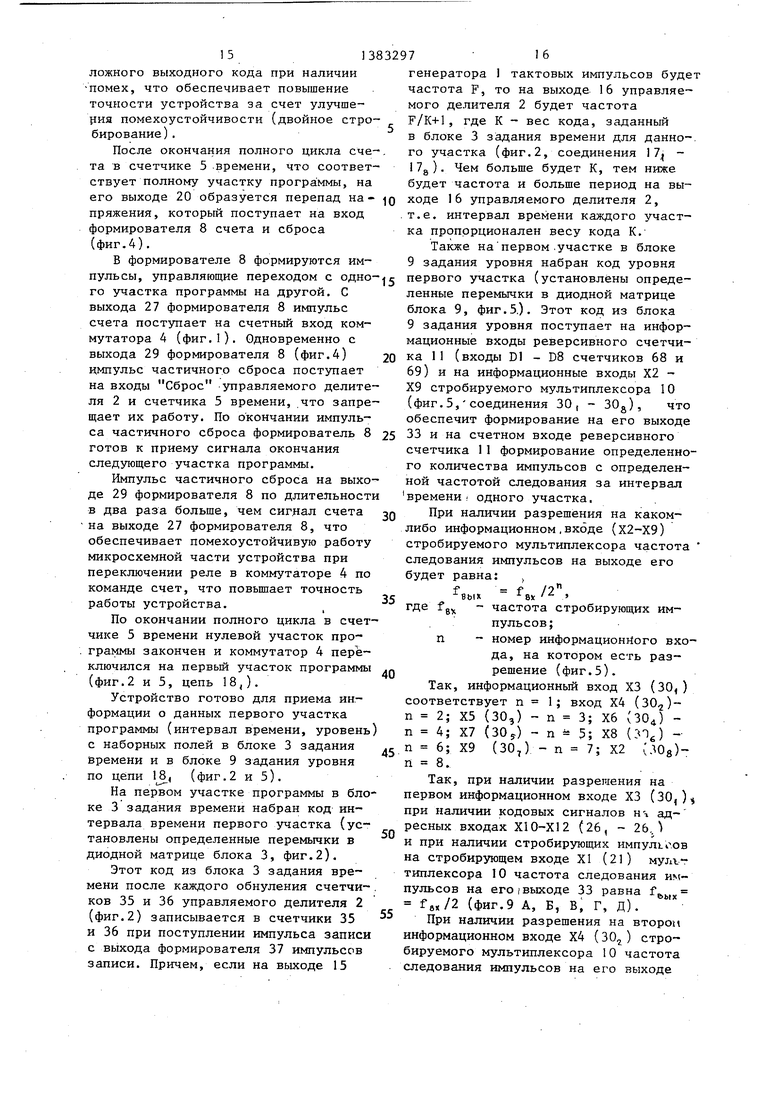

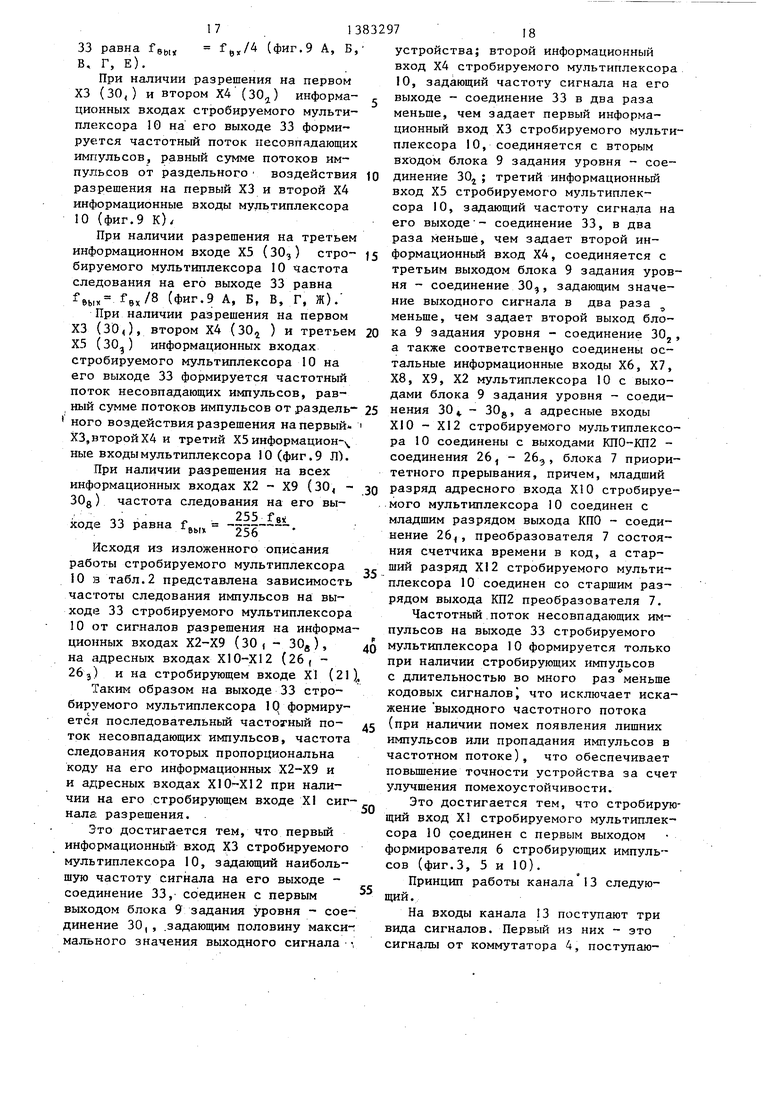

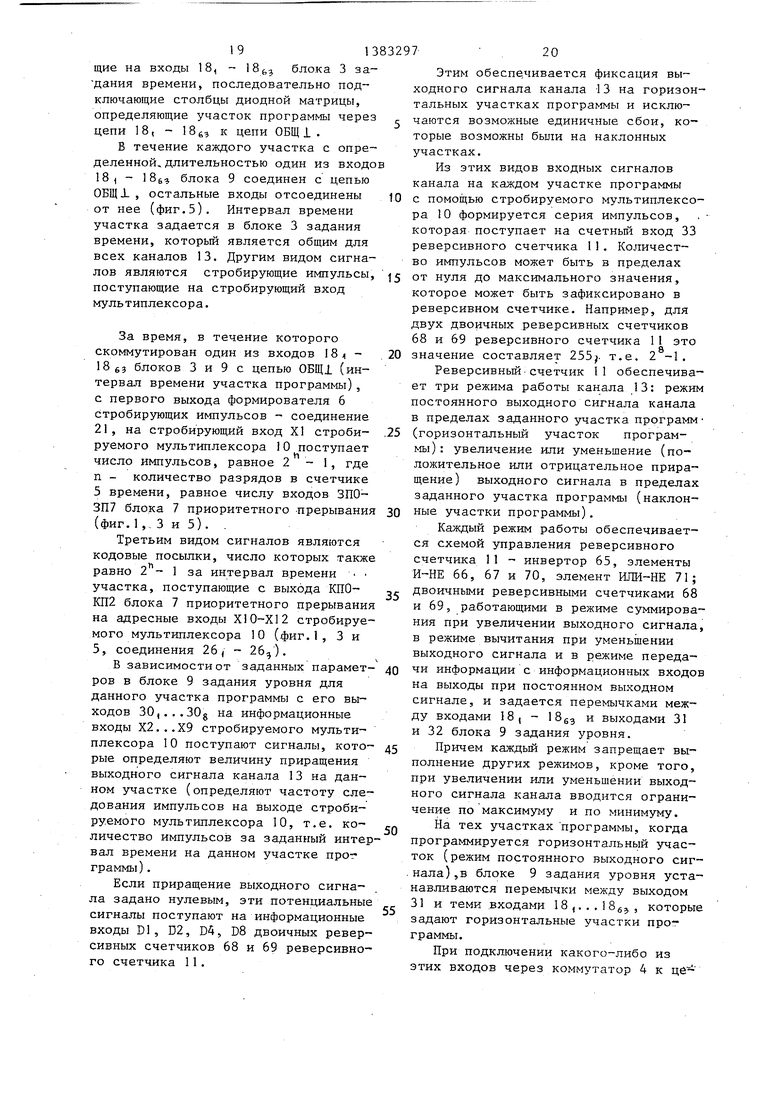

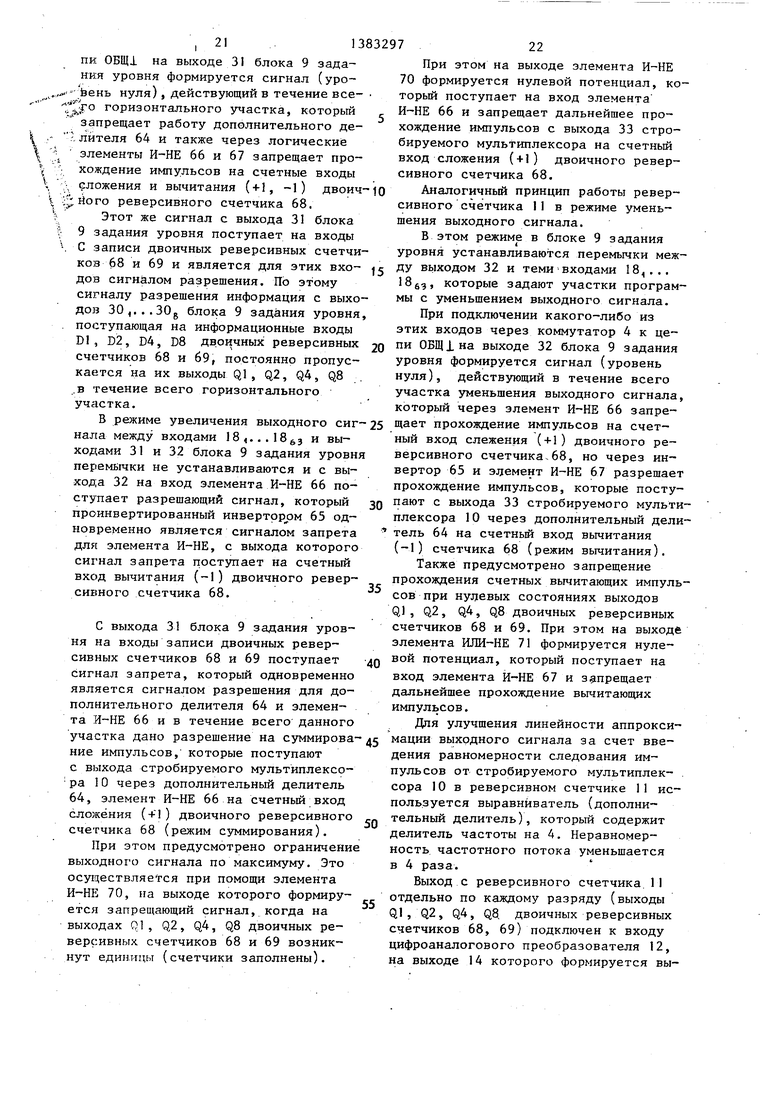

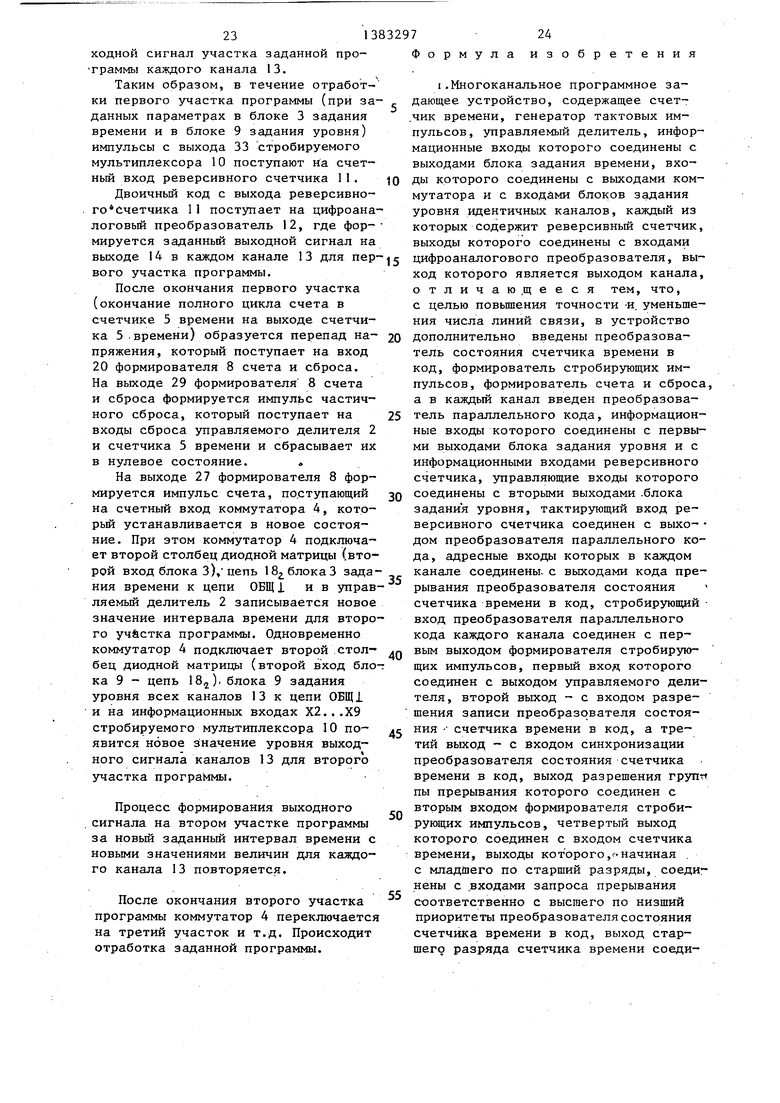

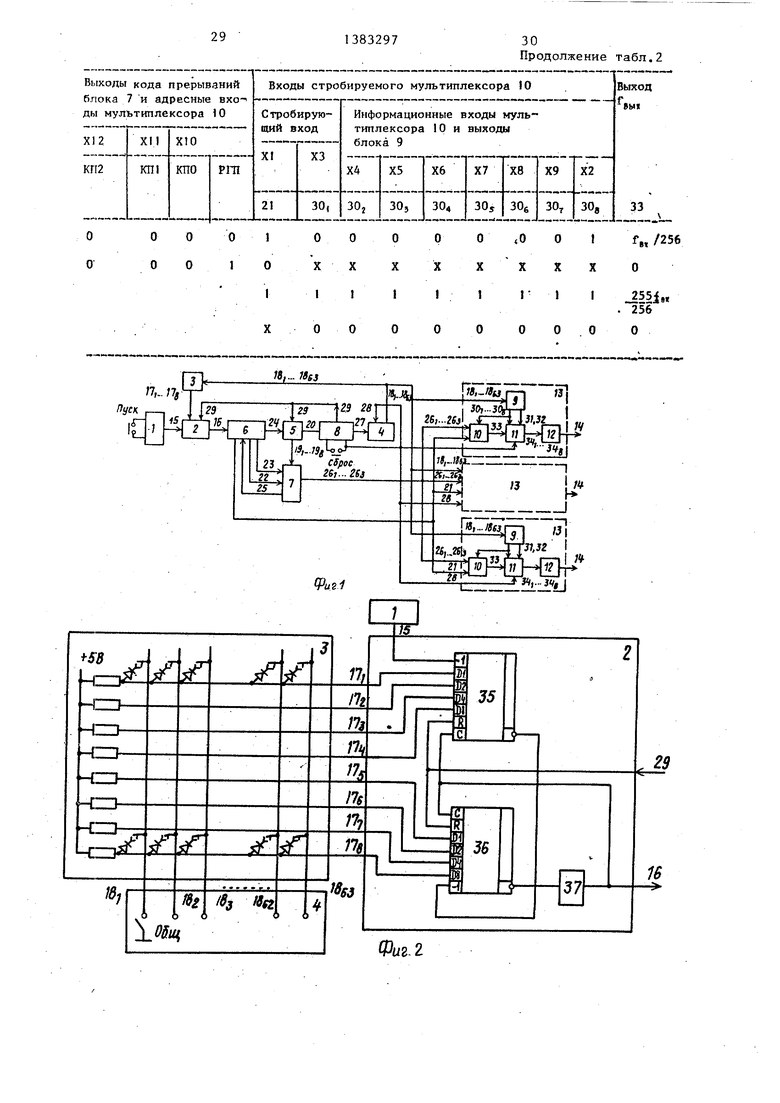

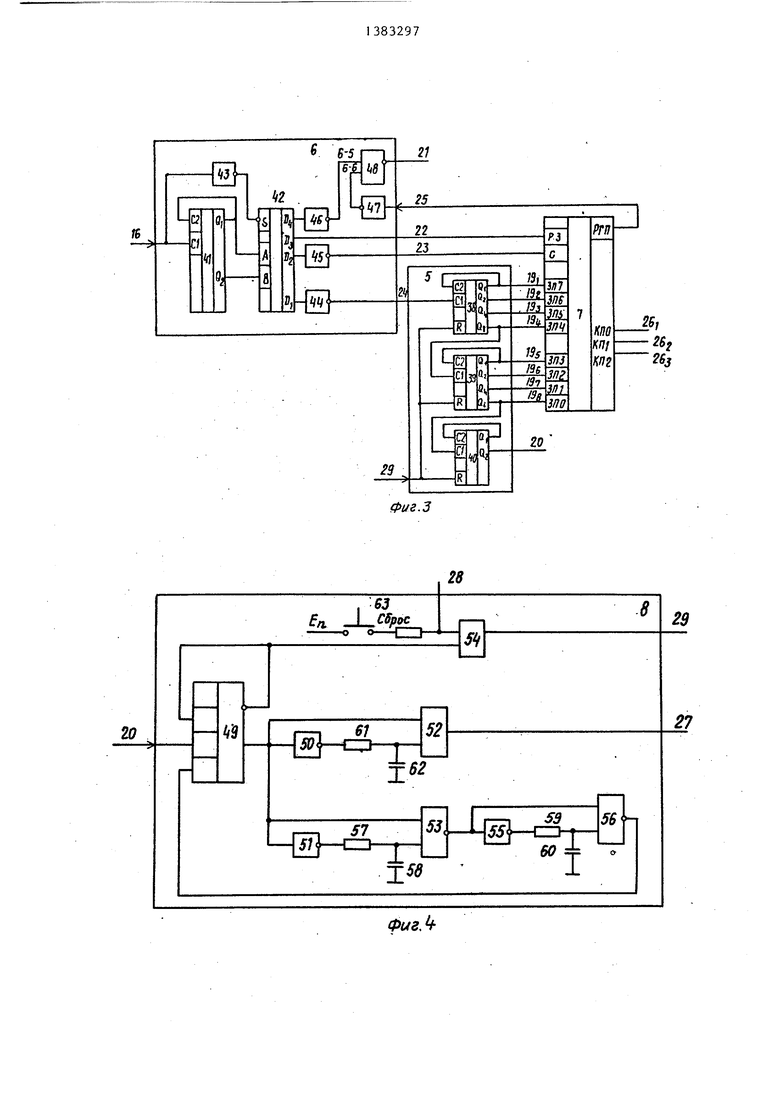

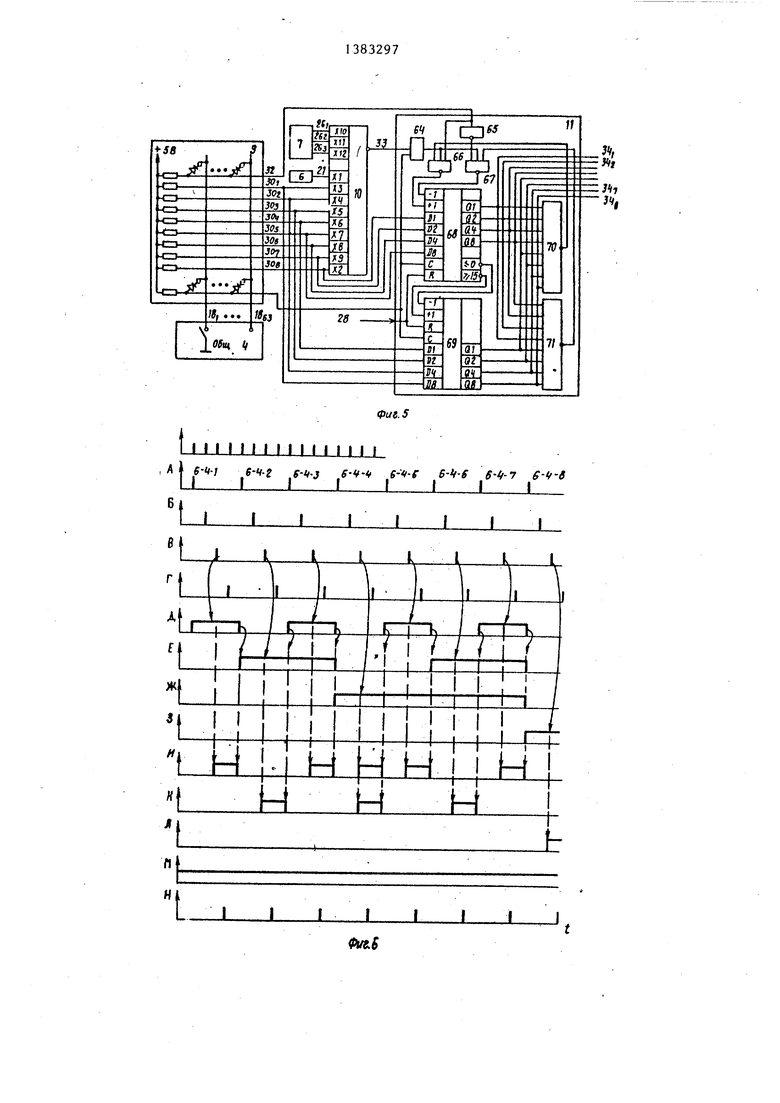

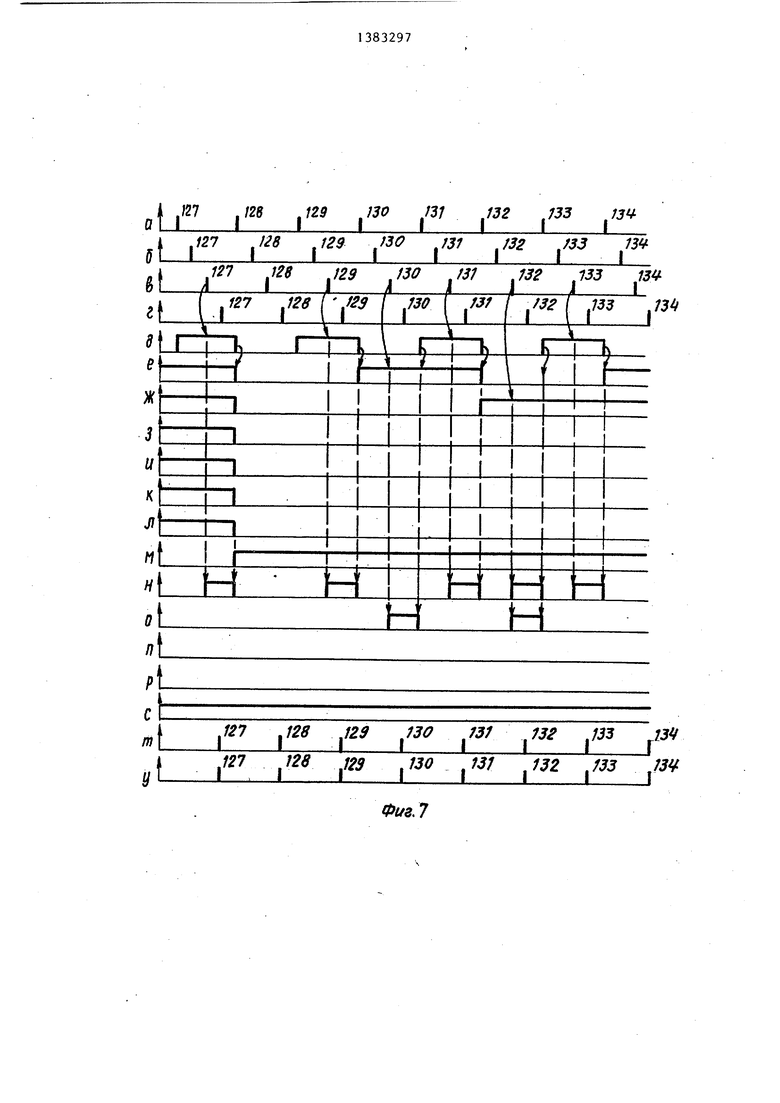

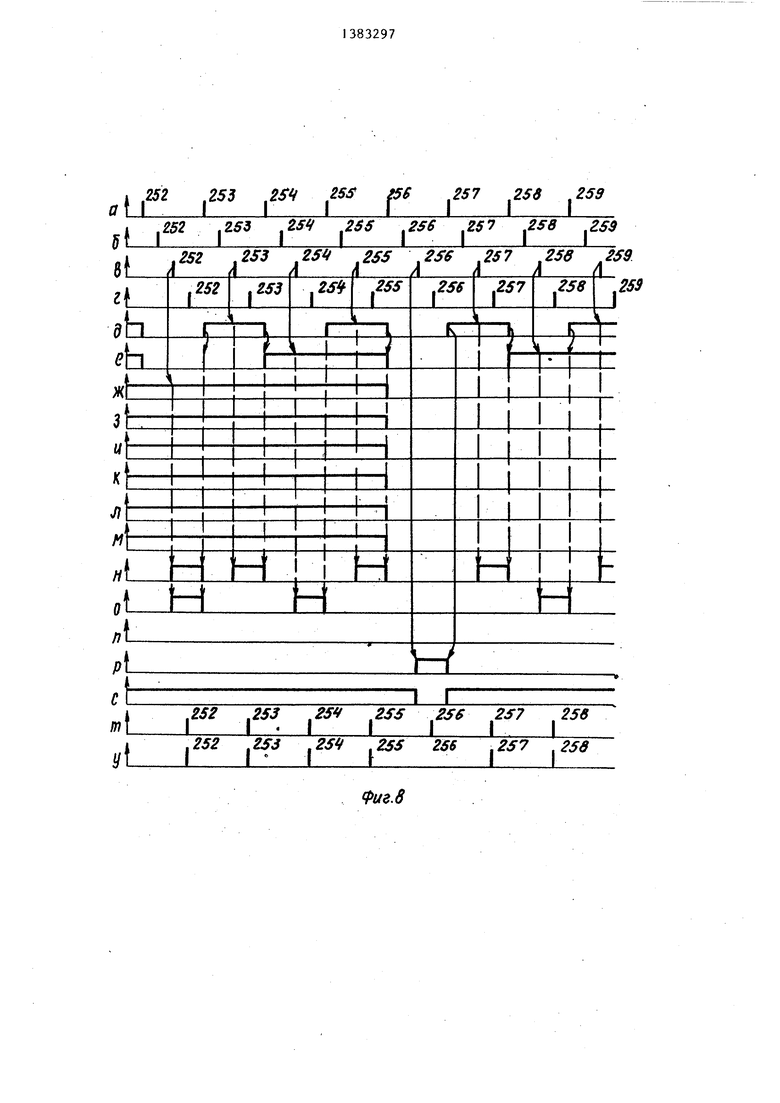

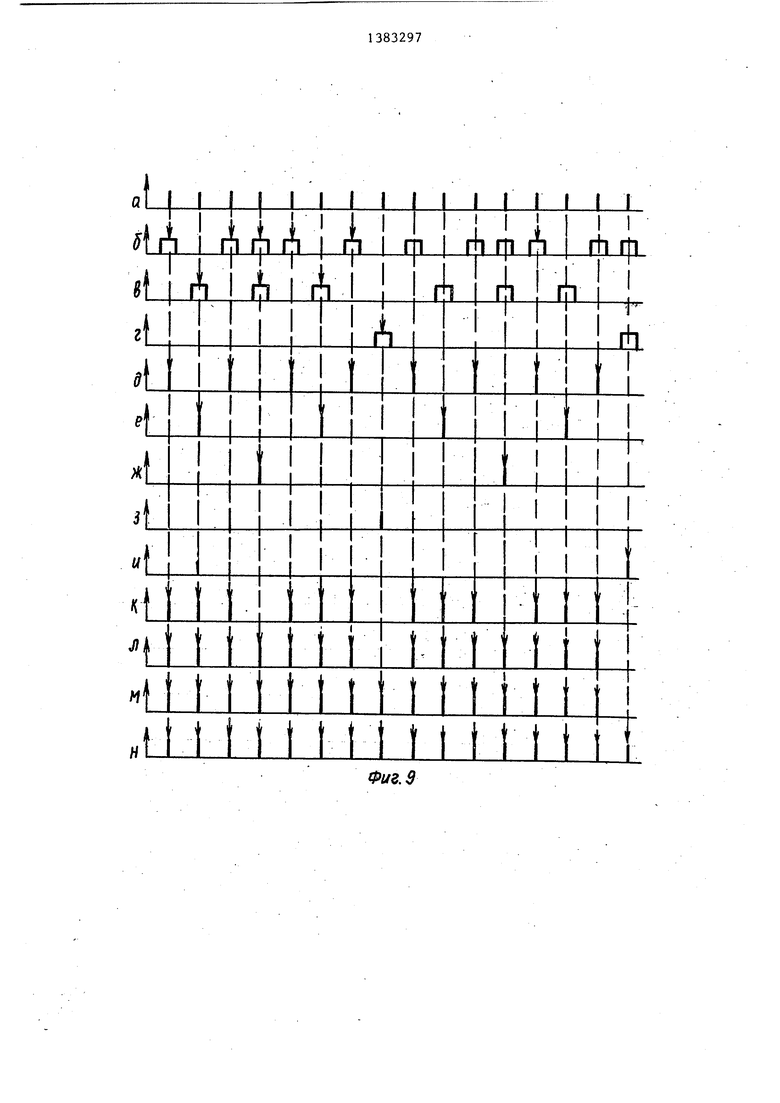

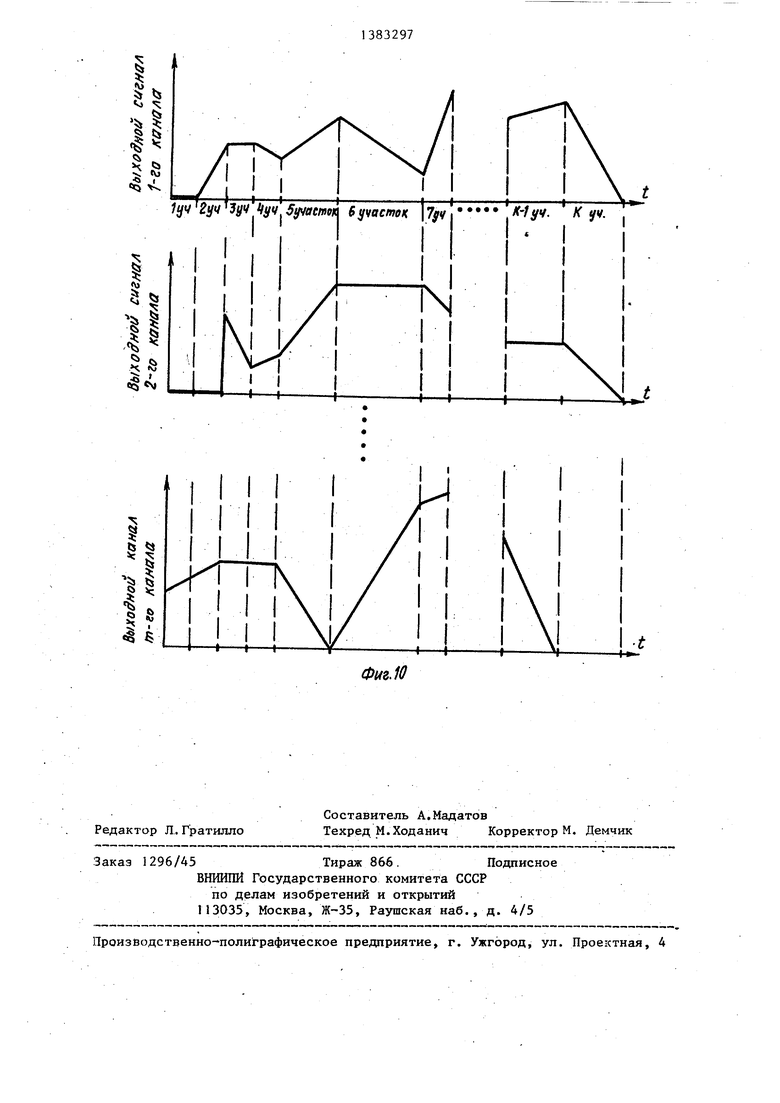

На фиг.1 представлена блок-схема многоканального программного задающего устройства; на фиг.2 - функциональные схемы блока задания времени, управляемого делителя,и их связь: с коммутатором и генератором тактовых импульсов; на фиг.З - функцибнальные схемы формирователя стробирующих импульсов, счетчика времени и их связь с блоком приоритетного прерывания;. на фиг.4 - функциональная схема формирователя счета и сброса; на фиг.З функциональные схемы блока задания уровней, реверсивного счетчика -и связь стробируемого мультиплексора с блоком приоритетного прерывания, формирователем стробирующих импульсов и коммутатором; на фиг.6-8 - временные диаграммы работы счетчика времени, формирователя стробирующих импульсов блока приоритетного прерывания соответственно; на фиг.9 - то же, формирователя стробирующих импульсов, блока приоритетного прерывания, стробируемого мультиплексора; на фиг.10 - вид программ задания выходных сигна- ЛОЕ1 для нескольких каналов.

Устройство (фиг.1) содержит генератор I тактовых импульсов, управляемый делитель 2, блок 3 задания времени, коммутатор 4, счетчик 5 времени, фор1мирователь 6 стробирующих импульсов, преобразователь 7 состояния счетчика времени в код на блоке приоритетного прерывания, формирователь 8 счета и сброса, блок 9 задания уровня, преобразователь 10 параллельного кода на стробируемых мультиплексорах, реверсивный счетчик 11, цифро аналоговый преобразователь 12, канал 3, выход канала 14, кнопки Пуск и Сброс. . ,

На фиг.I обозначены:

соединение 15 - выход генератора 1 тактовых импульсов и вычитающий вход управляемого делителя 2, и соединение 16 - выход последнего и первый вход формирователя 6 стробирующих импульсов;

соединения 17, ...17g - выходы блока 3 задания времени и информационные входы управляемого делителя 2; . соединения 18,... выходы коммутатора 4., входы блока 3 задания времени и блока 9 задания уровня в

каналах 13;

соединения 19,...19g - входы запроса прерывания блока 7 приоритетного прерывания и выходы разрядов счетчика 5 времени, соединение 20 выход последнего разряда счетчика. 5 и вход формирователя 8 счета и сброса;

соединение 21 - стробирующий вход стробируемых мультиплексоров 10 всех

каналов 13 и первый выход формирователя 6 стробирующих импульсов, его второй и третий выходы 22 и 23 соединены соответственно с входом разрешения записи и входом синхронизации

блока 7 приоритетного прерывания;

соединение 24 - счетный вход счетчика 5 времени и четвертый выход формирователя 6 стробирующих импульсов, а соединение 25 - его второй

вход и выход разрешения группы прерывания блока 7 приоритетного прерывания, соединения 26,...26j - выходы кода прерывания последнего и адресные входы стробируемых мультиплексо-

ров 10 каналов 13;

соединение 27 - счетный вход коммутатора 4 и первый выход формирователя 8 счета и сброса, соединение 28 его второй вход и входы сброса ком-

мутатора 4, реверсивных счетчиков 11 каналов 13, а соединение 29 - третий выход формирователя 8 и входы сброса управляемого делителя 2 и счетчика 5 времени;

соединения 30,...30д - информационные входы стробируемого мультиплексора 10 и соответствующего выхода блока 9 задания уровня, а соединения 31 и 32 - его выходы записи и

знака и соответствующие входы реверсивного счетчика 11, счетный вход которого обозначен 33 как связь с вы- ходом стробируемого мультиплексора 10;

соединения 34...348 - выходы разрядов реверсивного счетчика 1 1 и входы - ифpoaнaлoгoвoгo преобразователя 12.

На фиг.2 обозначены реверсивные счетчики 35 и 36 импульсов, формирователь 37 импульсов записи кодов, поступающих на информационные входы счетчиков 35 и 36.

На фиг.З обозначены последовательно включенные двоичные счетчики 3840,двухразрядный двоичный счетчик

41,стробируемый дешифратор 42, соответственно первый 43 - пятый 47 ин- верторы, элемент И-НЕ 48. Q

На фиг.4 обозначены триггер 49, первый инвертор 50, второй инвертор 51, элемент И 52, первый элемент И-НЕ 53, элемент ИЛИ 54, третий инвертор 55, второй элемент И-НЕ 56, 5 первая времязадающая цепь 57 и 58, вторая времязадающая цепь 59 и 60, третья времязадающая цепь 61 и 62, кнопка 63 сброса.

f На фиг.5 обозначены делитель 64 20 частоты импульсов на четыре, инвертор 65, элементы И-НЕ 66 и 67, двоичные реверсивные счетчики 68 и 69, импульсов, элемент И-НЕ 70, элемент ИПИ-НЕ 71. 25

Сущность изобретения состоит в применении блока приоритетного прерывания в качестве преобразователя с двойным стробированием состояния счетчика времени в код, который равен 30 двоичному эквиваленту десятичногр номера первого младшего значащего разряда (не равного нулю) состояния счетчика времени, причем первый вход

а старший разряд - с старшим разр дом кода прерывания блока приорит ного прерывания.

Многоканальное программное зад щее устройство работает следующим образом.

Перед началом работы в блоке (фиг.1 и 2) задания времени при мощи перемычек на шинах 18 ,...18б (фиг.2), соединенных с коммутатор 4, устанавливаются коды заданных тервалов времени для каждого учас программы, общие для всех каналов

Время кодируется двумя тетрада младшая - шины 17....174, связанн с информационньми входами D1 ...D8 реверсивного счетчика 35, старшая шины 1 7 . . . 1 7g , связанные с инфо мационными входами D1...D8 ревер ного счетчика 36 управляемого дел теля 2.

В каждом канале 13 в блоках 9 задания уровня (фиг.1 и 5) при по щи перемычек на шинах 18..., соединенных с коммутатором 4, уст навливаются коды заданных амплиту уровня в каждом канале 13. Амплит Кодируется следующим образом.

Для горизонтальных участков пр граммы перемычка устанавливается шине 31 и двоичный код амплитудыремычками на шинах 30,. ..30g. Для наклонных 5гчастков перемычка на ш

запроса прерывания блока приоритетно-эс устанавливается, а знак

го прерывания, имеющий самый высокий приоритет, соединен с выходом первого разряда счетчика времени, следующий второй вход запроса прерывания блока приоритетного прерывания 40 соединен с выходом второго разряда времени и соответственно остальные выходы разрядов счетчика времени соединены с входами запроса прерывания блока приоритетного преры- 45 вания, причем выход старшего восьмого разряда соединен с входом запроса прерывания, имеющий самый низкий приоритет, а выходы кода прерываний блока приоритетного прерывания, числоCQ которых равно log, N от N входных сигналов на входах запроса прерывания, соединяются с адресными входами стробируемого мультиплексора каждого- канала, причем младший разряд выхода ее кода прерывания блока приоритетного прерывания соединяется с младшим разрядом адресных входов стробируе- мого мультиплексора каждого канала.

наклона определяется перемычкой н шине 32. Подъем программы (увелич ние выходного сигнала канала), - е нет перемычки на шине 32, спуск (уменьшение выходного сигнала кан наличие перемычки на шине 32.

Количество участков программы выходы. 184...18,- коммутатора 4

/

(фиг.1, 2 и 5) .- зависит от коли ва релейных триггеров с памятью в коммутаторе 4.

После установки заданных значе интервалов времени и амплитуд на устройство подается питание и осу ствляется сброс на нуль всех счет узлов устройства кнопкой Сброс цепи 28 и 29.

Счетчик 5 времени и управляемы делитель 2 сбрасываются на нуль п входу 29 и сигнал поступает (фиг. на R вход реверсивных счетчиков 3 36 (фиг.2). и счетчиков 38-40 (фиг.З).

а старший разряд - с старшим разрядом кода прерывания блока приоритетного прерывания.

Многоканальное программное задающее устройство работает следующим образом.

Перед началом работы в блоке 3 (фиг.1 и 2) задания времени при помощи перемычек на шинах 18 ,...18бз (фиг.2), соединенных с коммутатором 4, устанавливаются коды заданных интервалов времени для каждого участка программы, общие для всех каналов 13

Время кодируется двумя тетрадами: младшая - шины 17....174, связанные с информационньми входами D1 ...D8 реверсивного счетчика 35, старшая - шины 1 7 . . . 1 7g , связанные с информационными входами D1...D8 реверсивного счетчика 36 управляемого делителя 2.

В каждом канале 13 в блоках 9 задания уровня (фиг.1 и 5) при помощи перемычек на шинах 18..., соединенных с коммутатором 4, устанавливаются коды заданных амплитуд уровня в каждом канале 13. Амплитуда Кодируется следующим образом.

Для горизонтальных участков программы перемычка устанавливается на шине 31 и двоичный код амплитудыпе- ремычками на шинах 30,. ..30g. Для наклонных 5гчастков перемычка на ши-

наклона определяется перемычкой на шине 32. Подъем программы (увеличение выходного сигнала канала), - если нет перемычки на шине 32, спуск (уменьшение выходного сигнала канала) наличие перемычки на шине 32.

Количество участков программы - выходы. 184...18,- коммутатора 4

/

(фиг.1, 2 и 5) .- зависит от количесва релейных триггеров с памятью в коммутаторе 4.

После установки заданных значений интервалов времени и амплитуд на устройство подается питание и осуществляется сброс на нуль всех счетных узлов устройства кнопкой Сброс по цепи 28 и 29.

Счетчик 5 времени и управляемый делитель 2 сбрасываются на нуль по входу 29 и сигнал поступает (фиг.2) на R вход реверсивных счетчиков 35 и 36 (фиг.2). и счетчиков 38-40 (фиг.З).

513

Сигнал сброса вырабатывается в формирователе 8 (фиг.4) импульсов счета и сброса при нажатии кнопки Сброс. Этот сигнал поступает непосредственно через резисторы на вход Сброс 28 коммутатора 4 и сбрасывает его в исходное состояние..

Этот же сигнал Сброс 28 посту пает во все каналы 13 на реверсивные счетчики 11 (на вход R счетчиков 68 и 69, фиг.5)..

После этого осуществляется запуск устройства кнопкой Пуск (фиг.1). При этом генератор 1 тактовых импульсов начинает работать и импульсы с его выхода I5 поступают на управляемый делитель 2, на вычитающий вход - 1 реверсивного счетчика 35 (фиг.2). На выходе О счетчика 35 появляется сигнал, которьй поступает на вычитающий вход - 1 счетчика 36. С выхода 6 О последнего сигнал проходит на вход формирователя 37 импульсов записи, далее сформированный импульс за- писи поступает на вход записи С счетчиков 35 и 36 и по заднему фронту записывается нулевое значение сигналов на входах D1, D2, D4, D8 обоих счетчиков (входы счетчиков 35 и 36 соединены с блоком 3 задания времени через инверторы, которые на фиг.2 не показаны).

На нулевом участке программы коммутатор 4 (фиг.2) не подключен к блоку задания времени. Этот участок имеет минимальное время, возможное в устройстве (1 с), и выполняет функции динамического контроля всех блоков устройства после первоначального сброса.

Нулевой участок занимает очень короткое время, так как счетчики 35 и 36 в начальном положении все время записывают нулевое значение, и частота импульсов на его выходе равна частоте импульсов от генератора 1 тактовых импульсов.

С выхода управляемого делителя 2 (соединение 16, фиг.2) импульсы поступают на первый вход формирователя 6 стробирующих импульсов (соединение 16, фиг.З), который также является счетным входом С1 двухразрядного дво- ичного счетчика 41 и входом первого инвефтура 43. ,

Двоичный двухразрядный код с выходов первого и второго разрядов QI и Qi счетчика 41 поступает соответст

10

15

20

25.

30

венно на входы первого и второго разрядов А и В стробируемого дешифратора 42, на стробирующий вход Б которого поступают импульсы с выхода первого инвертора 43.

На выходах дешифратора 42 формируются четыре параллельные унитарные последовательности импульсов, которые последовательно сдвинуты во времени друг относительно друга на период следования входных импульсов и с частотой следования в четыре раза меньше входной частоты импульсов формирователя 6, а длительность импульсов равна длительности импульсов на стробирующем входе S дешифратора 42.

Сигналы на выходах стробируемого дешифратора 42 формируются только при наличии стробирующего импульса на стробирующем входе S дешифратора.

Далее последовательность импульсов с выхода D1 дешифратора 42 через инвертор 44, выход которого является четвертым выходом формирователя 6 стробирующих импульсов (соединение 24), поступает на счетный вход счетчика 5 времени - счетный вход СI двоичного счетчика 38 (фиг.6 А).

Последовательность импульсов с выхода дешифратора 42 через инвертор 45, выход которого является третьим выходом формирователя 6 стробирующих импульсов (соединение 23), поступает на вход синхронизации С блока 7 приоритетного прерывания (фиг.6 Б).

Последовательность импульсов с выхода дешифратора 42, который являет- ся вторым выходом формирователя 6 стробирующих импульсов - соединение 22, поступает на вход разрешения записи (РЗ) блока 7 (фиг.6 в).

Последовательность импульсов с четвертого выхода D4 дешифратора

%2 через четвертый инвертор 46 поступает на первый вход элемента И-НЕ 48 (фиг.6 Г).

Сигнал на втором входе элемента И-НЕ 48 разрешает его работу при отсутствии сигнала разрешения группы прерывания (РГП) - соединение 25, блока 7 приоритетного прерывания.

Сигнал на втором входе элемента И-НЕ 48, разрешающий работу, поступает с выхода пятого инвертора 47, вход которого является вторым входом формирователя 6 стробирующих импульсов и выходом РГП блока 7 - соединение 25. При наличии сигнала разрешения

40

45

50

на втором входе элемента И-НЕ 48 последовательность импульсов с перво го выхода 21 формирователя 6 строби- ругощих импульсов поступает на строби рующий вход XI стробируемых мультиплексоров 10 всех каналов 13 (фиг.1 и 5; 6 Г, М, Н).

С выходов 19 ,...19д счетчика 5 времени (фиг.З) двоичный код поступа ет на входы ЗПО-ЗП7 блока 7 приоритетного прерывания, причем код с выхода, первого младшего разряда счетчика 5 времени - соединение 19, (выход Q двоичного счетчика 38), поступает на вход ЗП7 блока приоритетного прерывания, имеющий самый высокий, приоритет, и соответственно коды остальных разрядов счетчика 5 времени - соединение 19j..,19g (выходы

Q2 Q. Qe QI. Qa 34, Qg двоичных счетчиков 38 и 39), поступают на входы ЗПб-ЗПО блока 7, причем код с выхода старшего восьмого разряда - соединение 19g, поступает на вход ЗПО, имеющий самый низкий приоритет.

Кодовые сигналы с выходов кода прерываний КПО-КП2 блока 7 приоритет ного прерывания - соединение 26,- 265, поступают на адресные входы XIО XI2 стробируемых мультиплексоров 10 каналов 13 (фиг,1 и 5), причем кодо вые сигналы с выхода КПО младшего разряда кода прерывания блока 7 - соединение 26,, поступают на вход XIО младшего разряда адресных входов мультиплексоров 10 каналов 13,

Кодовые сигналы с выхода КП1 кода прерь/Вания блока 7 - соединение 26j поступают на вход XI1 первого разряда адресных входов мультиплексоров 10 каналов 13, а кодовые сигналы с выхода КП2 старшего разряда кода прерываний блока 7 - соединение 26,, поступают на вход Х52 старшего разряда адресных входов стробируемых мультиплексоров 10 каналов 13.

При поступлении первого импульса с четвертого выхода формирователя 6 стробирующих импульсов - соединение 24 (фиг.3)4 на счетный вход счетчика 5 времени (фиг,6 А) выход первого младшего разряда его - соединение 19,, устанавливается в единичное состояние и этот сигнал поступает на вход 3II7 блока 7 приоритетного прерывания (фиг.6 Д). Первый импульс с третьего выхода формирователя 6 стробирующих импульсов - сое

10

15

20

25

30

динение 23, поступает на вход синхронизации С блока 7 приоритетного прерывания (фиг.6 Б) и подготавливает его к приему информации с входов ЗИО-ЗП7.

Первый импульс с второго выхода формирователя 6 стробирующих импульсов - соединение 22, поступает на вход РЗ блока 7 приоритетного прерывания (фиг.6 в) н разрешает прием информации с входов ЗПО-ЗП7, в данный момент - с входа ЗП7.

По этому импульсу выход КПО младшего разряда кода прерывания блока 7 - соединение 26,, устанавливается в единичное состояние (фиг.6 И).

При поступлении второго импульса с четвертого выхода формирователя 6 стробирующих импульсов - соединение 24, на счетный вход счетчика 5 времени (фиг.6 А) выход первого младшего разряда его - соединение 19 , и вход ЗП7 блока 7 устанавливаются в нулевые состояния.

При этом выход КПО младшего разряда кода прерывания также устанавливается в Нулевое состояние (фиг.6 И).

Таким образом, при поступлении первого импульса на счетный вход счетчика 5 времени (фиг.6 А) на выходах кода прерывания блока 7 КПО-КП2 - соединения 26,- 26, формируется код (фиг.6. И, К, л).

Первый импульс с первого выхода формирователя 6 стробирующих импуль- сов - соединение 21 , поступающий на стробирующий вход XI стробируемого мультиплексора 10 (фиг.З), находится точно в середине кодового сигнала на выходе КПО блока 7 .приоритетного прерывания (фиг.6 И, H)V

Также при поступлении второго импульса на счетный вход счетчика 5 времени выход второго разряда его - соединение 19, устанавливается в единичное состояние и этот сигнал поступ ает на вход ЗПб блока 7 приори-- тетного прерывания (фиг.6 Е).

Второй импульс с третьего выхода формирователя 6 стробирующих импульсов - соединение 23, поступает на вход синхронизации С блока 7

(фиг,6 Б) и подготавливает его к приему информации с входов ЗП.

Второй импульс с второго выхода формирователя 6 стробирующих импульсов - соединение 22, поступает на вход РЗ блока 7 (фиг.6 В) и разрешает прием информации с входов ЗПО- ЗП7, в данный момент - с входа ЗПб. По этому импульсу выход КП1 кода прерывания преобразователя 7 - соединение 26, устанавливается в единичное состояние (фиг.6 К).

При поступлении третьего импульса с выхода формирователя 6 стробирующих импульсов - соединение 24, на счетный вход счетчика 5 времени (фиг.6 А) выход первого младшего разряда его - соединение 19 , устанавливается в единичное состояние и этот сигнал поступает на вход ЗП7 блока 7 (фиг.6 Д), имеющий самый высокий приоритет.

Поэтому по сигналу на входе ЗП7 на выходе КП1 - соединение 26, преобразователя 7 устанавливается нулевое состояние (фиг.6 К).

Таким образом, при поступлении второго импульса на счетный вход счетчика 5 времени (фиг.6 А) на выходах кода прерывания блока 7 КПО - КП. - соединения 26, - 26,, формируется код (фиг.6, И, К, л).

Второй импульс с первого выхода фор мирователя 6 стробирующих импуль- COEI - соединение 21, поступающие на стробирующий вход XI стробируемого мультиплексора 10 (фиг.5), лаходится точно в середине кодового сигнала на выходе КП1 блока 7 (фиг., Н),

При поступлении третьего импульса на счетный вход счетчика 5 времени выход первого разряда его - соедине- н ие 19| , устанавливается в единичное состояние и этот сигнал поступает на вход ЗП7 блока 7 (фиг,6 Д - 3).

Третий импульс с третьего выхода формирователя 6 стробирующих импульсов - соединение 23, поступает на вход синхронизации С блока 7 (фиг.6 Б) и подготавливает его к приему информации с входов ЗПО-ЗП7.

Третий импульс с второго выхода формирователя 6 стробирующих импульсов - соединение 22, поступает на вход РЗ блока 7 приоритетного прерывания (фиг.6 в) и разрешает прием информации с входов ЗПО-ЗП7, в данный момент - с входа ЗП7. По этому импульсу выход КПО кода преобразовате0 ля 7 - соединение 26,, устанавливается в единичное состояние (фиг.6 И).

При поступлении четвертого импульса с четвертого выхода формирователя 6 стробирующих импульсов - соединение

5 24, на счетный вход счетчика 5 времени (фиг.6 А) выходы первого младшего и второго разрядов его - соединения 19, и 19, устанавливаются в нулевые состояния, а выход третьего разряда 0 соединение 19,- в единичное состоя- . ние (фиг.6 Д, Е, Ж).

Сигнал единичного состояния с выхода третьего разряда счетчика 5 вре- мени - соединение 19,, поступает на вход ЗП5 блока 7, а сигналы нулевых состояний с выходов второго и первого младшего разрядов счетчика 5 времени - соединения 19 и 19,, поступают соответственно на входы ЗП6 и ЗП7, последний имеет самый высокий приоритет. Поэтому по сигналу на входе ЗП7 на выходе КПО - соединение 26,, устанавливается нулевое состояние (фиг.6 и).

5- Таким образом, при поступлении третьего импульса на счетный вход счетчика 5 времени (фиг.6 А) на выходах кода прерывания блока 7 прио- ритетного прерывания КПО-КП2 - сое- 0 динения 26, - 26 формируется код (фиг.6, И, К, Л),

0

Третий импульс с первого выхода формирователя 6 стробирующих импульсов - соединение 21, поступающий на стробирующий вход XI стробируемого мультиплексора 10 (фиг.5), находится точно в середине кодового сигнала на выходе КПО блока 7 приоритетного прерывания (фиг.6 И, Н).

Также при поступлении четвертого импульса на счетный вход счетчика 5 времени выход третьего разряда его - соединение 19}, устанавливается в

0

единичное состояние и этот сигнал по- ступает на вход ЗП5 блока 7 (фиг.6 Ж)

Четвертый импульс с третьего выхо- да формирователя 6 стробирующих импульсов - соединение 23, поступает на вход синхронизации С блока 7 (фиг.6 Б) и подготавливает его к приему информации с входов ЗПО-ЗП7.

Четвертый импульс с второг о выхода формирователя 6 стробирующих импульсов - соединение 22, поступает на вход РЗ блока 7 приоритетного прерывания (фиг.6 в) и разрешает прием

воздействие от сигналов на других входах ЗП6-ЗПО - соединения 19.2 s имеющих соответственно более низкие уровни приоритета относительно входа 3II7, и всегда устанавливает нулевое состояние на выходах кода прерывания КПО-К112 - соединения 26 - 26,, преобразователя 7 (фиг.6 Д-Л; фиг.7 и 8

д-л).

Импульсы с первого выхода формирователя .6 стробирующих импульсов - соединение 21, всегда находятся точно в середине кодовых сигналов на вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1290304A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Цифровой измеритель ускорения вала | 1991 |

|

SU1791781A1 |

| Устройство для ввода информации | 1982 |

|

SU1048465A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Линейно-круговой интерполятор | 1987 |

|

SU1462250A2 |

| Линейно-круговой интерполятор | 1986 |

|

SU1312530A1 |

| Устройство для управления возбудителем механических колебаний | 1983 |

|

SU1137451A1 |

| Устройство для сопряжения абонентов с магистралью | 1986 |

|

SU1361570A1 |

Изобретение.относится к автоматическому регулированию и может быть использовано в устройствах управления производственными процессами по заранее заданной программе одновременно по нескольким каналам управления. Целью изобретения является по- вьшение точности многоканального программного задающего устройства, уменьшение числа линий связи. В многоканальное программное задающее устройство, состоящее из счетчика времени, генератора тактовых импульсов, управляемого делителя, коммута- тора и нескольких каналов, каждый из которых содержит реверсивный счетчик, блок задания уровня и цифро- аналоговый преобразователь, дополнительно введены преобразователь состояния счетчика времени в код, формирователь стробирующих импульсов, формирователь счета и сброса, а в каждый канал - преобразователь параллельного кода. В данном устройстве достигается обеспечение жесткой синхронизации работы блоков устройства с помощью формирователя стробирующих импульсов. Сущность изобретения заключается в использовании блока приоритетного прерывания в качестве управляемого шифратора состояния счетчика времени, что позволяет сократить число линий связи в устройстве. 4 з.п. ф-лы, 10 ил., 2 табл. Ф (Л

информации с входов ЗПО-ЗП7., в данный 5 ходах КПО-КП2 - соединения 26 - 26, момент - с входа ЗП5. По этому импульсу выходы КПО и КП1 кода прерывания блока 7 - соединения 26, и 26, устанавливаются в единичное состояние (фиг.6 И, к).

При поступлении пятого импульса с четвертого выхода формирователя 6 стробирующих импульсов - соединение Я

длительность этих сигналов всегда равна половине периода следования импульсов, поступающих на счетный вход счетчика 5 времени (фиг.6 А, И, К, Л, 20 Н; фиг. 7 и 8 А, Н, О, П, У).

Далее при поступлении восьмого импульса на счетный вход - соединение 24, счетчика 5 времени (фиг.6 А), выход четвертого разряда его - соедиДалее при поступлении восьмого импульса на счетный вход - соединени 24, счетчика 5 времени (фиг.6 А), выход четвертого разряда его - соеди24, на счетный вход счетчика 5 времени (фиг. 6 А) выход первого младшего 25 нение 194., устанавливается в единич- разряда его - соединение 19, уста- ное состояние и этот сигнал поступа- навливается fl единичное состояние и ет на вход ЗП4, на другие входы ЗПО- этот сигнал поступает на вход ЗП7 блока 7 (фиг.6 Д) имеющий самый выЗПЗ, ЗП5-ЗП7 поступают нулевые сигналы с выходов остальных разрядов счетчика 5 времени (фиг.6 Д-З).

сокий приоритет. Поэтому по сигналу на входе ЗП7 на выходах КПО, КП1 - соединения 26, и 262, устанавливают нулевые состояния (фиг.6 И, К).

Таким образом, при поступлении четвертого импульса на счетньш вход счетчика 5 времени (фиг.6 А) на выходах кода прерывания блока 7 приоритетного прерывания КПО-КП2 - соединения 26,- 26з, формируется код . (фиг.6, И, К, Л).

26,

26,

1Ш2

КП1

КПО

о11

Четвертый импульс с первого выхода формирователя 6 стробирующих им- . пульсов - соединение 21, поступающий на стробирующий вход XI стробируемо- го мультиплексора 10 (фиг.5), нахо- дится точно в середине кодовых сигналов на выходах КПО, КП1 блока 7 (фиг.6 И, К, Н).

Таким образом, изменение сигнала на входе ЗП7, имеющего самый высокий приоритет, преобразователя 7 состояния счетчика времени в код из нулево- го состояния в единичное или из единичного состояния в нулевое всегда снимает

ходах КПО-КП2 - соединения 26 - 26,

длительность этих сигналов всегда равна половине периода следования импульсов, поступающих на счетный вход счетчика 5 времени (фиг.6 А, И, К, Л, Н; фиг. 7 и 8 А, Н, О, П, У).

Далее при поступлении восьмого импульса на счетный вход - соединение 24, счетчика 5 времени (фиг.6 А), выход четвертого разряда его - соединение 194., устанавливается в единич- ное состояние и этот сигнал поступа- ет на вход ЗП4, на другие входы ЗПО-

нение 194., устанавливается в единич- ное состояние и этот сигнал поступа- ет на вход ЗП4, на другие входы ЗПО-

ЗПЗ, ЗП5-ЗП7 поступают нулевые сигналы с выходов остальных разрядов счетчика 5 времени (фиг.6 Д-З).

При поступлении восьмого импульса, на вход синхронизации С - соединение 23, и на вход РЗ - соединение 22, блока 7 приоритетного прерывания (фиг.6 Б, в) на выходах кода прерывания КПО-КП2 формируется код (фиг.6 И, К, л).

26,

KITl

26,

гао

5

0

5

1 О О Аналогично формируется код на выходах кода прерывания К110-КП2 - соединения 26, - 26д, преобразователя 7 состояния счетчика времени в код при поступлении последующих импульсов на счетный вход - соединение 24, счетчика 5 времени.

При поступлении 128-го импульса на счетный вход - соединение 24, счетчика 5 времени (фиг.7 А) выход восьмого разряда его устанавливается в единичное состояние и этот сигнал поступает на вход ЗПО блока 7, а на другие входы ЗП1-ЗП7 поступают нулевые сигналы с остальных разрядов счетчика 5 времени (фиг.7 Д-М).

13

При поступлении 128-го импульса на вход синхронизации С-соединение 23, - и на вход РЗ - соединение 22, блока 7 (фиг.7 Б.В) на выходах кода прерывания КПО-КП2 формируется код (фиг.7 Н, О, П)

О

О

О

При этом выход РГП - соединения 25, блока 7 (фиг.7 Р) остается в нулевом состоянии (запрет группы пре- 15 рывания), а второй вход элемента И-НЕ; (фиг. 3, соединение 48) формирователя 6 стробирующих импульсов остается в единичном состоянии (фиг.7.С),

1383297I i

При поступлении Z57-ro импульса на счетный вход счетчика 5 времени все процессы в последнем и блоке 7 повторяются.

Таким образом, за один участок программы на стробирующий вход XI мультиплексора 10 поступает 255 импульсов, что и определяет всегда по- |0 стоянную точность устройства, так как при наличии второго нулевого состояния на выходах кода прерывания КПО- КП2 блока 7 приоритетного прерывания- первое нулевое состояние было при поступлении 128-го импульса на счетный вход .счетчика 5 времени - исключается работа преобразователя 10, а следовательно, и реверсивного счетчика 11, и цифройналогового преобразочто обеспечивает раз13ешение прохожде-20 вателя 12 всех каналов 13. ния стробирующих импульсов на первый выход - соединение 21, формирователя

6и на стробирующий вход XI строби- руемого мультиплексора 10 (фиг.5,

7У).

При поступлении 256-го импульса на счетный вход - соединение 24, счетчика 5 времени (фиг.8 А) выходы всех разрядов его устанавливаются в нулевое состояние и эти сигналы не вызывают запроса прерывания ЗПО-3117 блока 7 (фиг.8 Д-М).

При поступлении 256-го импульса на вход синхронизации С - .соединение 23, и на вход РЗ - соединение 22, блока 7 приоритетного прерывания (фиг.8 Б, в) на выходе кода прерывания формируется код (фиг.8 Н, О, П)

Это достигается тем, что выход РГП 25 блока 7 соединен с вторым входом формирователя 6 стробирующих импульсов, являющийся входом пятого

25 инвертора 47, выход которого соединен с вторым входом элемента И-НЕ 48, выход которого является первым выходом 21 формирователя 6 стробирующих импульсов и соединен со строби-

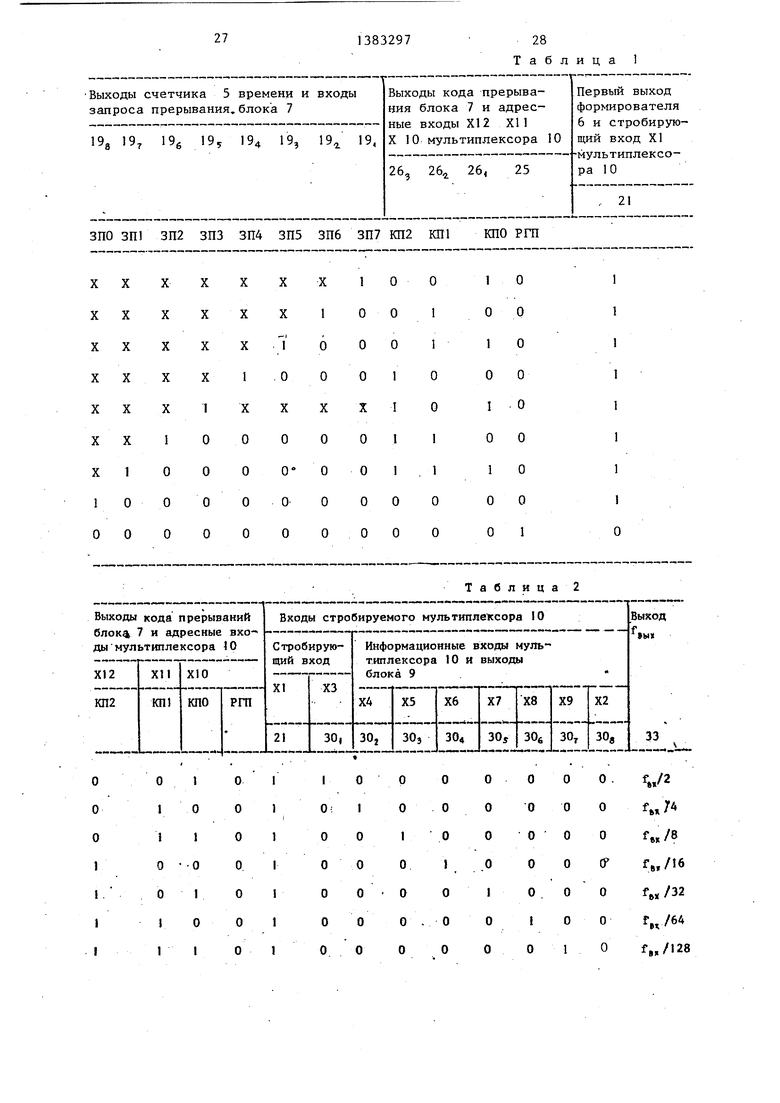

30 Рующими входами XI мультиплексора 10 всех каналов 3 (фиг.1, 3 и 5). Исходя из приведенного описания работы счетчика 5 времени, формирователя 6 стробирующих импульсов, преобразователя 7 состояния счетчика времени в код (блок приоритетного прерывания) составлена табл.1 состояния последнего - зависимость выходных кодов (выходы кодов прерывания КПО-КП2, РГП) от входных сигналов на входах ЗПО-ЗП7 (выходы L9;L- - 9g счетчика времени).

При этом выход РГП блока 7 (фиг.З, соединение 25), являющийся вторым входом формирователя 6 стробирующих импульсов, устанавливается в единичное состояние (запрос прерывания отсутствует, фиг.8 Р), а второй вход элемента И-НЕ 48 (фиг.З) формирователя 6 переходит в нулевое состояние (фиг.8 С), что запрещает прохождение стробирующих импульсов на первый выход формирователя 6 (фиг.З, соединение 21) и на стробирующий вход XI стробируемого мультиплексора 10 (фиг.1, 5, 8 С, Т, у).

вателя 12 всех каналов 13.

Это достигается тем, что выход РГП 25 блока 7 соединен с вторым входом формирователя 6 стробирующих импульсов, являющийся входом пятого

инвертора 47, выход которого соединен с вторым входом элемента И-НЕ 48, выход которого является первым выходом 21 формирователя 6 стробирующих импульсов и соединен со строби-

Рующими входами XI мультиплексора 10 всех каналов 3 (фиг.1, 3 и 5). Исходя из приведенного описания работы счетчика 5 времени, формирователя 6 стробирующих импульсов, преобразователя 7 состояния счетчика времени в код (блок приоритетного прерывания) составлена табл.1 состояния последнего - зависимость выходных кодов (выходы кодов прерывания КПО-КП2, РГП) от входных сигналов на входах ЗПО-ЗП7 (выходы L9;L- - 9g счетчика времени).

Таким образом, на выходах КПО-КП2 преобразователя 7 формируется код, который равен двоичному эквиваленту десятичного номера первого младшего значащего разряда (неравного нулю) счетчика 5 времени, что и определяет уменьшение линий связи в 13, так как требуемое количество линий связи для передачи информации в каналы 13 будет равно от N входных сигналов на входах ЗПО-ЗП7 преобразователя 7.

. Код на выходах КПО-КП2 блока 7 приоритетного прерывания формируется только при наличии двух стробирующих импульсов, что исключает образование

ложного выходного кода при наличии помех, что обеспечивает повышение точности устройства за счет улучше- рия помехоустойчивости (двойное стро- бирование).

После окончания полного цикла счета в счетчике 5 времени, что соответствует полному участку програ:ммы, на его выходе 20 образуется перепад на - пряжения, который поступает на вход формирователя 8 счета и сброса (фиг.4),

В формирователе 8 формируются им10

генератора 1 тактовых импульсов будет частота F, то на выходе 16 управляемого делителя 2 будет частота F/K+1, где К - вес кода, заданньш в блоке 3 задания времени для данно-, го участка (фиг.2, соединения 17 - I7д). Чем больше будет К, тем ниже будет частота и больше период на выходе 16 управляемого делителя 2, т.е. интервал времени каждого участка пропорционален весу кода К.

Также на первом .участке в блоке 9 задания уровня набран код уровня

пульсы, управляющие переходом с одно-.j первого участка (установлены опредего участка программы на другой. С выхода 27 формирователя 8 импульс счета поступает на счетный вход коммутатора 4 (фиг.1). Одновременно с выхода 29 формирователя 8 (фиг.4) импульс частичного сброса поступает на входы Сброс управляемого делителя 2 и счетчика 5 времени, что запрещает их работу. По окончании импуль-

ленные перемычки в диодной матрице блока 9, фиг.5.). Этот код из блока 9 задания уровня поступает на информационные входы реверсивного счетчи- 20 ка 11 (входы D1 - D8 счетчиков 68 и 69) и на информационные входы Х2 - Х9 стробируемого мультиплексора 10 (фиг.5, соединения 30, - 30g), что обеспечит формирование на его выходе

са частичного сброса формирователь 8 25 33 и на счетном входе реверсивного

30

35

готов к приему сигнала окончания следующего участка программы.

Импульс частичного сброса на выходе 29 формирователя 8 по длительности в два раза больше, чем сигнал счета на выходе 27 формирователя 8, что обеспечивает помехоустойчивую работу микросхемной части устройства при переключении реле в коммутаторе 4 по команде счет, что повьшгает точность работы устройства.

По окончании полного цикла в счетчике 5 времени нулевой участок про- граммы закончен и коммутатор 4 переключился на первый участок программы .,. (фиг.2 и 5, цепь 18,).

Устройство готово для приема информации о данных первого участка программы (интервал времени, уровень) с наборных полей в блоке 3 задания времени и в блоке 9 задания уровня по цепи 18, (фиг.2 и 5).

На первом участке программы в блоке 3 задания времени набран код интервала времени первого участка (установлены определенные перемычки в диодной матрице блока 3, фиг.2).

Этот код из блока 3 задания времени после каждого обнуления счетчи- . ков 35 и 36 управляемого делителя 2 (фиг.2) записывается в счетчики 35 и 36 при поступлении импульса записи с выхода формирователя 37 импульсов записи. Причем, если на выходе 15

45

50

55

генератора 1 тактовых импульсов будет частота F, то на выходе 16 управляемого делителя 2 будет частота F/K+1, где К - вес кода, заданньш в блоке 3 задания времени для данно-, го участка (фиг.2, соединения 17 - I7д). Чем больше будет К, тем ниже будет частота и больше период на выходе 16 управляемого делителя 2, т.е. интервал времени каждого участка пропорционален весу кода К.

Также на первом .участке в блоке 9 задания уровня набран код уровня

ленные перемычки в диодной матрице блока 9, фиг.5.). Этот код из блока 9 задания уровня поступает на информационные входы реверсивного счетчи- ка 11 (входы D1 - D8 счетчиков 68 и 69) и на информационные входы Х2 - Х9 стробируемого мультиплексора 10 (фиг.5, соединения 30, - 30g), что обеспечит формирование на его выходе

0

5

,.

счетчика 11 формирование определенного количества импульсов с определенной частотой следования за интервал времени: одного участка.

При наличии разрешения на каком- либо информационном,входе (Х2-Х9) стробируемого мультиплексора частота следования импульсов на выходе его будет равна:

где f

8bU

f /2

I RV

ex

5

0

5

- частота стробирующих импульсов;

n - номер информационного входа, на котором есть разрешение (фиг.5).

Так, информационный вход ХЗ (30,) соответствует n 1; вход Х4 (30)- п 2; Х5 (30,) - n 3; Х6 (ЗО) - n 4; Х7 (30 у) - n i 5; Х8 () - n 6; Х9 (30 - n 7; Х2 (.Og)- п 8.

Так, при наличии разрешения на первом информационном входе ХЗ (ЗО,) при наличии кодовых сигналов нч ад- ресных входах Х10-Х12 (26, - 26,.) и при наличии стробирующих импулъ1.ов на стробирующем входе XI (21) мулъ- типлексора 10 частота следования и(- пульсов на его(Выходе 33 равна fp fg,/2 (фиг.9 А, Б, В, Г, Д).

При наличии разрешения на второй информационном входе Х4 (30) стробируемого мультиплексора 1 О частота следования импульсов на его выходе

ьых

Г.,/4 (фиг.9 А, Б,

р f

бЫХ ВХ

33 равна В, Г, Е).

При наличии разрешения на первом ХЗ (30,) и втором Х4 (30,j;) информационных входах стробируемого мульти- плб ксора 10 на его выходе 33 форми- руется частотный поток несовпадающих импульсов, равный потоков им- nyxibcoB от раздельного воздействия разрешения на первый ХЗ и второй Х4 информационные входы мультиплексора 10 (фиг.9 к)/

При наличии разрешения на третьем информационном входе Х5 (30,) стробируемого мультиплексора 10 частота следования на его выходе 33 равна /8 (фиг.9 А, Б, В, Г, ж).

При наличии разрешения на первом ХЗ (30,), втором Х4 (30,j ) и третьем Х5 (30) информационных входах стробируемого мультиплексора 10 на его выходе 33 формируется частотный поток несовпадающих импульсов, равный сумме потоков импульсов от раздель- ного воздействия разрешения на первый i ХЗ,нторойХ4 и третий Х5 информацион-, ныв входы мультиплексора 10 (фиг. 9 Л).

При наличии разрешения на всех информационных входах Х2 - Х9 (ЗО, - 30g) частота следования на его вы- Ц f

ходе 33 равна fj,,

Исходя из изложенного описания работы стробируемого мультиплексора 10 3 табл.2 представлена зависимость частоты следования импульсов на: выходе 33 стробируемого мультиплексора 10 от сигналов разрешения на информационных входах Х2-Х9 (30( - ЗОд ), на адресных входах Х10-Х12 (26, - 263) и на стробирующем входе XI (21),

Таким образом на выходе 33 стробируемого мультиплексора 10 формируется последовательный частогный поток несовпадающих импульсов, частота следования которых пропорциональна коду на его информационных Х2-Х9 и и адресных входах при наличии на его стробирующем входе XI сигнала разрешения.

Это достигается тем, что первьй нформационный вход ХЗ стробируемого ультиплексора 10, задающий наибольую частоту сигнала на его выходе - соединение 33, соединен с первым ыходом блока 9 задания уровня - соеинение 30,, .задающим половину максиального значения выходного сигнала ,

0

5

0

5

0

5

0

5

0

5

устройства; второй информационный вход Х4 стробируемого мультиплексора 10, задающий частоту сигнала на его выходе - соединение 33 в два раза меньше, чем задает первый информационный вход ХЗ стробируемого мультиплексора 10, соединяется с вторым входом блока 9 задания уровня - соединение 30j; третий информационный вход Х5 стробируемого мультиплексора 10, задающий частоту сигнала на его выходе - соединение 33, в два раза меньше, чем задает второй информационный вход Х4, соединяется с третьим выходом блока 9 задания уровня - соединение 30,, задающим значение выходного сигнала в два раза меньше, чем задает второй выход блока 9 задания уровня - соединение 30, а также соответственно соединены остальные информационные входы Х6, Х7, Х8, Х9, Х2 мультиплексора 10 с выходами блока 9 задания уровня - соединения 30 - 30g, а адресные входы XIО - XI2 стробируемого мультиплексора 10 соединены с выходами КПО-КП2 - соединения 26, - 26, блока 7 приоритетного прерывания, причем, младший разряд адресного входа XIО стробируемого мультиплексора 10 соединен с младшим разрядом выхода КПО - соединение 26,, преобразователя 7 состояния счетчика времени в код, а старший разряд XI2 стробируемого мультиплексора 10 соединен со старшим разрядом выхода КП2 преобразователя 7.

Частотный.поток несовпадающих импульсов на выходе 33 стробируемого мультиплексора 10 формируется только при наличии стробирующих импульсов с длительностью во много раз меньше кодовых сигналов| что исключает искажение выходного частотного потока (при наличии помех появления лишних импульсов или пропадания импульсов в частотном потоке), что обеспечивает повьш1ение точности устройства за счет улучшения помехоустойчивости.

Это достигается тем, что стробирую- щий вход XI стробируемого мультиплексора 10 соединен с первым выходом формирователя 6 стробирующих импульсов (фиг.З, 5 и 10).

Принцип работы канала 13 следующий.

На входы канала 13 поступают три вида сигналов. Первый из них - это сигналы от коммутатора 4, поступаю13

,63

блока 3 за19

щие на входы 18, - 11 Дания времени, последовательно подключающие столбцы диодной матрицы, определяющие участок программы через цепи 18, - 18 6, к цепи ОБЩ i .

В течение каждого участка с определенной, длительностью один из входо 18 ( - 18б- блока 9 соединен с цепью ОБЩ± , остальные входы отсоединены от нее (фиг.5). Интервал времени участка задается в блоке 3 задания времени, который является общим для всех каналов 13. Другим видом сигналов являются стробирующие импульсы, поступающие на стробирующий вход мультиплексора.

За время, в течение которого скоммутирован один из входов 18 - 18 63 блоков 3 и 9 с цепью ОБЩ1 (интервал времени участка программы), с первого выхода формирователя 6 стробирующих импульсов - соединение 21, на стробирующий вход XI строби- руемого мультиплексора 10 поступает число импульсов, равное 2 - I, где п - количество разрядов в счетчике 5 времени, равное числу входов ЗПО- ЗП7 блока 7 приоритетного -прерывания (фиг.1,, 3 и 5).

Третьим видом сигналов являются кодовые посылки, число которых также равно 2 - 1 за интервал времени

участка, поступающие с выхода КПО- КП2 блока 7 приоритетного прерывания на адресные входы X10-XI2 стробируе- мого мультиплексора 10 (фиг.1, 3 и 5, соединения 26j - 26).

В зависимости от заданных парамет- ров в блоке 9 задания уровня для данного участка программы с его выходов 30,...30g на информационные входы Х2...Х9 стробируемого мультиплексора 10 поступают сигналы, кото- рые определяют величину приращения выходного сигнала канала 13 на данном участке (определяют частоту следования импульсов на выходе строби- руемого мультиплексора 10, т.е. ко- личество импульсов за заданный интервал времени на данном участке прог граммы).

Если приращение выходного сигнала задано нулевым, эти потенциальные сигналы поступают на информационные входы D1, D2, D4, D8 двоичных реверсивных счетчиков 68 и 69 реверсивного счетчика 11.

1383297

20

5

0 5 О

5

0 5 ,.

5

Этим обеспе,чивается фиксация выходного сигнала канала -13 на горизонтальных участках программы и исключаются возможные единичные сбои, которые возможны бьши на наклонных участках.

Из этик видов входных сигналов канала на каждом участке программы с помощью стробируемого мультиплексора 10 формируется серия импульсов, , которая поступает на счетньй вход 33 реверсивного счетчика 11. Количество импульсов может быть в пределах от нуля до максимального значения, которое может быть зафиксрфовано в реверсивном счетчике. Например, для двух двоичных реверсивных счетчиков 68 и 69 реверсивного счетчика 11 это значение составляет 255. т.е. 2 -1.

Реверсивный-счетчик 11 обеспечивает три режима работы канала 13: режим постоянного выходного сигнала канала в пределах заданного участка программ (горизонтальный участок программы) : увеличение или уменьшение (положительное или отрицательное приращение) выходного сигнала в пределах заданного участка программы (наклонные участки программы).

Каждый режим работы обеспечивается схемой управления реверсивного счетчика 11 - инвертор 65, элементы И-НЕ 66, 67 и 70, элемент ИЛИ-НЕ 71; двоичными реверсивными счетчиками 68 и 69, работающими в режиме суммирования при увеличении выходного сигнала, в режиме вычитания при уменьшении выходного сигнала и в режиме передачи информации с информационных входов на выходы при постоянном выходном сигнале, и задается перемычками между входами 18, - 1863 и выходами 31 и 32 блока 9 задания уровня.

Причем каждый режим запрещает выполнение других режимов, кроме того, при увеличении или уменьшении выходного сигнала канала вводится ограничение по максимуму и по минимуму.

На тех участках программы, когда программируется горизонтальный участок (режим постоянного выходного сиг- - нала),в блоке 9 задания уровня устанавливаются перемычки между выходом 31 и теми входами 18 ,. . . 18,, , которые задают горизонтальные участки прог граммы.

При подключении какого-либо из этих входов через коммутатор 4 к цепи ОБЩ на выходе 31 блока 9 задания уровня формируется сигнал (уро

.- - Ъень нуля), действующий в течение все-

/.ifo горизонтального участка, который запрещает работу дополнительного , лйтеля 64 и также через логические элементы 66 и 67 запрещает про; хождение импульсов на счетные входы сложения и вычитания ( + 1, -1) двоичi rioro реверсивного счетчика 68,

Этот же сигнал с выхода 31 блока

; 9 задания уровня поступает на входы

С записи двоичных реверсивных счетчиков 68 и 69 и является для этих вхо- j ду выходом 32 и теми входами 18... дов сигналом разрещения. По этому , которые задают участки програм- сигналу разрешения информация с выходов 30,...30g блока 9 задания уровня, поступающая на информационные входы

мы с уменьшением выходного сигнала.

При подключении какого-либо из этих входов через коммутатор 4 к цеD1 , D2, D4, D8 двоичных реверсивных 20 « ОБЩ на выходе 32 блока 9 задания счетчиков 68 и б9, постоянно пропус- уровня формируется сигнал (уровень кается на их выходы Q1, Q2, Q4, Q8 .в течение всего горизонтального

нуля), действующий в течение всего участка уменьшения выходного сигнала, участка.который через элемент И-НЕ 66 запреВ режиме увеличения выходного сиг- 25 Щэет прохождение импульсов на счет- нала между входами 18...18бз и вы- ный вход слежения ( + 1) двоичного реходами 31 и 32 блока 9 задания уровня перемычки не устанавливаются и с выхода 32 на вход элемента И-НЕ 66 поступает разрешающий сигнал, который проинвертированный инверторам 65 одновременно является сигналом запрета для элемента И-НЕ, с выхода которого сигнал запрета поступает на счетный вход вычитания (-1) двоичного реверсивного счетчика 68.

С выхода 31 блока 9 задания уровня на входы записи двоичных реверсивных счетчиков 68 и 69 поступает сигнал запрета, который одновременно является сигналом разрешения для дополнительного делителя 64 и элемента И-НЕ 66 и в течение всего данного

30

35

40

версивного счетчика.68, но через инвертор 65 и элемент И-НЕ 67 разрешает прохождение импульсов, которые поступают с выхода 33 стробируемого мультиплексора 10 через дополнительный дели- тель 64 на счетньй вход вьтитания (-1) счетчика 68 (режим вычитания).

Также предусмотрено запрещение прохождения счетных вычитающих импульсов при нулевых состояниях выходов Q1 , Q2, Q4, Q8 двоичных реверсивных счетчиков 68 и 69. При этом на выходе элемента ИЛИ-НЕ 71 формируется нулевой потенциал, который поступает на вход элемента И-НЕ 67 и 351прещает дальнейшее прохождение вычитающих импульсов.

Дпя улучшения линейности аппроксиучастка дано разрешение на суммирова-дд мации выходного сигнала за счет ввение импульсов, которые поступают с выхода стробируемого мультйплексо- ра 10 через дополнительный делитель 64, элемент И-НЕ 66 на счетный вход сложения (+ 1 ) двоичного реверсивного счетчика 68 (режим суммирования).

При этом предусмотрено ограничени выходного сигнала по максимуму. Это осуществляется при помощи элемента И-НЕ 70, на выходе которого формируется запрещающий сигнал, когда на выходах Q1, Q2, Q4, Q8 двоичных реверсивных счетчиков 68 и 69 возникнут единицы (счетчики заполнены).

При этом на выходе элемента И-НЕ 70 формируется нулевой потенциал, который поступает на вход элемента 66 и запрещает дальнейшее прохождение импульсов с выхода 33 стро- бируемого мультиплексора на счетньй вход сложения (+1) двоичного реверсивного счетчика 68.

Аналогичный принцип работы реверсивного счетчика II в режиме уменьшения выходного сигнала.

В этом режиме в блоке 9 задания уровня устанавливаются перемычки между выходом 32 и теми входами 18... , которые задают участки програм-

мы с уменьшением выходного сигнала.

При подключении какого-либо из этих входов через коммутатор 4 к це0

5

0

версивного счетчика.68, но через инвертор 65 и элемент И-НЕ 67 разрешает прохождение импульсов, которые поступают с выхода 33 стробируемого мультиплексора 10 через дополнительный дели- тель 64 на счетньй вход вьтитания (-1) счетчика 68 (режим вычитания).

Также предусмотрено запрещение прохождения счетных вычитающих импульсов при нулевых состояниях выходов Q1 , Q2, Q4, Q8 двоичных реверсивных счетчиков 68 и 69. При этом на выходе элемента ИЛИ-НЕ 71 формируется нулевой потенциал, который поступает на вход элемента И-НЕ 67 и 351прещает дальнейшее прохождение вычитающих импульсов.

Дпя улучшения линейности аппрокси0

5

дения равномерности следования импульсов от стробируемого мультиплек- . сора 10 в реверсивном счетчике 11 используется выравниватель (дополнительный делитель), который содержит делитель частоты на 4. Неравномерность частотного потока уменьшается в 4 раза.

Выход с реверсивного счетчика.1I отдельно по каждому разряду (выходы Ql, Q2, Q4, Q8 двоичных реверсивных счетчиков 68, 69) подключен к входу цифроаналогового преобразователя 12, на выходе 14 которого формируется вы23

ходной сигнал участка заданной про- граммы каждого канала 13.

Таким образом, в течение отработ- ки первого участка программы (при заданных параметрах в блоке 3 задания времени и в блоке 9 задания уровня) импульсы с выхода 33 стробируемого мультиплексора 10 поступают на счетный вход реверсивного счетчика 11.

Двоичный код с выхода реверсивно- го Счетчика 11 поступает на цифроана- логовый преобразователь 12, где фор- мируется заданный выходной сигнал на

выходе 14 в каждом канале 13 для пер- дифроаналогового преобразователя, вы

вого участка программы.

После окончания первого участка (окончание полного цикла счета в счетчике 5 времени на выходе счетчика 5.времени) образуется перепад напряжения, который поступает на вход 20 формирователя 8 счета и сброса. На выходе 29 формирователя 8 счета и сброса формируется импульс частичного сброса, который поступает на входы сброса управляемого делителя 2 и счетчика 5 времени и сбрасывает их в нулевое состояние.

На выходе 27 формирователя 8 формируется импульс счета, по.ступающий на счетный вход коммутатора 4, который устанавливается в новое состояние. При этом коммутатор 4 подключает второй столбец диодной матрицы (второй вход блока З), цепь IS блока 3 задания времени к цепи ОБЩ и в управляемый делитель 2 записывается новое значение интервала времени для второго участка программы. Одновременно коммутатор 4 подключает второй .стол- бец диодной матрицы (второй вход блока 9 - цепь 182). блока 9 задания уровня всех каналов 13 к цепи ОБЩ1 и на информационных входах Х2...Х9 стробируемого мулвтиплексора 10 появится новое значение уровня выходного сигнала каналов 13 для второго участка программы.

Процесс формирования выходного сигнала на втором участке программы за новый заданный интервал времени с новыми значениями величин для каждого канала 13 повторяется.

После окончания второго участка программы коммутатор 4 переключается на третий участок и т.д. Происходит отработка заданной программы.

ормула

24 и 3

обретения

I.Многоканальное программное задающее устройство, содержащее счет- .чик времени, генератор тактовых импульсов, управляемый делитель, информационные входы которого соединены с выходами блока задания времени, входы которого соединены с выходами коммутатора и с входами блоков задания уровня идентичных каналов, каждый из которых содержит реверсивный счетчик, выходы которого соединены с входами

0

5

0

д

5

5

0

5

ход которого является выходом канала, отличающееся тем, что, с целью повьш1ения точности И. уменьшения числа линий связи, в устройство дополнительно введены преобразователь состояния счетчика времени в код, формирователь стробирующих импульсов, формирователь счета и сброса, а в каждый канал введен преобразователь параллельного кода, информационные входы которого соединены с первыми выходами блока задания уровня и с информационными входами реверсивного счетчика, управляющие входы которого соединены с вторьми выходами .блока задания уровня, тактирующий вход реверсивного счетчика соединен с выхо- дом преобразователя параллельного кода, адресные входы которых в каждом канале соединены, с выходами кода прерывания преобразователя состояния счетчика времени в код, стробирующий вход преобразователя параллельного кода каждого канала соединен с первым выходом формирователя стробирующих импульсов, первый вход которого соединен с выходом управляемого делителя, второй выход - с входом разрешения записи преобразователя состояния - счетчика времени в код, а третий выход - с входом синхронизации преобразователя состояния счетчика времени в код, выход разрешения групт пы прерывания которого соединен с вторым входом формирователя стробирующих импульсов, четвертый выход которого соединен с входом счетчика времени, выходы которого,г.начиная . с младшего по старший разряды, соеди нены с входами запроса прерывания соответственно с высшего по низший приоритеты преобразователя состояния счетчика времени в код, выход старшего разряда счетчика времени соединен с входом формирователя счета и сброса, первый, выход которого соединен со счетным входом коммутатора, второй выход - с входами сброса ком- мутатора и реверсивных счетчиков каждого какала, третий выход - с входам сброса счетчика времени и управляемого делителя, выход генератора тактовых импульсов соединен с вычитаю- щим входом управляемого делителя.

элемента И-НЕ является первым выходом

формирователя стробирующих импульсов, д выход элемента ИЛИ является третьим

четвертый выход дешифратора является выходом этого форг рователя.

5

0

5

о

5

0

вторым выходом формирователя стробирующих импульсов, выход третьего инвертора является третьим выходом формирователя стробирующих импульсов, выход второго инвертора является четвертым выходом формирователя стробирующих импульсов, вход пятого инвертора является вторым входом формирователя стробирующих импульсов,

27

1383297

28 Таблица

V /7,

,... J8e3

ск.

«I

29

75

ггуН

гэ

23

LK

25

I

EJMJrQ

29 5

27 ,J

/5,..7J,Uo CSpoc

ге/... ffj

i/ef

.-«о

3l

ST-zS

JO,... 30,,

-A..::.:.

tE eLZ3j

7,..)ЛГ--- --

S

П

г«

/3

HI

U

ФигЛ

i n I I t r I M ( I r I I t

.34, Kt

:«7 JV,

Фиг. 7

; i/ v 2i/«/ tf / «ifv|5{WCWM 6участок 7уу

1

I |i

§s

.i,

X-fyv. К yv.

I

IN I I

I I I

.fff

| Устройство для программногоупРАВлЕНия | 1979 |

|

SU840811A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Программное задающее устройство | 1979 |

|

SU903808A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-03-23—Публикация

1986-01-13—Подача