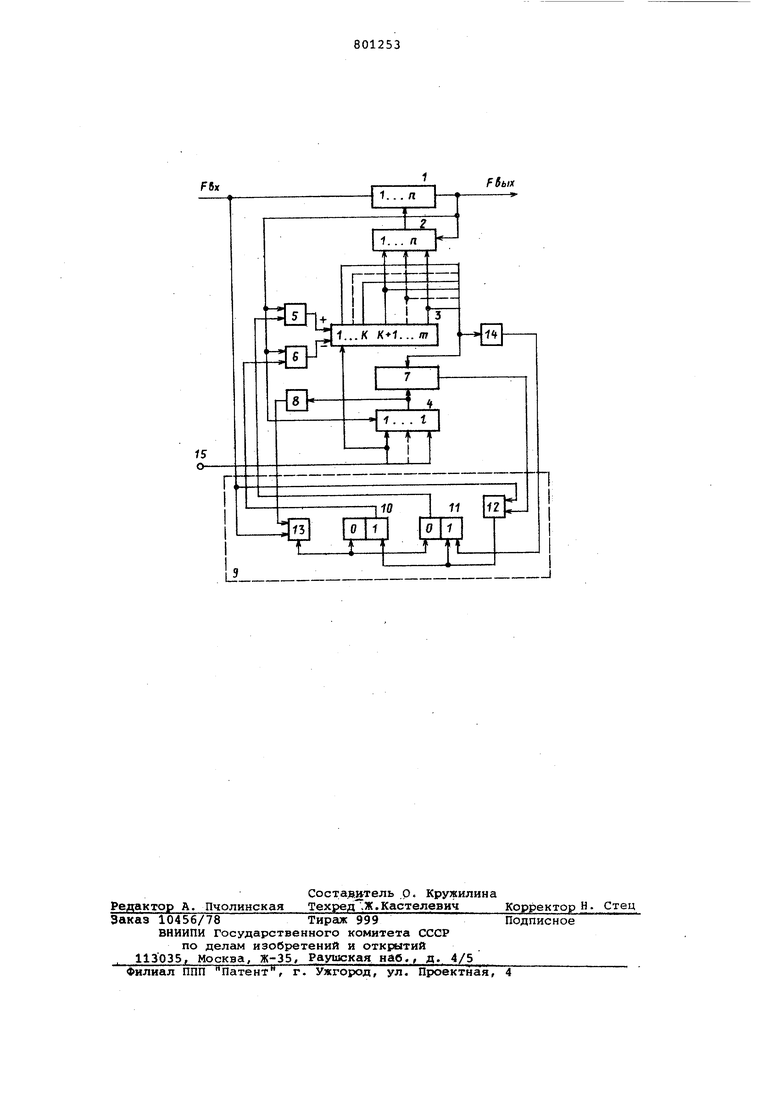

закону, монотонно увеличиваясь и уменьшаясь. Устройство не может функционировать при занесении в вычитающий счетчик нечетного двоичного кода, по абсолютной величине меньшего удшоенного значения максимального кода реверсивного счетчика импульсов. Кром того, в данном делителе частоты входная частота максимально может быть по делена на число, равное максимальному коду реверсивного счетчика, т.е кратному числу в двоичной системе нечисления. Это ограничивает .сферу при менения такого делителя частоты. Цель изобретения - расширение фун циональных возможностей. Поставленная цель достигается тем что в делитель -частоты следования им пульсов с автоматически изменяющимся коэффициентом деления, содержащий двоичный делитель частоты, первый вход которого подключен к входной ши и первому входу коммутатора, второй вход - к выходу блока записи параллельного кода, а выход - к первым вхо дам элементов И, входу блока записи параллельного кода и входу вычитающего счетчика импульсов, разрядные входы которого подключены к кодовой шине, а выход - к входу дешифратора нуля и первому входу блока сравнения, второй вход которого соединен с разрядными выходами реверсивного счетчика импульсов, а выход - со вторым входом коммутатора, третий вход которого подключен к выходу дешифратора нуля, а выходы коммутатора - ко вторым входам элементов И, выходы которых соединены со входами реверсивного счетчика импульсов, вве ден дешифратор максимального кода, вход которого соединен со вторым входом блока сравнения, а выход - с четвертым входом коммутатора, при этом выходы старших разрядов реверсивного счетчика импульсов соединены с разрядными входами блока записи параллельного кода, а установочный вход первого разряда - с входом пер вого разряда вычитающего счетчика им пульсов . На чертеже представлено устройство, -структурная электрическая схема. Схема содержит двоичный делитель ча9тоты, блок 2 записи параллельного кода, реверсивный счетчик 3 импульсо вь итающий счетчик 4 импульсов, элеме(нты 5 и б И, блок 7 сравнения, дешифратор 8 нуля, коммутатор 9, триггеры 10 и 11 коммутатора, элементы 1 и 13 И коммутатора, дешифратор 14 максимального кода, кодовая шина 15. Делитель частоты следования им пульсов работает следующим образом. Импульсы с частотой FBX поступают на вход двоичного делителя 1. Импуль переполнения с выхода двоичного дели теля 1 через блок 2 переписывает прямой код старших (k+l)...ni разрядр счетчика 3 в двоичный делитель 1,. поступает на вход счетчика 4 и через элемент 5 поступает на суммирукяций вход счетчика 3. Частота выходе йвоичного делителя 1 остается постоянной до тех пор, пока не заполнятся 1...К разряды счетчика 3. С приходом следующего импульса на + вход 1...К разряды счетчика 3 установятся в О, а (К+1) разряд - в 1 и в результате увеличится частота , которая останется постоянной до следующего импульса переполнения 1...К разрядов счетчика 3. Таким образом частота F ; бyдeт ступенчато возрастать по мере увеличения кода в счетчике 3 и установится максимальной при равенстве значений кода в счетчике 3 и числа в дешифраторе 14. Если значение кода в счетчике 4 больше удвоенного значения числа в дешифраторе 14, то сигнал .с его выхода после достижения равенства кода счетчика 3 и числа в дешифраторе 14 устанавливает триггер 11 в единичное состояние и снимает тем самым разрешающий потенциал с нулевого выхода триггера 11 на вход элемента 5, запрещая прохождение импульсов на суммирукяций вход счетчика 3. С этого момента установившаяся максимальная частота импульсов выхода двоичного делителя 1 сохраняется до тех пор, пока код счетчика 4 не сравняется с кодом в счетчике 3. После сравнения кодов блок 7 выдает разрешающий потенциал на элемент 12, импульс с выхода которого устанавливает триггеры 10 и 11 в единичное состояние, в результате чего с единичного выхода триггера 10 поступает разрешающий потенциал на элемент б. Импульсы с выхода двоичного делителя 1 через элемент б начинают поступать на вычитакнций вход счетчика 3 и уменьшать в нем значение кода, что приводит соответственно к ступенчатому снижению выходной частоты Fp(Дeлителя. Когдакод в счетчике 4 станет равным нулю, дешифратор 8 подаст разрешающий потенциал на элемент 13 для прохождения импульсов FBX на сброс триггеров 10 и 11 в нулевое состояние и возвращения делителя частоты в исходное состояние .Для выполнения следукндего цикла работы устройства подается новый код по шине 15 в счетчик 4 и одновременно зна.чение первого разряда этого кода на установочный вход первого разряда счетчика 3, что всегда создает четную разность между кодами в счетчиках 4 и 3 для выполнения условия сравнения кодов в блоке 7. Если значение кода в счетчике 4 меньше удвоенного значения числа в дешифраторе 14, то частота импульсов с выхода двоичного далителя 1 увеличивается до такой величины, пока увеличивающееся значение кода счетчика 3 не станет равньлм уменьшающемуся значению кода счетчика 4. После сравнения кодов блок 7 (Ввдает разрешающий потенциал на элемент 12 для прохождения импульса входной частоты FBIC на установку триг геров 10 и 11 в единичное состояние. Разрешающий потенциал с нулевого выхода триггера 11 снимается с элемента 5, а разрешающий потенциал с единичного выхода триггера 10 подается на элемент 6. С этого момента счетчик 3 начинает работать на уменьшение кода в нем, тем самым ступенчато уменьшая частоту импульсов Р0цхС выхо да двоичного делителя 1. Цикл работы делителя частоты заканчивается аналогично описанному вы ше при появлении нулевого значения кода в счетчике 4. Частота на выходе двоичного делителя 1 равна во всех случаях РВЬЛ где m - общее число разрядов счетчиК - число младших 1 ... К разрядов счетчика 3; М - число в старших (К+1)...т разрядах счетчика 3. Данный делитель частоты следовани импульсов с автоматически изменяющим ся кoэффициeнтQм деления обеспечивае функционирование как с четными, так и нечетными кодгши деление входной частоты на произвольное целое число в пределах разрядности реверсивного счетчика не только по линейному, но и по ступенчатому закону на участках увеличения и уменьшения выходной час тоты. Формула изобретения Делитель частоты следования импульсов с автоматически изменяющимся коэффициентом деления, содержащий двоичный делитель частоты, первый вход которого подключен к входной шине и первому входу коммутатора, второй вход - к выходу блока записи параллельного кода, а выход - к первым входам элементов И, входу блока записи параллельного кода и входу вычитающего счетчика импульсов, разрядные входы которого подключены к кодовой шине, а выход - к входу дешифратора нуля и первому входу блока сравнения, второй вход которого соединен с разрядными выходалш реверсивного счетчика импульсов, а выход - со вторым входом коммутатора, третий вход которого подключен к выходу дешифратора нуля, а выходы коммутатора - ко вторым входам элементов И, выходы которых соединены со входами реверсивного счетчика импульсов, о т л и ч аю щ и и с я тем, что, с целью расширения функционсшьных возможностей, ё него введен дешифратор максимальjioro кода, вход которого соединен coj вторым входом блока сравнения, а выход - с четвертьм входом коммутатора, при этом выходы старших разрядовреверсивного счетчика импульсов соединены с разрядными входами блока записи парашлельного ксща, а установочнь1й вход первого разряда - с входом первого разряда вычитающего счетчика импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 451199, кл. Н 03 К 23/00, 19.01.72. 2.Авторское свидетельство СССР № 552704, кл. Н 03 К 23/00, 24.02.76.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с автоматически изменяющимся коэффициентом деления | 1976 |

|

SU552704A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| Многоканальное программное задающее устройство | 1986 |

|

SU1383297A1 |

| Делитель частоты следования импульсов с автоматически изменяющимся коэффициентом деления | 1984 |

|

SU1221746A1 |

| Устройство для упорядочения массива чисел | 1986 |

|

SU1383336A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Генератор квазирегулярных последовательностей импульсов | 1979 |

|

SU866717A1 |

| Генератор векторов | 1988 |

|

SU1596375A2 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для моделирования узлов коммутации сообщений | 1986 |

|

SU1354203A1 |

Авторы

Даты

1981-01-30—Публикация

1978-10-11—Подача