(54) ИНТЕГРАТОР

Относительтя величина этой ошибки

ПЕр

Ux

дц цТди

nfр

5 T-t

Ux-tnEp

UX-T

fp (1)

-fc t

где Ui - напряжение на выходе интегрирующе. го усилителя в момент сравнения с опорным напря жением сравнивающего устройства;

Т - время одного цикла интегрирования, т.е. время, за которое напряжение на выходе интегрирующего усилителя достигает значения Ui.

Как видно из формулы (1), при заданной относительной т;очности 5 ограничивается время одного цикла иитегрирования, т.е. динамический диапазон входных сигналов, от уровня которых зависит скорость интегрирования.

Физически возникновение ошибки Ди объясняется тем, что один из интегрирующих усилителей после формирования сравнивающим устройством импульса сравнения уже перестал интегрировать, а второй еще не начал.

Целью изобретения является повышение :{очкости интегрирования.

Поставленная цель достигается тем, что предложенньш интегратор дополнительно содержит логический элемент И-ИЛИ, дополнительные переключатель, блок сравнения, инверторы и сумматор. Первьш дополнительный инвертор, дополнительный сумматор и второй дополнительный инвертор соединены последовательно. Выход второго дополнительного инвертора соединен с первым входом дополнительного блока сравнения, второй вход которого соединен с выходом пятого и шестого переключателей, а выход - с вторым входом блока управления, выход которого через логический элемент И-ИЛИ соединен с управляющими входами первого, второго, третьего и четвертого переключателей. Вход интегратора подключен ко входу первого дополнительного инвертора непосредственно, а к первому входу дополнительного сумматора через дополнительньш переключатель, управляющий вход которого подключен к выходу блока определения знака. Второй вход дополнительного сумматора соединен с первым источником опорного сигнала.

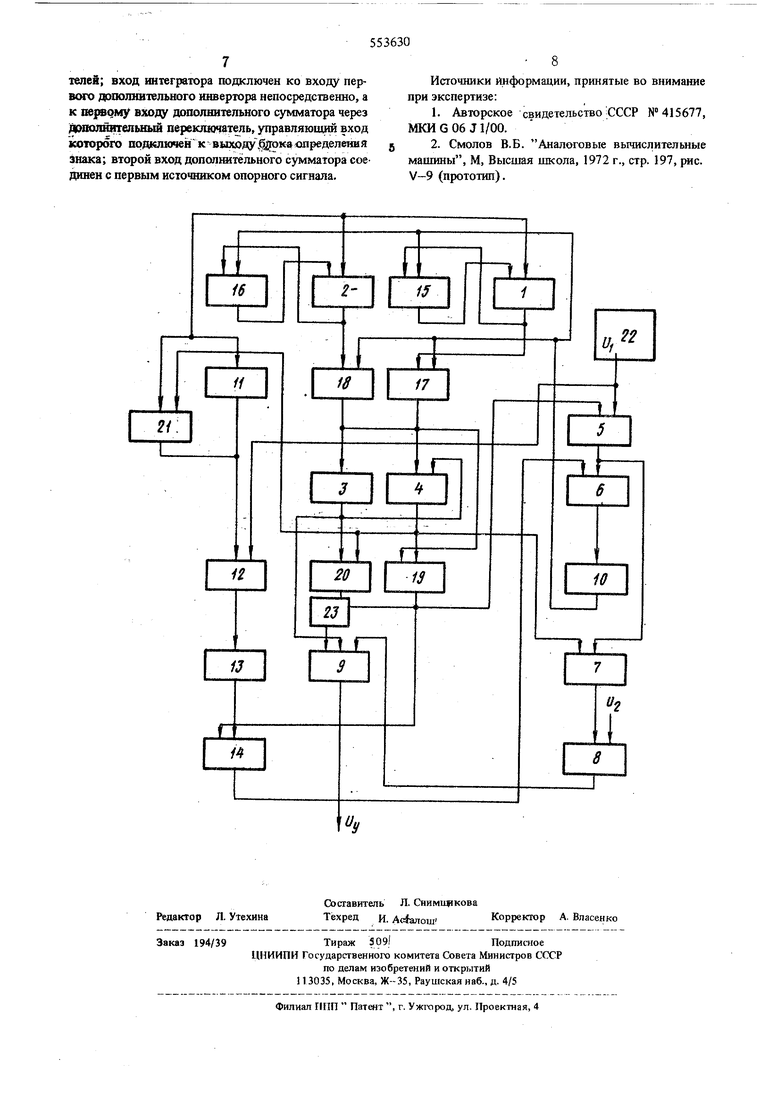

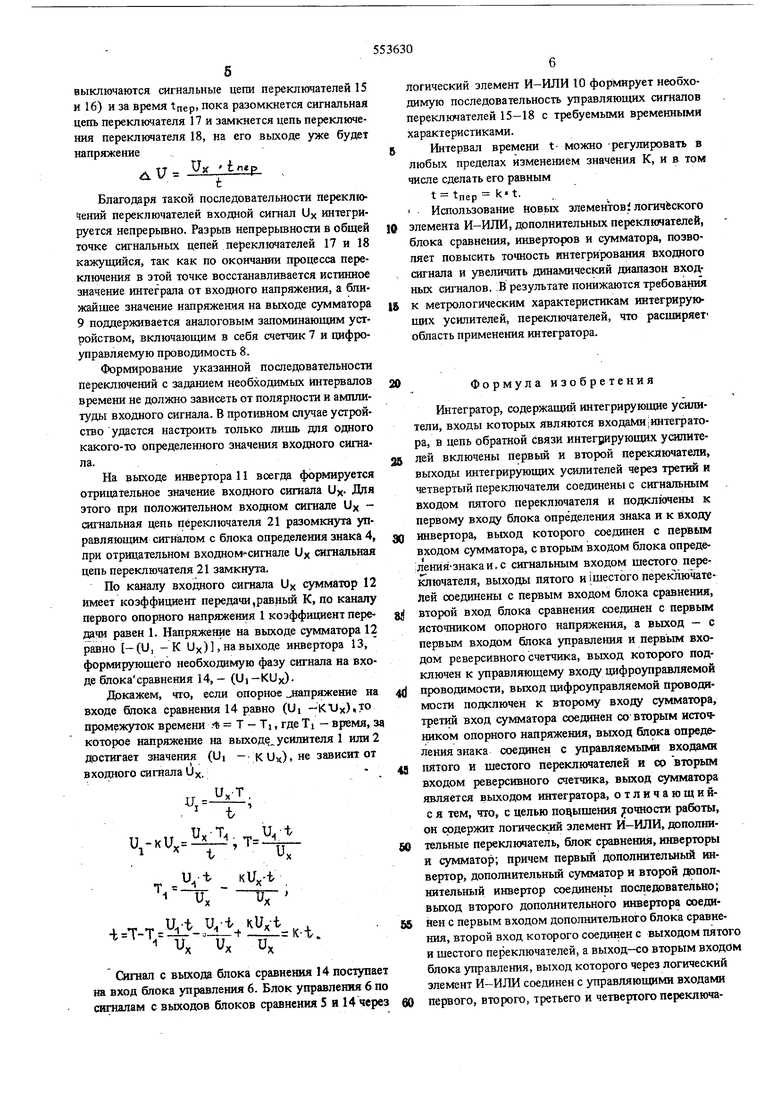

На чертеже представлена блок-схема интегратора.

Интегратор содержит первый 1 и второй 2 интегрирующие усилители, инвертор 3, блок определения знака 4, блок сравнения 5, блок управления 6, реверсивный счетчик 7, цифроуправляюшую прово димость 8, сумматор 9, логический элемент И-ИЛИ 10, первый дополнительный инвертор 11, Дополнительный сумматор 12, второй дополнительньш инвертор 13, дополнительный блок сравнения 14, переключатели 15-20, дополнительньш переюпочатель 21 источники опорного напряжения. 22, 23

Интегратор работает следующим образом.

При входном сигнале Ux О (интегратор 1включен) на счетчике 7 записан код 1000...0. Напряжение на выходе цифроуправляемой проводимости 8 пропорщ онально произведению значения этого кода (так же как и для значения любого другого кода на ее входе) на значение опорного напряжения цифроуправляемой проводимости 8, Напряжение с выхода цифроуправляемой проводимости 8 поступает на сумматор 9, к которому для компенсации ненулевого начального значения подключен второй источник опорного напряжения .

Предположим, что, начиная с начального момента времени, входное напряжение DX интегрируется усилителем 1 или усилителем 2, (что не имеет прин ципиального .значения). При этом на управляющих входахпереключателей 15, 18, 16 и 17 управляющий сшнал имеет такое значение, что сигнальные цепи переключателей 15, 18 разомкнуты, а сигнальные цепи переключателей 16, 17 замкнуты.

Блок определения знака4 по сигналам на его входе с общей точки сигнальных цепей переключателей 17, 18 и инвертора 3 через управляющие входа переключателей 19, 20 замыкает сигнальные цепи одного из этих переключателей таким образом, что на их общей точке ползгчается напряжение одного определенного знака, т.е. формируется модуль входного напряжения Ux.

Через инвертор 3, восстанавливающий фазу проинтегрированного входного сигнала, измененную на 180° усилителем 1, проинтегрировшшый входной сигнал поступает на сумматор 9, на выходе которого образуется алгебраическая сумма напряжений, поданных на его вход.

Как только напряжение с общей точки сигнальных цепей переключателей 19,20 сравняется с первым опорным напряжением на входе блока сравнения 5, на его выходе формируется импульс,- возбуждающий блок управления 6 и переводящий счетчик 7 в ближайшее состояние по () или по (-) счетной единице в зависимости от управляющего сигнала с блока определения знака 4. В соответствии с новым кодом на выходе счетчика 7 меняется значение напряжения на выходе цифроуправляемой проводимости 8 и соответственно на выходе сумматора 9.

При одновременном переключении,переключателей 15, 18 на время переключения прерьшается интегрирование входного сигнала. Для исключения этого целесообразно организовать последовательность переключений переключателей следующим образом. При интегрировании вхощого сигнала усилителем 1 переключатель 1 б должен начать переключаться раньше, чем переключатели 15, 17и 18. При интегрировании входного сигнала усилителем 2 переключатель 15 должен начать переключаться раньше, чем переключатели 16, 17 и 18.

Оптимальный промежуток времеш, на который раньше должен начать переключаться соответствующий переключатель, равен t tnep, где tngp время переключе шя переключателя. В этом к моменту начала выключения, например, ус.илителя 1 усилитель 2 включается (т.е. включаются к выключаются сигнальные цепи переключателей 15 и 16) и за время tnep, пока разомкнется сигнальная цепь переключателя 17 и замкнется цепь переключения переключателя 18, на его выходе уже будет напряжение д и У yt лер Благодаря такой последовательности переклю кий переключателей входной сигнал DX интегрируется непрерьшно. Разрьт непрерьшности в общей точке сигнальных цепей переключателей 17 и 18 кажущийся, так как по окончании процесса переключения в этой точке восстанавливается истинное значение интеграла от входного напряжения, а ближайшее значение напряжения на выходе сумматора 9 поддерживается аналоговым запоминающим устройством, включающим в себя счетчик 7 и цифроуправляемую проводимость 8. Формирование указанной последовательности переключений с заданием необходимых интервалов времени не должно зависеть от полярности и амплитуды входного сигнала. В противном случае устройство удастся настроить только лишь для одного какого-то определенного значения входного сигнала. На выходе инвертора 11 всегда формируется отрицательное значение входного сигнала Ux- Для этого при положительном входном сигнале Ux сигнальная цепь переключателя 21 разомкнута управляющим сигналом с блока определения знака 4, при отрицательном входном-сигнале Ux сигнальная цепь переключателя 21 замкнута. По каналу входного сигнала Ux сумматор 12 имеет коэффициент передачи,равшш К, по каналу первого опорного напряжения 1 коэффициент передачи равен 1. Напряжение на выходе сумматора 12 равно -(и, -К УХ), на выходе инвертора 13, формирующего необходимую фазу сигнала на входе блокасравнения 14,- (Uj-KUx). Докажем, что, если опорное Jнaпpяжeш e на входе блока сравнения 14 равно (Ui -KXJx) промежуток времени -t Т - Ti, где Ti - время, зч которое напряжение на выходе усилителя 1 или 2 достигает значения (Ui - к Ux). не зависитот входного сигнала Ох. и,-ки,. .M-..t и, и Опиал с выхода блока сравнения 14 поступает на вход блока управления 6. Блок управления 6 по сигналам с выходов блоков qjaBHeHHH 5 я 14 через логический элемент И-ИЛИ 10 формирует необходимую последовательность управляющих сигналов переключателей 15-18 с требуемыми временными характеристиками. Интервал времени t- можно регулировать в Любых пределах изменением значения К, и в том числе сделать его равным I Использование новых элементовi логического элемента И-ИЛИ, дополнительных переключателей, блока сравнения, инверторов и сумматора, позволяет повысить точность интегрирования входного сигнала и увеличить динамический диапазон входных сигналов. Ъ результате понижаются требования к метрологическим характеристикам интегрирующих усилителей, переключателей, что расширяетобласть применения интегратора. Формула изобретения Интегратор, содержащий интегрирующие усилители, входы которых являются входами интегратора, в цепь обратной связи интегвирующих усилителей включены первый и второй переключатели, выходы интегрирующих усилителей через третий и четвертый переключатели соединены с сигнальным входом пятого переключателя и подключены к первому входу блока определения знака и к входу инвертора, выход которого соединен с первым входом сумматора, с вторым входом блока опреде:ления-знакаи,с сигнальным входом щестого переключателя, выходы пятого и (шестого переключатеЛей соединены с первым входом блока сравнения, второй вход блока сравнения соединен с первым источником опорного напряжения, а выход - с первым входом блока управления и первым входом реверсивного счетчика, выход которого подключен к управляющему входу цифроуправляемой проводимости, выход цифроуправляемой проводимости подключен к второму входу сумматора, третий вход сумматора соединен со вторым источником опорного напряжения, выход блока определения знака соединен с управляемыми входами пятого и щестого переключателей и ер вторым входом реверсивного счетчика, выход сумматора является выходом интегратора, отлнчающийс я тем, что, с целью повышения ;гочности работы, он содержит логический элемент И-ИЛИ, дрполнительные переключатель, блок сравнения, инверторы и сумматор; причем первый дополнительный инвертор, дополнительный сумматор и второй допоп нительный инвертор соединень последовательно; выход второго дополнительного инвертора соедиНей с первым входом дополнительного блока сравнения, второй вход которого соединен с выходом пятого и щестого переключателей, а выход-со вторым входом блока управления, выход которого через логический элемент И-ИЛИ соединен с управляющими входами первого, второго, третьего и четвертого переключа

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1978 |

|

SU744628A2 |

| Устройство автоматической смены масштабов для аналоговой вычислительной машины | 1983 |

|

SU1113809A1 |

| ПЕРЕСТРАИВАЕМЫЙ ARC-ФИЛЬТР | 1995 |

|

RU2110140C1 |

| Интегратор | 1981 |

|

SU1081643A2 |

| Интегратор с автокоррекциейКОэффициЕНТА пЕРЕдАчи | 1978 |

|

SU805346A1 |

| ВИХРЕТОКОВЫЙ ДЕФЕКТОСКОП | 1995 |

|

RU2085932C1 |

| Устройство для автоматической смены масштабов в аналоговой вычислительной машине | 1983 |

|

SU1080153A1 |

| Функциональный преобразователь | 1988 |

|

SU1674171A1 |

| Аналого-цифровая вычислительная система | 1986 |

|

SU1420605A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

Авторы

Даты

1977-04-05—Публикация

1975-06-02—Подача