Изобретение относится к вычислительной технике.

Известны устройства для автсматической смены масштабов (УАСМ), содержащее электромеханические блоки, осуществлякщие плавное изменение масштаба по машинной переменной l .

Недостатком этих устройств является низкая полоса пропускания и необходимость высокоточной организации работы всех устройств, осуществляющих изменение масштабов, в противном.случае в решение вносятся существенные сшибки, значительно искажающие физику моделируемого процесса.

Известно также устройство, осуществляющее подключение дублирукщих вычислительных блоков ВБ) в момент смены масштабов, причем подключаемые ВБ заранее подготовлены к работе в системе новых масштабов, т.е. на интеграторах заранее сформированы напряжения начальных условий по масштабируеколм переменным в ново масштабе 2 .

Недостаток этого устройства ограничение возможностей АВМ из-за использования ВБ для смены масштабов, которые лишь частично исполь.зуются в процессе решения.

Наиболее близким к предлагаемому является уст Зойство для .автоматической смены масштабов в аналоговых вычислительных машинах, содержащее блок фиксации границ поддиапазона, подсоединенный к выходу интегратора, блок управления заданием иачальных условий, реверсивный распределитель импульсов , соединенный с. блоком переключения режимов, запоминающие блоки с блоками управления , соединённые соответственно с цифроуправляемьо4И сопротивлениями,, одно из которых включено на входе -интегратора, и блок сопряжения с другими устройствами автоматической смены масштабов при их функциональной связи, выход которого соединен с реверсивным распределителем импульсов .

Однако данное устройство характериэуется достаточно большим временйш интервалом, что при моделировании . высокочастотных процессов, пртекакЕщих в динашических системгис, вносит существенную пЬгреаность в .решение. Недостатком этого устройства яаяяётся также неточность выставки нагаряжения начального условия связанная с аипаратурнвми особенностдали фиксации поддиапаэояа {гиетерезис схем сравнения, осуцёствлякцях выставку напряжения начального .условия для поддиапазона) . .

Целью изобретения является повышение точности и быстродействия устройства.

Для достижения поставленной цели в устройство для автоматической смены масштабов в аналоговой вычислительной машине, содержащее операционньй усилитель, к выходу которого подключен блок фиксации Г14аниц поддиапазона, последовательно соединенные блок сопряжения и реверсивный счетчик, цифроуправляемое сопротивление, включенное между входом устрой ства и входом операционного усилителя, Запоминающий блок, подключенный к управляющему входу цифро5П1равляемого сопротивления, и интегрирующий конденсатор, введены сум-, мирующий усилитель/ переключатель, блок формирования границы поддиапазона, блок задания кода и ключи, включенные в плечи моста, одна диагональ моста включена между входом и выходе операционного усилителя, в другую диагональ мостовой схемы включен интегрирующий конденсатор, .управлякщие входы ключей противоположных плеч мостовой,.схемы попарно подключены к соответствующим импульсным выходам блока фиксации границ поддиапазона,потенциальный выход которого соединен со входом блока сопряжений, выход реверсивного счетчика подключен к адресному входу запоминающего блока и управляющему входу переключателя, сигнальные входы которого являются входами опорного напряжения устройства, входы суммирующего усилителя соединены с выходами операционного .усилителя, и блок формирования границы поддиапазона,первый,втсфо и третий входы которого подключены соответственно к выходам блока сопряжения, переключателя и блока задания кода.

Кроме того, блок формирования границы поддиапазона содержит элемент ИЛИ, группу элементов И и декодирующую резистивную матрицу типа Rr2R, причем группа входов элемента ИЛИ является первьм входом блока, вы|сод элемента ИЛИ подключен к первым входам элементов И |Группы., вторые входы которых являются третьим входом блока, выходы элементов И подключены к управляющим входам декодирующей резистивной матрицы типа а-2Я, сигнальный

вход которой является вторым входом блока.,

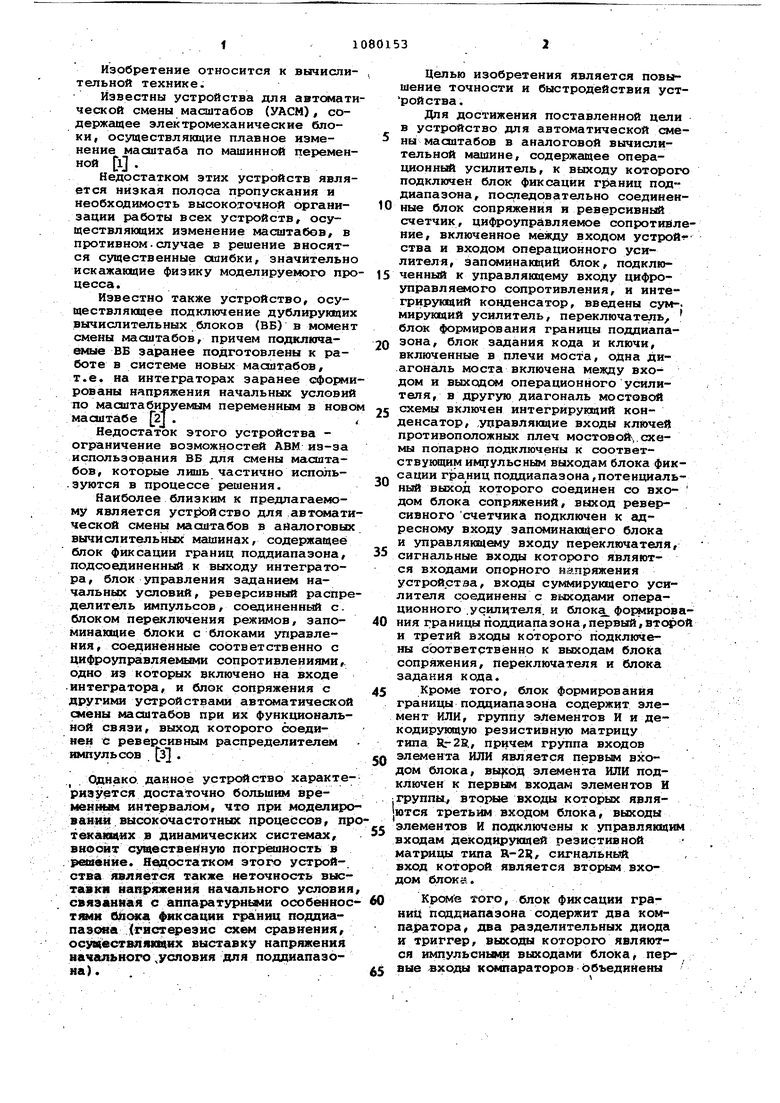

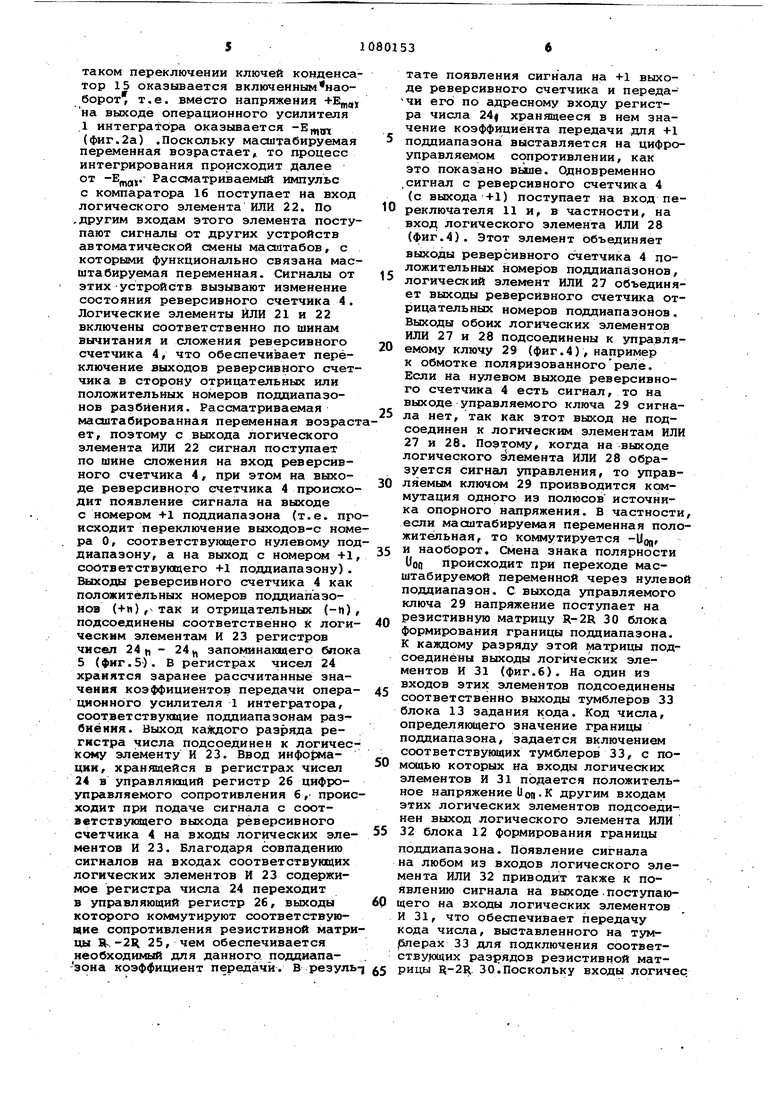

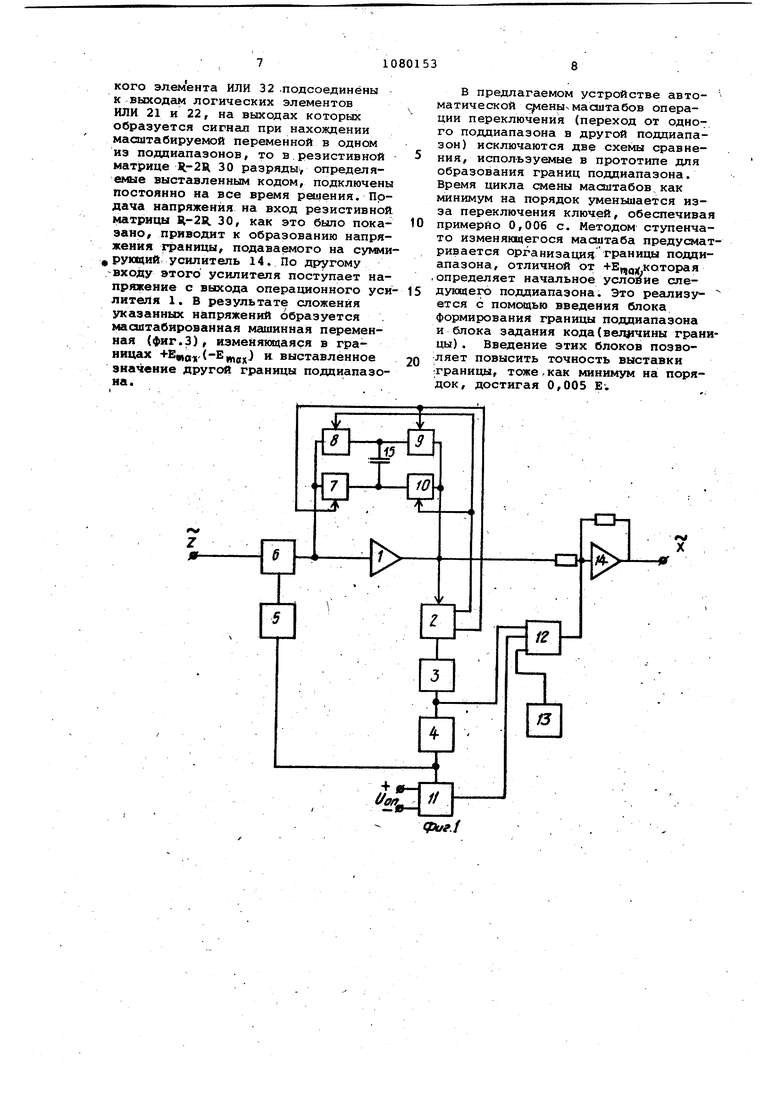

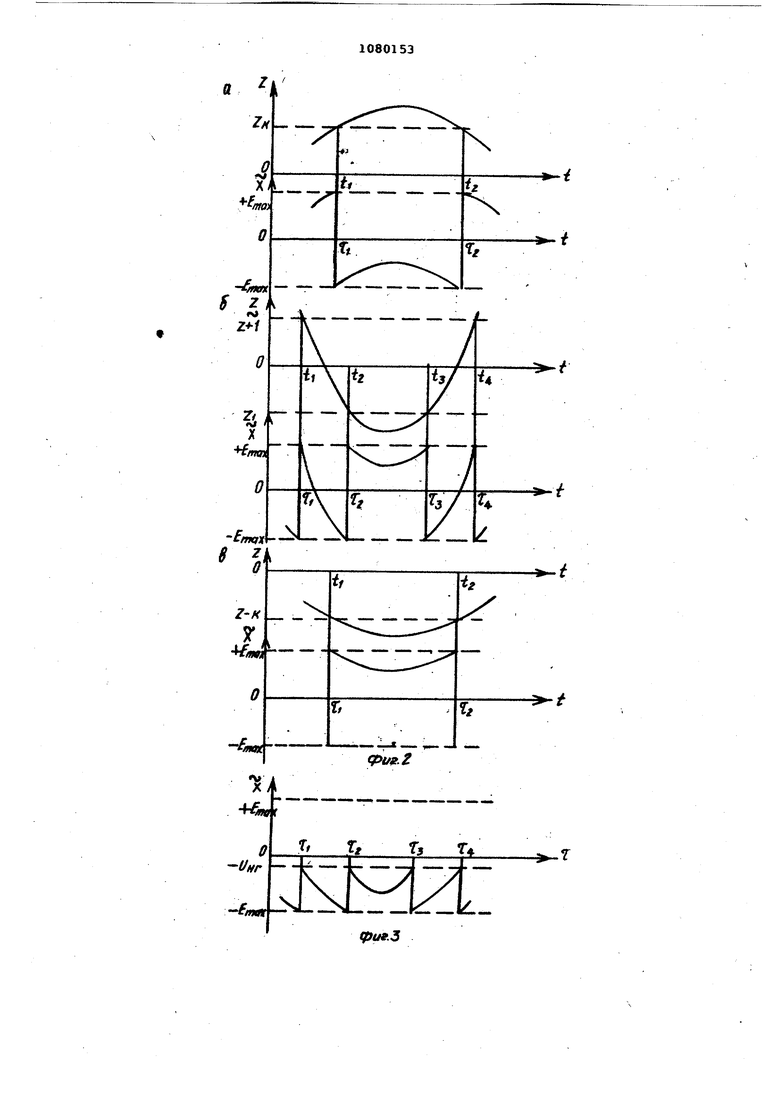

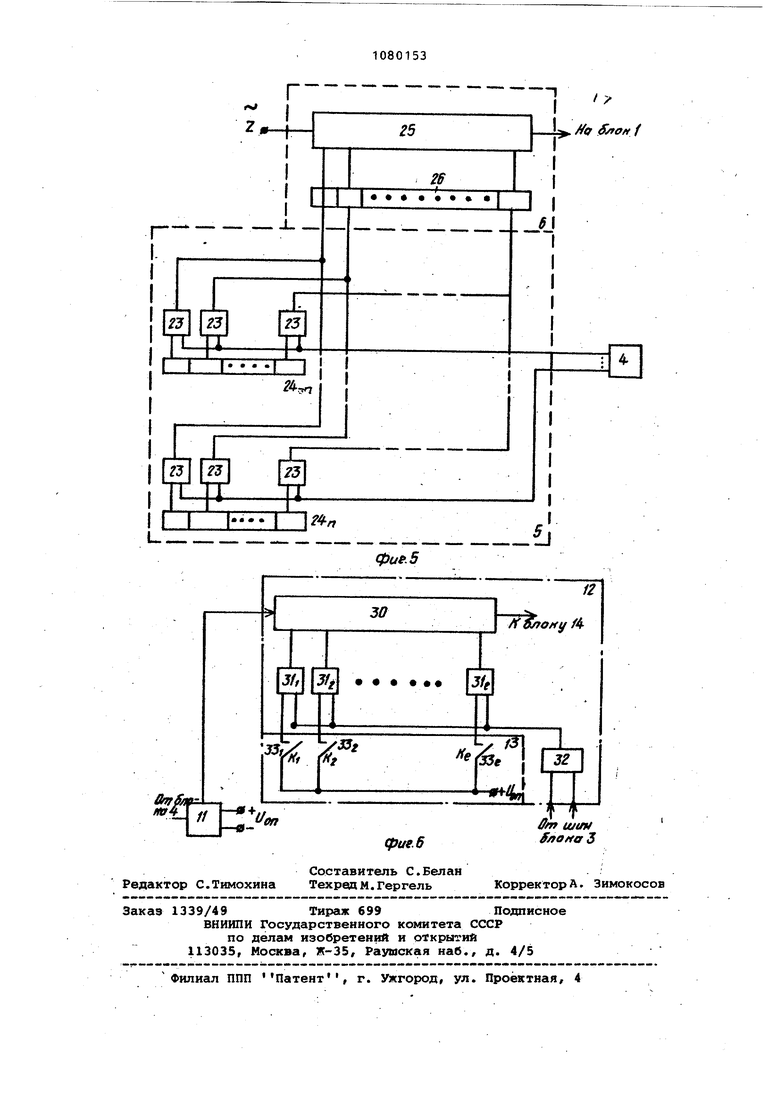

того, блок фиксации грании псддиапазона содержит два комnajpaxOpa, два разделительных диода и триггер, выходы которого являются импульсньво выходами блока, первые аходы компараторов объединены и являются входом блока, вторые входы компараторов подключены- к ши задания величины границы поддиапазона, выходы компараторов являются потенциальными выходами блока и через соответствуицие разделител ные диО|Ды соединены со счетным входом триггера. На фиг.1 представлена блок-схема предлагаемого устройства; на фиг. 2 - три варианта изменения переменной при постоянных и переменных масштабах; на фиг. 3 - фраг мент масштабируемой переменной; на фиг.4 - блок-схемы блоков фиксации границ поддиапазона, сопряжения и переключателя; на фиг.5 блок-схема запоминающего блока, соединенного с цифроуправляемым сопротивлением; на фиг. б - блоксхема формирования границы поддиапазона и блока задания кода. Устройство автоматической смены масштабов для аналоговой вычисл тельной машины (фиг.1) содержит операционный усилитель 1, блок 2 фиксации границ поддиапазона, блок 3 сопряжения, реверсивный счетчик импульсов 4, запоминающий блок 5, цифроуправляемое сопротивление б, ключи 7 - 10, переключатель 11, блок 12 формирования границы подди апазона, блок 13 задания кода, сум мирующий усилитель 14, интегрирую;ций конденсатор 15. Нафиг. 1, фиг.2, фиг.З обозначены:ист- опорное напряжение; 2 - входная машинная переменная; х - выходная машин ная переменная (масштабированная); гоах напряжение линейной зоны вычислительных блоков АВМ (например, t 100 В, + 50 В, ±10 В); напряжение нижней границы; t - машинное время; t - физическое время Блок 2 фиксации границ поддиапа зонов (фиг.4) содержит два компара тора 16 и 17, два разделительных диода 18 и 19, триггер 20 со счетным входом. Этот блок производит выработку и передачу ригнала в момент сравнения машинной переменной на выходе операционного усилителя 1 интегратора с напряжением гра ницы поддиапазона ч-КщакИли Блок 3 сопряжения (фиг.4) содер жит два многовходовых логических . элемента ИЛИ 21 и 22. Блок обуще.ствляет сопряжение масштаба данной переменной при функциональной связи ее с другими переменными, по которым производится также перемен ное масштабирование. Запоминающий блок 5 (фиг.5) содержит логические элементы И 23, регистры 24 чисел для положительны и отрицательных номеров поддиапазонов. Этот блок осуществляет хранение чисел в двоичном коде, определяющих коэффициент передачи операционного усилителя 1 на различных поддиапазонах переменной. Цифроуправляемое сопротивление 6 (фиг.5) содержит резистивную матрицу типа R-2R 25 и управляющий регистр 26, соединенный с выходами логичесг ких элементов И 23 каждого регистра 24 числа запоминающего блока. Переключатель 11 (фиг.4) содержит два многовходовых логических элемента ИЛИ 27 и 28, управляемый ключ 29, например двухобмоточное поляризованное реле. Этот блок осуществляет выдачу напряжения той или другой полярности в блок 12 формирования границы поддиапазона. Блок 12 формирования границы поддиапазона (фиг.б) содержит декодирующую резистивную матрицу типа R-2 30, логические элементы И 31, логический элемент ИЛИ 32. Блок осуществляет формирование напряжения границы поддиапазона и выдачи его.на вход сумматора 14. Блок 13 задания кода содержит тумблеры 33, где количество тумблеров соответствует коду, выставляемому на резистивной матрице. Вы- . ходы тумблеров подсоединены к логическим элементам И 31, а входы их подсоединены к положительному полюсу источника опорного напряжения +иоп. Данный блок осуществляет .задание кода, преобразуемого блоком 12 формирования границы поддиапазона в постоянное напряжение, соответствукадее границе поддиапазона . Устройство автоматической смены масштабов работает следующим образом. В зависимости от изменен.ия машинная переменная может пересекать +Е,пдхИЛИ поддиапаэоЪ|а (фиг.2а, б, в). Факт пересечения машинной переменной одной из границ служит началом рабочего цикла смены масштабов. В момент, показанный например, на фиг. 2а, происходит сравнение выходного напряжения, операционного усилителя 1 интегратора с напряжением границы +Е„а)1. Это сравнение происходит с помсяаью компаратора 16, на выходе которого образуется импульс, проходящий через разделительный диод 18 на счетный вход триггера 20 и на вход блока 3 сопряжения. Переход триггера 20 в противоположное состояние и образование при этом переходе сигнала управления дли пар ключей 8, 10 и 7, 9 приводит к тому, что, нёшример, первая пара, ключей 8,10 закрцвается, а вторая пара ключей 7,9 открывается. При

таком переключении ключей конденсатор 15 оказывается включеннымнаоборот т.е. вместо напряжения +E,)( на выходе операционного усилителя 1 интегратора оказывается , (фиг.2а) .Поскольку масштабируемая переменная возрастает, то процесс интегрирования происходит далее от ,. Рассматриваемый импульс с компаратора 16 поступает на вход логического элемента ИЛИ 22. По .другим входам этого элемента поступают сигнёшы от других устройств автоматической смены масштабов, с которыми функционально связана масштабируемая переменная. Сигналы от этих устройств вызывают изменение состояния реверсивного счетчика 4. Логические элементы ИЛИ 21 и 22 включены соответственно по шинам вычитания и сложения реверсивного счетчика 4, что обеспечивает переключение выходов реверсивного счетчика в сторону отрицательных или положительных номеров поддиапазонов разбиения. Рассматриваемая масштабированная переменная возрастет, поэтому с выхода логического элемента или 22 сигнал поступает по шине сложения на вход реверсивного счетчика 4, при этом на выходе реверсивного счетчика 4 происходит появление сигнала на выходе с номером +1 поддиапазона (т.е. происходит переключение выходов-с номера О, соответствующего нулевому поддиапазону, а на выход с номере +1, содтветствуквдего +1 поддиапазону). &ЛСОДЫ реверсивного счетчика 4 как положительных номеров поддиапазонов (+и) , так и отрицательных (-п) , подсоединены соответственно к логическнм элементам И 23 регистров чисел 24 , - 24 запоминающего блока 5 (фиг.5). В регистрах чисел 24 хранятся заранее рассчитанные значения коэффициентов передачи операционного усилителя 1 интегратора, соответствующие поддиапазонам разбиения. Выход разряда регистра числа подсоединен к логическому элементу И 23. Ввод инфо змадни, хранящейся в регистрах чисел 24 в управляющий регистр 26 цифроуправляемого сопротивления 6, происходит при подаче сигнала с соответствуквдего выхода реверсивного счетчика 4 на входы логических элементов И 23. Благодаря совпадению сигналов на входах соответствующих логических элементов И 23 содержимое регистра числа 24 переходит в управляющий регистр 26, выходы которого коммутируют соответствующие сопротивления реэистивной матрицы Ц-.-2R 25, чем обеспечивается необходимый для данного подциапа-зона коэффициент передачи. В резуль

тате появления сигнала на +1 выходе реверсивного счетчика и передачи его по адресному входу регистра числа 24( хранящееся в нем значение коэффициента передачи для +1 поддиапазона выставляется на цифроуправляемом сопротивлении, как это показано вьхле. Одновременно

.сигнал с реверсивного счетчика 4 (с выхода +1) поступает на вход переключателя 11 и, в частности, на вход логического элемента ИЛИ 28 (фиг.4). Этот элемент Объединяет

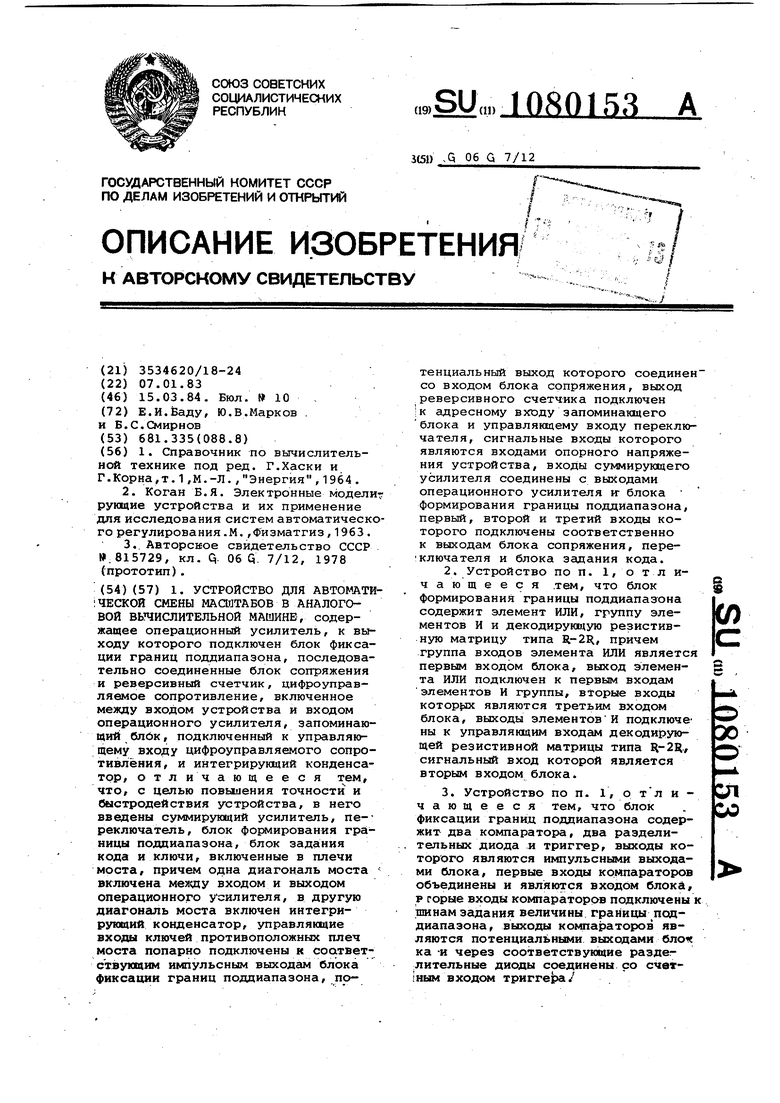

выходы реверсивного счетчика 4 положительных номеров поддиапазонов, логический элемент ИЛИ 27 объединяет выходы реверсивного счетчика отрицательных номеров поддиапазонов. Выходы обоих логических элементов ИЛИ 27 и 28 подсоединены к управляемому ключу 29 (фиг.4), например к обмотке поляризованногореле. Если на нулевом выходе реверсивного счетчика 4 есть сигнал, то на выходе управляемого ключа 29 сигнала нет, так как этот выход не подсоединен к логическим элементам ИЛИ 27 и 28. Поэтому, когда на выходе логического Элемента ИЛИ 28 образуется сигнал управления, то управляемым ключом 29 производится коммутация одного из полюсов источника опорного напряжения. В частности если масштабируемая переменная положительная, то коммутируется -Uoq, и наоборот. Смена знака полярности Поп происходит при переходе масштабируемой переменной через нулево поддиапазон. С выхода управляемого ключа 29 напряжение поступает на резистивную матрицу R-2R 30 блока формирования границы поддиапазона. К каждому разряду этой матрицы подсоединены выходы логических элементов И 31 (фиг.6). На один иэ входов этих элементов подсоединены соответственно выходы тумблеров 33 блока 13 задания кода. Код числа, определяющего значение границы поддиапазона, задается включением соответствующих тумблеров 33, с помсяцью которых на входы логических элементов И 31 подается положительное напряжение и on-К другим входам этих логических элементов подсоединен выход логического элемента ИЛИ 32 блока 12 формирования границы

поддиапазона. Появление сигнала на любом из входов логического элемента ИЛИ 32 приводит также к появлению сигнала на выходе.поступающего на входы логических элементов И 31, что обеспечивает передачу кода числа, выставленного на -гумj5nepax 33 для подключения соответствующих разрядов резистивной матрицы R-2R 30.Поскольку входы логиче

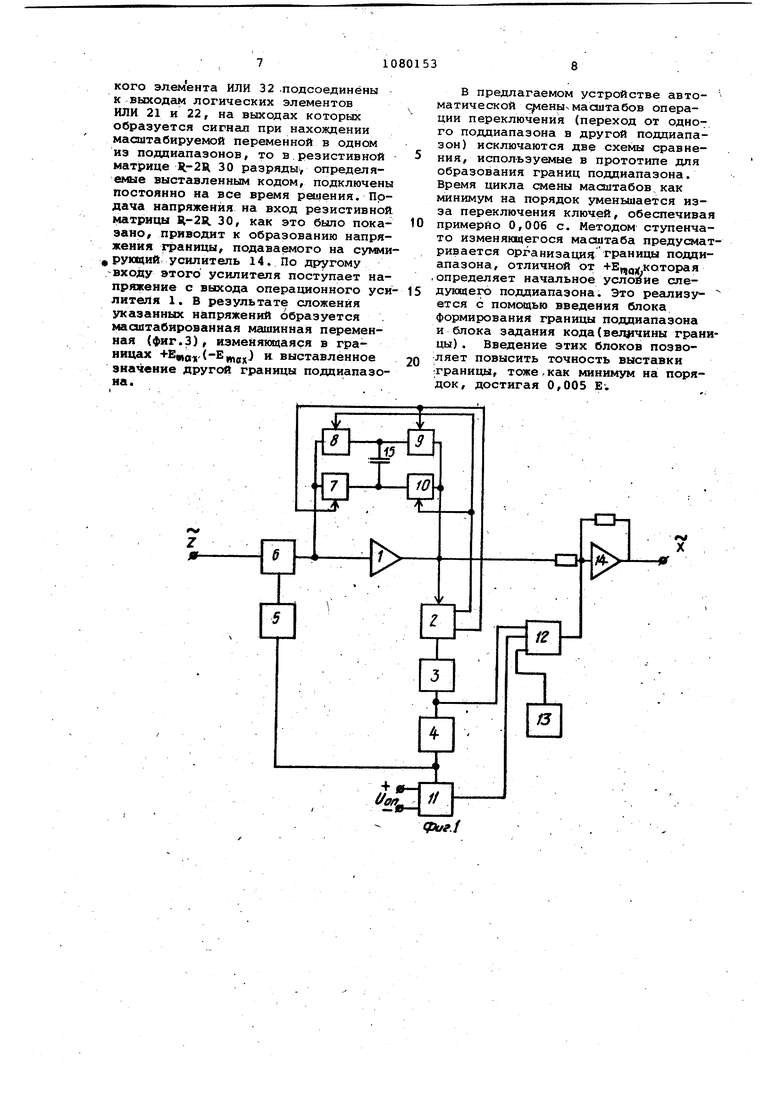

кого элемента ИЛИ 32 подсоединены к выходам логических элементов ИЛИ 21 и 22, на выходах которых образуется сигнал при нахождении масштабируемой переменной в одном из поддиапазонов то в резистивной матрице Я-2Я 30 разряды определяемые выставленным кодом, подключены постоянно на все время решения. Подача напряжения на вход резистивной матрицы Я-2Я 30, как это было показано, приводит к образованию напряжения границы, подаваемого на суммирующий усилитель 14. По другому входу этого усилителя поступает напряжение с выхода операхщонного усилитеЛя 1. В результате сложения указанных напряжений образуется масштабированная машинная переменная (фиг.З), изменяющаяся в границах .,,( и выставленное значение другой границы поддиапазона.

В предлагаемом устройстве автоматичecкoйc лeныs масштабов операции переключения (переход от одного поддиапазона в другой поддиапазон) исключаются две схемы сравне5 ния, используемые в прототипе для образования границ поддиапазона. Время цикла 1ены масштабов,как минимум на порядок уменьшается изза переключения ключей, обеспечивая

0 примерйо 0,006 с. Методом ступенчато изменяющегося масштаба предусматривается организация границы поддиапазона, отличной от ,/которая .определяет начальное условие сле5 дующего поддиапазона. Это реализу- ется с помощью введения блока формирования границы поддиапазона и блока задания кода (вел|1чины границы) . Введение этих блоков позвоQ ляет повысить точность выставки границы, тоже,как минимум на порядок, достигая 0,005 Е-.

i

i

i

1

фиеЛ

Г

/ ;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической смены масштабов для аналоговой вычислительной машины | 1983 |

|

SU1113809A1 |

| Аналого-цифровая вычислительная система | 1985 |

|

SU1320821A1 |

| Устройство для автоматической смены масштабов в аналоговой вычислительной машине | 1982 |

|

SU1080154A1 |

| Устройство для автоматической сменыМАСшТАбОВ B АНАлОгОВОй ВычиСлиТЕль-НОй МАшиНЕ | 1978 |

|

SU815729A1 |

| Аналого-цифровая вычислительная система | 1986 |

|

SU1420605A1 |

| Устройство для изменения масштабов в аналоговых вычислительных машинах | 1983 |

|

SU1195361A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство для изменения масштабов в аналоговых вычислительных машинах | 1974 |

|

SU489118A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

1. УСТРОЙСТВО ДЛЯ АВТОМАТЙ ЧЕСКОЙ СМЕНЫ МАШТАБОВ В АНАЛОГОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЕ, содержащее операционный усилитель, к выходу которого подключен блок фиксации границ поддиапазона, последовательно соединенные блок сопряжения и реверсивный счетчик, цифроуправляемое сопротивление, включенное между входом устройства и входом операционного усилителя, запоминающий блик, подключеннЕлй к управляющему входу цифроуправляемого сопротивления, и интегриругаций конденсатор , отличающееся тем, что, с целью повыиения точности и быстродействия устройства, в него введены суммирующий усилитель, пе-реключатель, блок формирования границы поддиапазона, блок задания кода и ключи, включенные в плечи моста, причем одна диагональ моста включена мелшу входом и выходом операционного усилителя, в другую диагональ моста включен интегрирующий конденсатор, управляющие входы ключей противоположных плеч моста попарно подключены к соатветствующим импульсным выходам блока фиксации границ поддиапазона,.потенциальный выход которого соединен со входом блока сопряжения, выход реверсивного счетчика подключен ;к адресному входу запоминагацего блока и управляющему входу переключателя, сигнальные входы которого являются входами опорного напряжения устройства, входы суммирующего усилителя соединены с выходами операционного усилителя к блока формирования границы поддиапазона, первый, второй и третий входы которого подключены соответственно к выходам блока сопряжения, переключателя и блока задания кода. 2.Устройство по п. 1, о т л иi чающееся .тем, что блок формирования границы поддиапазона содержит элемент ИЛИ, группу элементов И и декодирукт1то резистивную матрицу типа R-2R, причем группа входов элемента ИЛИ является первым входом блока/ выход элемента ИЛИ подключен к первым входс1М элементов И группы, вторые входы KOTOpiiK являются третьим входом О блока, выходы элементовИ подключе эо ны к управлякщим входам декодирующей резистивной матрицы типа 11-2Я/ сигнальный вход которой является вторым входом блока. сд 3.Устройство по п. 1, о тл и чающееся тем, что блок со фиксации гранид поддиапазона содержит два компаратора, два разделительных диода .и триггер, выходы которого являются импульсными выходами блока, первые входы компараторов объединены и являются входом блока, р горые входы компараторов подключены к шинам задания величины границы полдиапазона, выходы KOhoiapaторов являются потенциальными выходами блок ка -и через соответствующие разде.лительные диоды соединены со счет1ным входом триггера/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Справочник по вычислительной технике под ред | |||

| Г.Хаски и Г.Корна,т.1,М.-Л | |||

| /Энергия,1964 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Коган Б.Я | |||

| Электронные моделиг руюдие устройства и их применение для исследования систем автоматического регулирования.М | |||

| ,Фиэматгиз, 1963 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР | |||

| Устройство для автоматической сменыМАСшТАбОВ B АНАлОгОВОй ВычиСлиТЕль-НОй МАшиНЕ | 1978 |

|

SU815729A1 |

| Q | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-03-15—Публикация

1983-01-07—Подача