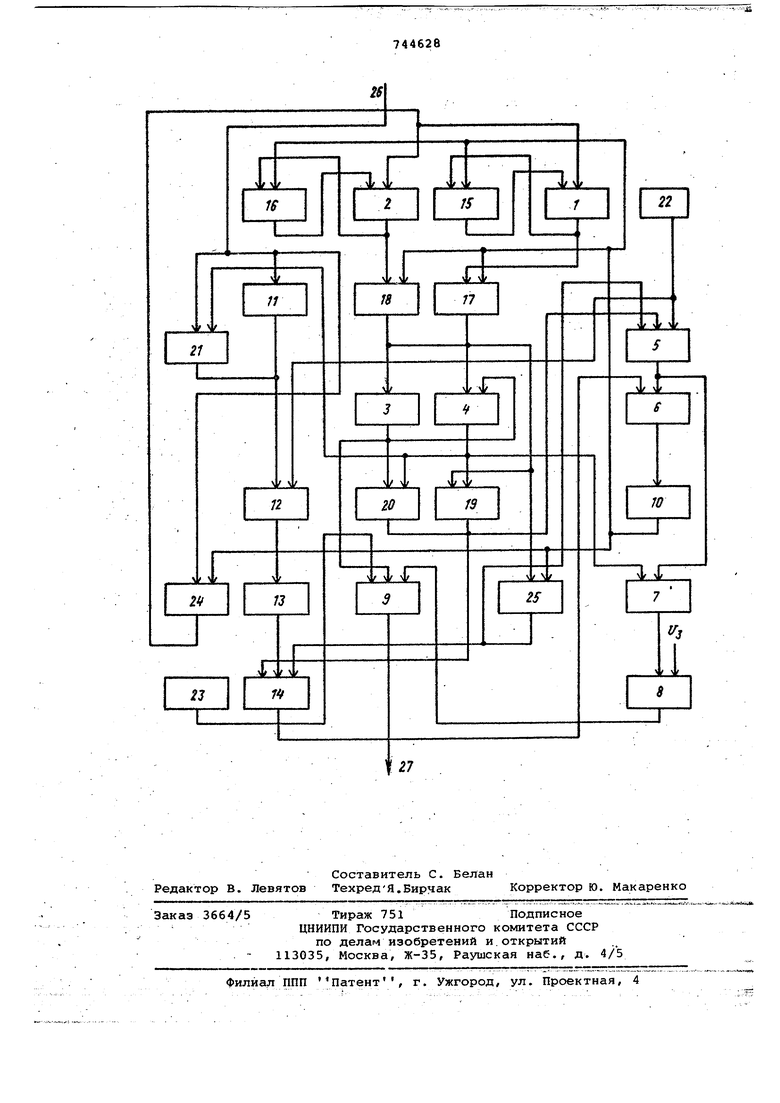

(54) ИНТЕГРАТОР Изобретение относится к области вычислительной техники и предназначено для использования в аналого-циф ровых устройствах различного назначения, в частности в аналого-цифровой вычислительной технике. Известен интегратор- по авт. св. 553630, содержащий первый интегри рующий усилитель, второй интегрирую щий усилитель, инвертор, блок определения знака, блок сравнения, блок управления, реверсивный счетчик, циф ро-управляюемую проводимость, сумма тор, логический элемент И-ИЛИ, первый дополнительный инвертор, дополн тельный, сумматор, второй дополнител .ный инвертор, дополнительный блок сравнения, первый, второй, третий, четвертый, пятый, шестой переключатели, дополнительный переключатель, источники опорного напряжения. В известном интеграторе временно и температурный дрейф напряжения смещения нуля и входного тока интегрирующих усилителей, старение компонентов (операционных усилителей, рез-исторов, конденсаторов) температурный гистеризис конденсаторов интегрирующих усилителей,- зависимость ;параметров компонентов от внешних условий (температура, влажность, давление, радиация) приводит к ошибкам интегрирования, т.к. известный интегратор используется для интегрирования длительных процессов,и в течение процесса интегрирования какая-либо профилактическая подстройка и подрегулировка, исключены. О111ибка интегрирования складывается из ошибок в определении времени переключения переключателей t и ошибок в определении значения интеграла от входного сигна.ла Uj. Целью настоящего изобретения является повышение точности интегрирования при воздействии дестабилизирующих факторов. Поставленная цель достигается тем, что в интегратор по авт .св. 553630 введены коммутатор каналов и блок памяти напряжения ошибки, при этом один вход коммутатора каналов подключен ко входной ине, другой вход - к выходу логического элемента И-ИЛИ, а выход коммутатора каналов подключен ко второму входу первого интегрирующего усил,ителя и ко второму входу второго интегрирующего усилителя, первый вход блока памяти-напряжения ошибки поякпочен к. выходам третьего и четвертого пере- ключателей, второй вход блока памят напряжения ошибки соединен с выходо логического элемента И-ИЛИ, а выход с третьим входом дополнительного бл ка сравнения и с третьим входом бло ка сравнения. На чертеже представлена блок-схе ма интегратора. Интегратор содержит первый интегрирующий усилитель 1, второй интегрирующий усилитель 2, инвертор 3, блок определения знака 4, блок срав нения 5, блок управления б, реверсивный счетчик 7, цифро-управляемую проводимость 8, сумматор 9, логичес кий элемент и-ИЛИ 10, первый дополнительный инвертор 11, дополнительн сумматор 12, второй дополнительный инвертор 13, дополнительный блок сравнения 14, первый, второй, третий четвертый, пятый, шестой переключатели 15, 16, 17, 18, 19, 20, дополнительный переключатель 21, источни ки опорного напряжения U , Uj 22, 2 коммутатор каналов 24,блок памяти н пряжения ошибки 25, входную ыину 26 входного сигнала U, шину 27 выходного сигнала Uy. Интегратор работает следующим образом. . При входном сигнале Uj О на вход ной шине 26 (интегратор включен) на счетчике 7 записан код 1000...О. Напряжение на выходе цифро-управляемой проводимости 8 будет пропорциЪнально произведению значения этого кода (так же как и для значения любого другого кода на ее входе) на значение опорного напряжения U цифро-управляемой проводимости 8. Напряжение с выхода цифро-управляемой проводимости В поступает на сумматор 9, к которому для компенсации ненулевого начального значения подключен второй источник опорного напряжения 23. ПрёДйЬлбжим, ;чго; начиная с на; чального момента времени, входное напряжение Uy интегрируется интегрирующим усилителем 1 или усилителем 2 что не имеет принципиального значения) . При этом на управляющих входах переключателей 15, 18, 16 и 17 управ ляющий сигнал имеет такое значение, что сигнальные цепи переключателей 15,18 разомкнуты, а переключателей 16,17 замкнуты. Блок определения знака 4 по сигналам на его входе с общей точки сиг нальных цепей переключателей 17, 18 и инвертора 3 через управляющие входы переключателей 19, 20 замыкает сигнгьльные цепи одного из этих переключателей таким образом, что на их общей точке получается напряжение одного определенного знака, т.е. фор Мируется модуль интеграла входного .напряжения U.

b-t Через инвертор 3, восстанавливаю щий фазу проинтегрированного входного сигнала, измененную на 180 интегрирующим усилителем 1, проинтегрированный входной сигнал поступает на сумматор 9, на выходе которого образуется алгебраическая сумма напряжений, поданных на его вход. Как только напряжение с общей точки сигнальных цепей переключателей 19, 20 сравнивается с первым опорным напряжением 0,( источники 22 на входе блока сравнения 5, на его выходе сформируется импульс, возбуждающий блок управления б и переводящий реверсивный счетчик 7 в ближайшее состояние по {+) или по (-) к счетной единице в зависимости от управляющегто сигнала с блока определения знака 4. В соответствии с новым кодом на выходе реверсивного счетчика 7 меняется значение напряжения на выходе цифро-управляемой проводимости 8 и соответственно на выходе сумматора 9 (выхбдная шина 27 результирующего напряжения Uy). При одновременном переключении переключателей 15, 16, 17, 18 на время перключения прерывается интегрирование входного сигнала. Для исключения этого целесообразно организовать последовательность переключений переключателей следующим образом. При интегрировании входного сигнала интегрирующим усилителем 1 переключатель 16 должен начать переключаться раньше, чем переключатели 15, 17, 18. При интегрировании входного сигнала усилителем 2 переключатель 15 должен начать переключаться раньше , чем переключатели 16, 17, 18. Оптимальный промежуток времени, на который раньше должен начать переключаться соответствующий переключатель, t , где tnep- время переключения переключателя. В этом случае к моменту начала выключения, например, усилителя 1 усилитель 2 включится (т.е. включаются к выключаются сигнальные цепи переключателей 15 и 16) и за время , пока разомкнется сигнальная цепь переключателя 17 и замкнется цепь переключателя переключения 18, на его выходе уже будет напряжение 4U где t - постоянная времени интегрирующих усилителей 1,2. Благодаря такой последовательности переключений переключателей входной сигнал UY, интегрируется непрерывно. Разрыв непрерывности в общей точке сигнальных цепей переключателей 17 и 18 кажущийся, так как после окончания процесса переключения в этой точке восстанавлибается истииное значение интеграла от входного напряжения, а ближайшее значение напряжения на выходе сумматора 9 поддерживается аналоговым запоминающим устройством, включающим в себя счетчик 7.и цифро-управляемую проводимость 8. Формирование указанной последовательности переключений с заданием не обходимых интервалов времени не долж ,но зависать от полярности и амплитуды входного сигнала. В противном слу чае устройство удастся настроить лиш для одного какого-то определенного значения входного сигнала. На выходе инвертора 11 формирует ся всегда отрицательное значение входного сигнала Uy, Для этого при положительном входном сигнале сигнальная цепь переключателя 21 разомк нута управляющим сигналом с блока оп ределения знака 4, при отрицательном входном сигнале и сигнальная цепь переключателя 21 замкнута. По каналу входного сигнала U на шине 26 сумматор 12 имеет коэффициент передачи равный К, по каналу пер вого опорногонапряжения с источника 22 коэффициент передачи равен единице. Напряжение на выходе сумматора 12 равно - (U -К-Цд), на выходе инвертора 13, формирующего необходимую фазу сигнала на входе блока сравнения 14 . Докажем, что;если опорное напряжение на входе блока сравнения 14 равно и -K-Uxf то промежуток бремени t Т-Т f где Т - время, за которое напряжение на выходе интегрирующего усилителя 1, или 2 достигне значения , не зависит от вход ного сигнала U. Т - время одного цикла интегрирования, т.е. время, з которое напряжение на выходе интегрирующего усилителя 1 или 2 изменится от нуля до и.-значения опорно го напряжения сравнения с выхода ис точника 22 на; входе сравнивающего устройства 5. t т-т Сигнал с выхода блока сравнения 1 поступает на вход блока управления 6 Блок управления б по сигналам с выходов блоков сравнения 5 и 14 через логический элемент и-ИЛИ 10 формирует необходимую последовательность управляющих сигналов переключателей 15, 16, 17, 18 с требуемыми временными характеристиками. Интервал времени t можно регулировать в любых пределах изменением .значения К и в том числе сделать его равным t- , -K-t Коммутатор каналов 24 поочередно подключает щину 26 входного сигнала и по сигналам с блока управления 6 Через логический элемент И-ИЛИ 10 к первому или второму интегрирующим усилителям 1, 2. Один из интегрирующих усилителей 1, 2 который в данном цикле интегрирования Интегрирует входной сигнал, подключается к шине 26, другой - отключается от шины 26. Конденсатор в цепи обратной связи отключенного интегрирующего усилителя 1 или 2 начинает разряжаться через замкнутую сигнальную цепь переключа геля 15 или 16. Начальное значение Напряжения, с которого конденсатор начнет разряжаться, известно и равно первому опорному напряжению Од источ.;ника 22 на блока сравнения 5, т.к. момент сравнения первого опорного напряжения на входе сравнивающего устройства 5 с выходным напряжением соответствующего интегрирующего усилителя определяет конец цикла интегрирования. Постоянная времени интегрирующих усилителей t также известна, поэтому известнои время, за которое соответствующий конденсатор интегрирующего усилителя должен разрядиться до нуля. Блок управления 6 формирует указанный промежуток времени, в конце которого размыкает сигнальную цепь. соответствующего переключателя 15 или 16. Соответствующий интегрирующий усилитель 1 или 2 переходит в режим хранения остаточного значения напряжения на конденсаторе, отличие которого от нулевого значения представляет .собой напряжение ошибки, вызванное различными дестабилизирующими факторами. Напряжение ошибки переписывается через переключатель 17 или 18 в блок памяти напряжения ошибки 25, после чего соответствующий интегрирующий усилитель 1 или 2 готов к интегрированию входного сигнала Uy на шине 2j5. Выход блока памятиiнапряжения, ошибки 25 подключается ко входам блоков сравнения 14 и 5. Полярность и величина корректирующего напряжения .ошибки на входах блоков сравнения 14 и 5 такова, что значение напряжения огибки соответствующего интегрирующего усилителя 1 или 2 Скомпенсируете я. Таким образом поочередно измеряются напряжения ошибки интегрирующих усилителей 1 или 2, которые в общем, отличаются друг от друга, и в те циклы интегрирования, в течение которых соответствующий интегрирующий усилитель 1 или 2 интегрирует входной сигнал Uj на шине 26, происходит компенсация соответствующего сигнсша ошибки интегрирующего усилителя 1 или 2 соответствующим компенсирующим напряжением.

Порядок функционирования блока памяти напр:яжения ошибки 25 определяется управляющими, сигналами с блока управления 6 через логический элемент И-ИЛИ 10.

Благодаря указанной коррекции время tfigf, не зависит от влияния различных дестабилизирующих факторов. Попутно повышается точность интегрирования за счет компенсации ошибки интегрирующих усилителей 1 или 2 на входе блока сравнения 5

Использование Новых элементов - коммутатора каиалов, корректора ошибки выгодно отличает предлагаемый интегратор 3т указанного прототипа, т.к. исключаются ошибки интегрирования, связайные с временным и температурным дрейфом напряжения смещения нуля и входного тока интегрирующих усилителей, со старением компонентов (операционных усилителей, резисторов, конденсаторов), с температурным гистеризисом конденсаторов интегрирующих усилителей , с зависимостью параМетров компонентов от внешних условий (температура, влажность, давление, радиация), т.е. предлагаемый интегратор самоподстраивается и самокалибруется, что принципиально важно

|при интегрировании длительных процессов, для интегрирования которых предназначен предлагаемый интегратор, когда профилактическая подстройка и подрегулировка исключены и (или) при интегрировании относительно коротких процессов, когда присутствие оператора исключается (атомные р еакторы, ракеты и другое специальное оборудование) .

Формула изобретения

Интегратор по авт. св., 553630, отличающийся тем, что, с целью повышения точности интегрирования при воздействии дестабилизирующих факторов, в него введены коммутатор каналов и блок памяти напряжения ошибки, при этом один вход коммутатора каналов подключен к входной шине, другой вход - к выходу логического элемента И-ИЛИ, а выход коммутатора каналов подключен ко второму входу первого интегрирующего усилителя и ко второму входу второго интегрирующего усилителя-, первый вход блока памяти напряжения ошибки подключен к выходам третьего и четвертого переключателей, второй вход блока памяти напряжения ошибки соединен с выходом логического элемента И-ИЛИ а выход - с третьим входом дополнительного блока сравнения и с третьим входом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1975 |

|

SU553630A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Устройство для оценки работы операторов | 1987 |

|

SU1441442A1 |

| Преобразователь сигнала в его среднее значение | 1978 |

|

SU748135A1 |

| Цифроаналоговая следящая система | 1989 |

|

SU1700536A1 |

| Устройство для контроля параметров инерционных звеньев | 1979 |

|

SU873248A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1636841A1 |

| Дискретно-аналоговый интегратор | 1976 |

|

SU611218A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

.

Авторы

Даты

1980-06-30—Публикация

1978-02-20—Подача