1-| .1

4ib

to

О Oi

о сд

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система | 1985 |

|

SU1320821A1 |

| Устройство автоматической смены масштабов для аналоговой вычислительной машины | 1983 |

|

SU1113809A1 |

| Устройство для автоматической смены масштабов в аналоговой вычислительной машине | 1983 |

|

SU1080153A1 |

| Устройство для автоматической смены масштабов в аналоговой вычислительной машине | 1982 |

|

SU1080154A1 |

| Устройство для изменения масштабов в аналоговых вычислительных машинах | 1983 |

|

SU1195361A1 |

| Устройство для автоматической сменыМАСшТАбОВ B АНАлОгОВОй ВычиСлиТЕль-НОй МАшиНЕ | 1978 |

|

SU815729A1 |

| Датчик сил упругой деформации механизма и устройство для его настройки | 1985 |

|

SU1288511A1 |

| Сумматор | 1982 |

|

SU1053114A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является повьшение быстродействия решения векторно-матричных уравнений X АХ + BU с большими значениями элементов матрицы А и вектора-столбца В. Аналого-цифровая вычислительная система содержит шины 1 и 2 передачи мантисс переменных и коэффициентов, шины 3 и 4 передачи порядков переменных и коэффициентов, шину 5 ввода начальных условий и ряд решающих ячеек 6, каждая из которых содержит две группы цифроуправляемых резисторов 7 и 8, три операционных усилителя 9, 13..и 21, весовые резисторы 10, 20 и 22, вычислители -Пи 16 порядков сумматора и интегратора, устройства 12 и 17 автоматической смены масштабов сумматора и интегратора, усилитель 14 с регулируемым коэффициентом усиления, блок 15 переключения емкости, цифроуправляемый резистор 18 начальных условий и управляемый источник 19 опорного напряжения. Повышение быстродействия обеспечивается на основе реализации режима непосредственной корректировки масштабов представления переменных в моменты времени выхода переменных за границы поддиапазонов , 2 З.п.ф-лы, 4 ил. (Л

L.

..h

Фиг.1

Изобретение относится к автоматике и вычислительной технике, в частности к моделированию физических процессов на аналого-цифровых вычислительных системах.

Цель изобретения - повышение быстродействия решения векторно-матричных уравнений X АХ + BU с большими значениями элементов матрицы А и векто- ра-столб,ца Во

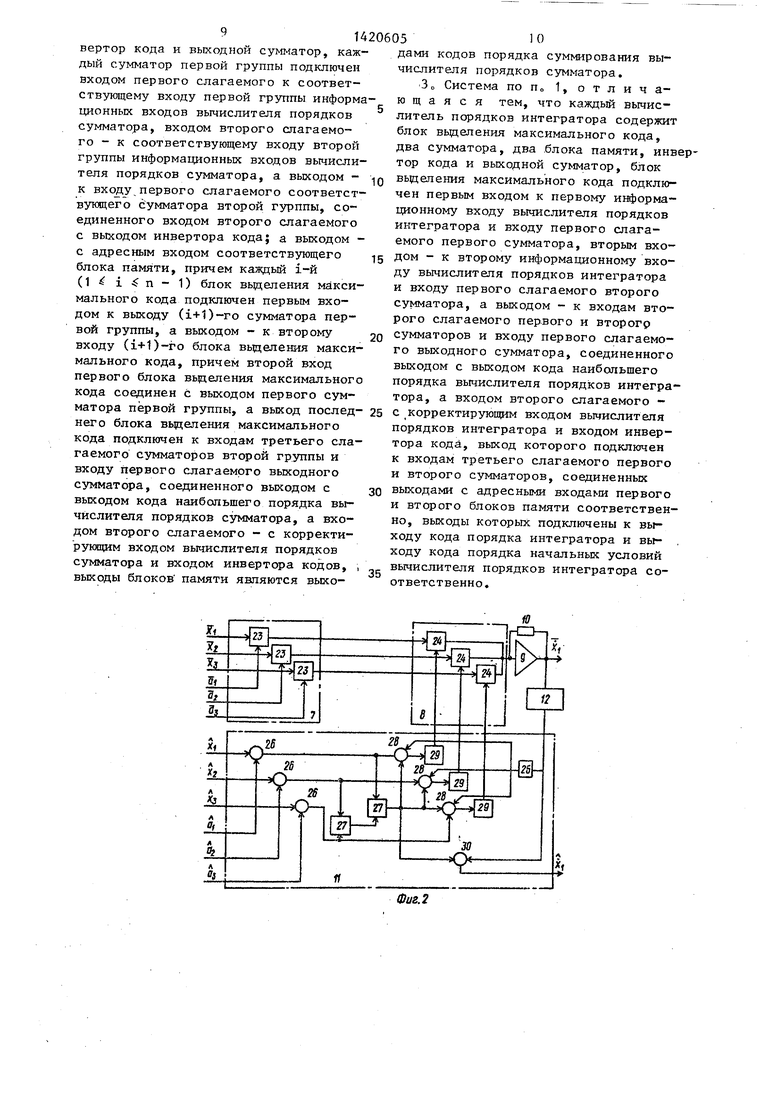

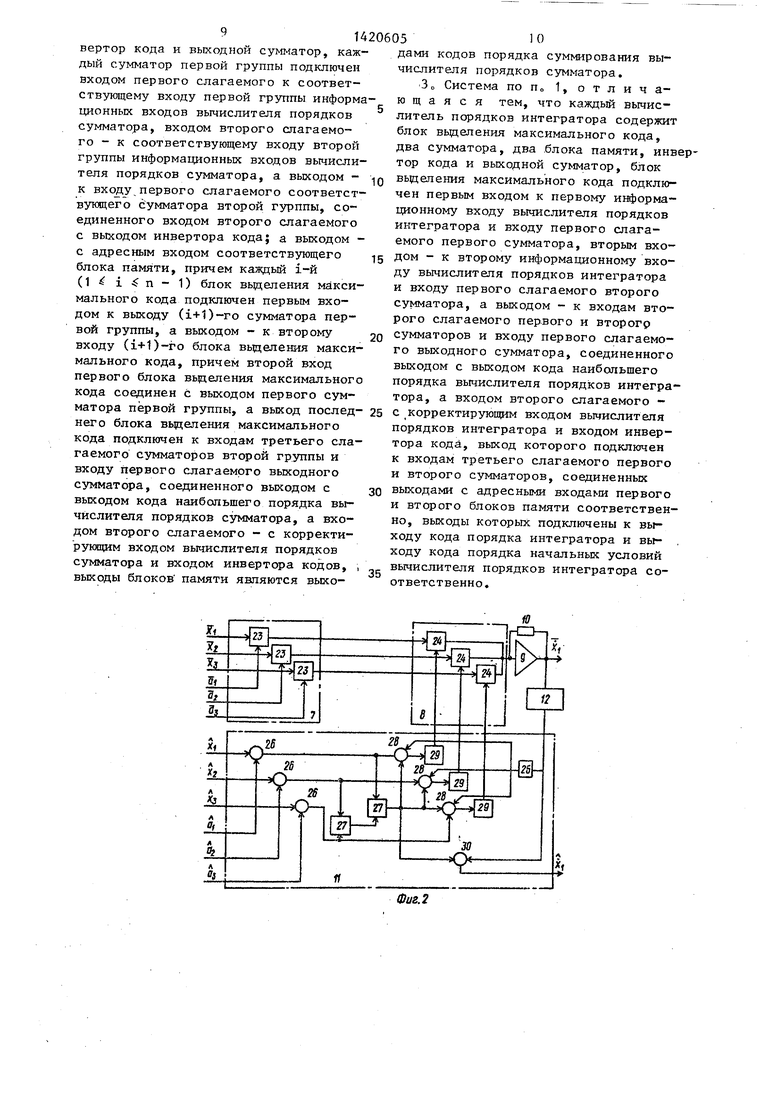

На фиг о 1 изображена блок-схема аналого-цифровой вычислительной системы (АЦВС); на фиг 2 - блок-схема вычислителя порядков сумматора (ВПС) и его подключения к узлам решакнцей ячейки; на фиг. 3 - блок-схема вычислителя порядков интегратора (ВПИ) и его подключения, к узлам решающей ячейки; на фиг„ 4 - блок-схема бло-

1

ка вьщеления максимального кода

Аналого-цифровая вычислительная система содержит (фиг, 1) шину 1 передачи з.начений мантисс переменных, шину 2 передачи мантисс коэффициентов, шину 3 передачи порядков переменных, шину 4 передачи порядков коэффициентов, шину 5 ввода начальных условий (порядков и мантисс переменных) и п решакяцих ячеек 6,-6, Каждая решающая ячейка 6{(1 1, ,,., п содержит первую группу 7 цифроуправ- ляемых резисторов (ЦУР), вторую группу 8 цифроуправляемых резисторов (ЦУР), первый операционный усилитель 9 с первым весовым резистором 10 в цепи обратной связи, вычислитель 11 порядков сумматора, устройство 12 автоматической смены масштабов сумматора (УАСМС), второй операционный усилитель 13, усилитель 14 с регулируемым коэффициентом усиления, блок

15переключения емкости, вычислитель

16порядков интегратора, устройство

17автоматической смены масштабов интегратора (УАСМИ), цифроуправля- емьм резистор 18 начальных условий, управляемый источник 19 опорного напряжения, второй весовой резистор 20 и третий операционный усилитель 21

с третьим весовым резистором 22 в цепи обратной связи. Первая и вторая группа 7 и 8 содержат по m цифроуправляемых резисторов 23 и 24 (фиг,2) где m - отражает порядок реализуемой системы векторно-матричных уравнений.

Вычислитель порядков сумматора 11 (фиг, 2) содержит инвертор 25 кода.

20

10

206052

первую группу сумматоров 26, группу блоков 27 вьделения максимального кода, вторую группу сумматоров 28, группу блоков 29 памяти и выходной сумматор 30,

Вычислитель 16 порядков интегратора (фиг, 3) содержит выходной сумматор 31, блок 32 вьделения максимального кода, два сумматора 33, два блока 34 памяти и инвертор 35 кода.

Каждый из блоков 27 и 32 вьщеле- ния максимального кода может быть выполнен (фиг, 4) на двух группах 15 элементов И 36, схеме сравнения кодов 37 и элементе НЕ 38,

На блок-схемах приняты следующие обозначения: х j и а,-, - мантиссы переменных и коэффициентов соответственно; j и а у: - порядки переменных и коэффициентов; Р; - значения поряд5

0

5

0

5

0

5

ка; X Qj - начальное условие мантиссы переменной.

Работа аналого-цифровой вычислительной системы основана на использовании метода ступенчатого изменения масштабов

Согласно этому методу при моделировании векторно-матричного уравнения типа X Ах + ви составляется объединенная матрица, состоящая из столбцов матрицы А и столбца вектора В, Элементы этой матрицы представляются в нормальной форме, т,е, , где о(- мантисса; Р - порядок; Е - основания системы очисления, Е 10, Далее объединенная матрица разделяется на матрицу мантисс и матрицу порядков и производится нормализация матрицы порядков - вынесение максимального порядка из каждой строки, образуя, таким образом, матрицу-столбец порядков производных, В соответствии со значениями элементов нормализованной матрицы порядков производится изменение значений элементов в матрице мантисс с последующей их выставкой, на аналоговой части системы через интерфейс ..сопряжения на соответствующих цифроуправляемых резисторах, включенных на входах сумматоров модели Значение элементов матрицы- столбца порядков производных также . выставляют через интерфейс сопряжения на соответствующих цифроуправляемых резисторах интеграторов модели. При выходе какой-либо переменной на границу поддиапазона производят ступенчатое изменение масштаба, что оз-

начает соответствующее увеличение или уменьшение порядка на единицу. Ступенчатое изменение масштаба по производной (выход на границу поддиапазона выходной машинной переменйой сумматора) приводит к изменению соответствующего элемента в матрице- столбце порядков производных и одновременно взаимообратное изменение значений управляемых сопротивлений обратной связи сумматора и на входе интегратора, соединенного с этим суммы 37 и элемента 38, которые подсоединены к группам элементов И 36. Таким образом, на выходе блока 27 о разуется больший из двух сравниваемых кодов. Кодовое значение максимального порядка поступает на вход всех сумматоров 28, куда соответств но на другие входы поступает кодово значение с выходов сумматоров 26, На сумматорах 28 происходит вычитание значения максимального порядка из порядков коэффициентов (операция нормализации). С выхода каждого сум

матором. При выходе на границу поддиапазона какой-либо переменной (выход- 15 матора 28 значение нормализованного ная машина переменная интегратора) порядка поступает на адресный вход производится изменение значения соответствующего элемента в нормализованной матрице порядков с последующей „ коррекцией значения его мантиссы в 20 матрице мантисс и изменением значений соответствующих регистров на входах сумматоров модели. Если значение порядка в нормализованной матрице порядков превьшзает нулевр.е значение, то производят нормализацию строки, в которую входит этот элемент, и соответствующую коррекцию значений элементов в матрице-столбце порядков

соответствующего блока 29 памяти, в котором реализована функциональная зависимость перехода от значения порядка в двоичном коде к значению порядка в десятичном коде. Это значение порядка реализуется на цифроуп- равляемых резисторах 24 второй группы 8. Одновременно значение максимал

25 ного порядка через сумматор 30 посту пает на сумматор 33 (положим, что начальных условий нет) и аналогично через блок 34 памяти реализуется на усилителе 14 с регулируемым коэффипроизводных и в матрице мантисс с последующей выставкой этих значений на соответствуюш 1х резисторах модели.

В режиме инициализации (фиг„ 1) на цифроуправпяемых резисторах пер30 циентом усиления в виде соответствующего коэффициента передачи о Так как усилитель 14 с регулируемым коэффициентом усиления включен в обратную связь операционного усилителя 13 в режиме интегрирования, то общий коэф

вой группы 7 выставляются числовые значения мантисс коэффициентов векторно- фициент передачи интегратора увели-

матричного уравнения, передаваемые по.шине 2 мантисс коэффициентов . Одновременно по шине 4 порядков этих коэффициентов передаются кодовые зна- чения порядков на сумматоры 26 вычислителя 11 (кодовые значения порядков передаются четьрехразрядным кодом - 3 разряда значения порядка, один разряд - знак порядка; 3 разряда значений порядка полностью включают диапазон реализуемых порядков устройств). По другим входам сумматоров 26 поступают логические нули. На блоках 27 производится попарное сравнение выходных значений сумматоров 26, определяя максимальный порядок. Значения кодов поступают на схему 37 сравнения (фиг, 4),на выходе которой образуется сигнал логического нуля или единицы в зависимости от того, какой код числа на входе блольше. Соответственно организуется разрешающий сигнал непосредственно с выхода схе

420605

мы 37 и элемента 38, которые подсоединены к группам элементов И 36. Таким образом, на выходе блока 27 образуется больший из двух сравниваемых кодов. Кодовое значение максимального порядка поступает на вход всех сумматоров 28, куда соответственно на другие входы поступает кодовое значение с выходов сумматоров 26, На сумматорах 28 происходит вычитание значения максимального порядка из порядков коэффициентов (операция нормализации). С выхода каждого сум- 15 матора 28 значение нормализованного порядка поступает на адресный вход 20матора 28 значение нормализованного порядка поступает на адресный вход

соответствующего блока 29 памяти, в котором реализована функциональная зависимость перехода от значения порядка в двоичном коде к значению порядка в десятичном коде. Это значение порядка реализуется на цифроуп- равляемых резисторах 24 второй группы 8. Одновременно значение максимального порядка через сумматор 30 поступает на сумматор 33 (положим, что начальных условий нет) и аналогично через блок 34 памяти реализуется на усилителе 14 с регулируемым коэффициентом усиления в виде соответствующего коэффициента передачи о Так как . усилитель 14 с регулируемым коэффициентом усиления включен в обратную связь операционного усилителя 13 в режиме интегрирования, то общий коэффициент передачи интегратора увели-

5

Q

0

5

чивается на величину максимального (определенного в. процессе нормализации) порядка. Указанные вьш1е операции происходят во всех решающих ячейкахо

В режиме решения работа системы происходит следующим образом

Положим, что мантисса переменной X возрастает и достигла верхней границы поддиапязона, устанавливаемого устройством 12, На выходе кода масштаба устройства 12 возникает единичный код, который через инвертор 25 поступает на вход второго слагаемого каждого сумматора 28, что приводит к уменьшению на единицу значения вькод- ного кода этих сумматоров. В связи с этим на выходах блоков 29 памяти значение десятичного порядка уменьшается на единицу. Одновременно на выходе сумматора 30 значение кода порядка увеличивается на единицу, что влечет за собой увеливение порядка

1

с регулируемым коэффициентом усиления. Таким образом, коэффициент передачи интегратора усилителя 13 с блоком 15 переключения емкости увеличивается на порядок. Аналогично действия происходят при уменьшении мантиссы переменной х , только в сумматорах 28 прибавляется единица, что влечет за собой увеличение порядка (коэффициента передачи на порядок) на резисторах 24, а у интегратора уменьшение на порядок коэффициента передачи за с чет изменения на порядок коэффициента усиления на усилителе 14о

Положим, что, возрастая, границы диапазона достигла мантисса х,. Тогда с выхода УАСМИ 17 единичный код через инвертор 35 поступает на сумматор 33 и, вычитаясь, уменьшает значение выходного кода сумматора 33 на единицу, что приводит к уменьшению

ющие значения порядков на выходах сумматоров 28 поступают на блоки 29 памяти. В результате этой операции на резисторах 24 реализуются новые значения коэффициентов передач, соответствующие новым значениям порядков. На усилителе 14 устанавливается

JO новый коэффициент усиления, соответствующий новому порядку, значение которого передается через сумматор 30, сумматор 33, блок 34 памяти.

При задании начальных условий ман-15 тисса X ния,

ков начальных условий. Значение порядка начальных условий поступает на блок 32 и на сумматор 33. В результа20 те сравнения максимального порядка при нормализации порядков коэффициентов с порядком начальных условий х, результирующее значение порядка с выхода блока 32 поступает на сумматоры

01

задается в виде напряже- а порядок XQ;,- по шине 5 порядна порядок коэффициента передачи уси- 25 33„ где вычитается от значений поряд- лителя 14, а следовательно, интегратора. Одновременно единичный код с выхода УАСМИ 17 проходит через(сумматор 31 (поскольку начальные условия отсутствуют, то по другому входу сумматора 31 поступает логический нуль) и постз пает по шине 3 порядков переменных на входы соответствующих сумматоров 26 в решаюгщх ячейках. В рассматриваемой решающей ячейке (фиг. 2) значение кода с выхода сумматора 31 Поступает на вход сумматора 26, где складывается с порядком соответственно а При этом могут возникнуть 2 режима. Если порядок на выходе сумматора 26 не превосходит максимальный порядок, установленный в режиме инициализации, то на

ков, поступающих по другим входам. Результирующие значения порядков с выходов сумматоров 33 поступают на блоки 34 памяти, устанавливая соответ- 30 ствующий коэффициент усиления на усилителе 14 и соответствунлций коэффициент передачи на резисторе 18 началь- ных условий по входу операционного усилителя 21.

ЗЦ

Смена масштабов УАСМИ 17 по мантиссе х происходит следуюш;им образом.

Выходной Импульс производит в блок 15 переключение e кocти интегра- 40 тора в цепи усилителя 13 и одновременно подключает соответствующее значение опорного напряжения на управляемом источнике 19 опорного напряжения, образуя, таким образом.

Выходной Импульс производит в блок 15 переключение e кocти интегра- 40 тора в цепи усилителя 13 и одновременно подключает соответствующее значение опорного напряжения на управляемом источнике 19 опорного напряжения, образуя, таким образом.

Таким образом, в предлагаемой аналого-цифровой вычислительной сисоответствующем цифроуправпяемом резисторе 24 через цепочку сумматор значения границ поддиапазона измене- блок 29 памяти устанавливается коэф- ния мантиссы XT фициент передачи по данному входу усилителя 9, увеличенный на порядок Аналогичные операции происходят и в

других решающих ячейках, куда на соот-5о стеме установка масштабов (порядков ветствующий рход по амне 3 порядков представления переменных и коэффи- переменных поступает х,. Если порядок циентов) в процессе работы происхо- на вькоде сумматора 26 превосходит дит не на каждом этапе обмена с циф-,

ровой вычислительной машиной, а по 55 мере возникающей необходимости (в момент времени выхода переменных на границы поддиапазонов), что обеспечивает повышение быстродействия решения векторно-матричных уравнений.

максимальный порядок, то происходит перенормализация (значения порядков сравниваются на блоках 27 и определяется новое значение максимального i порядка, которое вычитается из значений порядков на выходах сумматоров

ющие значения порядков на выходах сумматоров 28 поступают на блоки 29 памяти. В результате этой операции на резисторах 24 реализуются новые значения коэффициентов передач, соответствующие новым значениям порядков. На усилителе 14 устанавливается

новый коэффициент усиления, соответствующий новому порядку, значение которого передается через сумматор 30, сумматор 33, блок 34 памяти.

При задании начальных условий ман-5 тисса X ния,

ков начальных условий. Значение порядка начальных условий поступает на блок 32 и на сумматор 33. В результа0 те сравнения максимального порядка при нормализации порядков коэффициентов с порядком начальных условий х, результирующее значение порядка с выхода блока 32 поступает на сумматоры

01

задается в виде напряже- а порядок XQ;,- по шине 5 поряд33„ где вычитается от значений поряд-

ков, поступающих по другим входам. Результирующие значения порядков с выходов сумматоров 33 поступают на блоки 34 памяти, устанавливая соответ- ствующий коэффициент усиления на усиителе 14 и соответствунлций коэффициент передачи на резисторе 18 началь- ных условий по входу операционного усилителя 21.

Смена масштабов УАСМИ 17 по мантиссе х происходит следуюш;им образом.

Выходной Импульс производит в блок 15 переключение e кocти интегра- тора в цепи усилителя 13 и одновременно подключает соответствующее значение опорного напряжения на управляемом источнике 19 опорного напряжения, образуя, таким образом.

значения границ поддиапазона измене- ния мантиссы XT

Таким образом, в предлагаемой аналого-цифровой вычислительной сизначения границ поддиапазона измене- ния мантиссы XT

7 -1А20605

ормула изобретения

ля нен пер от .С ц шен X эле ца нит ков инт тор это под ход тич пер к в рем ных чи вых к у рез код му пор кор мас сме инф да мен рат тел уси чал дом дан фор к ш пер вьт ног го с в тел ка каж чен пер

ля каждой из п решаюш 1х ячеек соединен с соответствующим входом шины передачи значений мантисс переменных отличающаяся тем, что, .С целью повьш1ения быстродействия решения векторно-матричных уравнений X АХ + Ви с большими значениями элементов матрицы А и вектора-столбца В, в каждую решающую ячейку дополнительно введены вьмислитель порядков сумматора, вычислитель порядков интегратора и цифроуправляемый резистор задания начальных условий, при этом вычислитель порядков сумматора подключен корректирующим входом к выходу кода масштаба устройства автоматической смены масштабов сумматора, первой группой информационных входов к выходам шины передачи порядков переменных, второй группой информационных входов - к выходам шины передачи порядков коэффициентов, группой выходов кодов порядков суммирования - к управлякщим входам цифроуправляемых резисторов второй группы, а-выходом кода наибольшего порядка, - к первому информационному входу вычислителя порядков интегратора, соединенного корректирующим входом с выходом кода масштаба устройства автоматической смены масштабов интегратора, вторым информационным входом - с шиной ввода начальных условий порядков переменных, выходом кода порядка интегратора - с управляюш 1м входом усилителя с регулируемым коэффициентом усиления, а выходом кода порядка начальных условий - с управляющим входом цифроуправляемого резистора задания начальных условий, первый ин- формационный вывод которого подключен к шине ввода начальных условий мантис переменных, а второй информационный вьтод - к входу третьего операционного усилителя, при этом выход первого операционного усилителя соединен с входом второго операционного усилителя, а выходы кода наибольшего порядка вычислителя порядков интегратора каждой из п решающей ячейки подклю- чен к соответствующему входу шины передачи порядков переменных.

блока памяти, причем каждьй i-й

(1 i п - 1) блок вьщеления максимального кода подключен первым входом к выходу (i+1)-ro сумматора первой группы, а выходом - к второму входу (1+1)-го блока вьделения максимального кода, причем второй вход первого блока вьделения максимального кода соединен с выходом первого сумматора первой группы, а выход послед- него блока вьиеления максимального кода подключен к входам третьего слагаемого сумматоров второй группы и входу первого слагаемого выходного сумматора, соединенного выходом с выходом кода наибольшего порядка вычислителя порядков сумматора, а входом второго слагаемого - с корректирующим входом вычислителя порядков сумматора и входом инвертора кодов, выходы блоков памяти являются выхо

дами кодов порядка суммирования вычислителя порядков сумматора,

Зо Система по п 1, отличающаяся тем, что каждый вычислитель порядков интегратора содержит блок вьделения максимального кода, два сумматора, два .блока памяти, инвертор кода и выходной сумматор, блок вьделения максимального кода подключен первым входом к первому информационному входу вычислителя порядков интегратора и входу первого слагаемого первого сумматора, вторым вхо- дом - к второму информационному входу вычислителя порядков интегратора и входу первого слагаемого второго суь1матора, а выходом - к входам второго слагаемого первого и второгр сумматоров и входу первого слагаемого выходного сумматора, соединенного выходом с выходом кода наибольщего порядка вычислителя порядков интегра

тора, а входом второго слагаемого - с корректирующим входом вычислителя порядков интегратора и входом инвертора кода, выход которого подключен к входам третьего слагаемого первого и второго сумматоров, соединенных выходами с адресными входами первого и второго блоков памяти соответственно, выходы которых подключены к выходу кода порядка интегратора и вы- , ходу кода порядка начальных условий вычислителя порядков интегратора соответственно.

X,

Г

J7

22

Фи8,3

36

-

L1K

п-К

А

36

27(52}

(риг.

| Витенберг И.М., Программирование аналоговых вычислительных машин | |||

| М.: Машиностроение, 1972, .с | |||

| Способ получения продукта конденсации бетанафтола с формальдегидом | 1923 |

|

SU131A1 |

| Аналого-цифровая вычислительная система | 1985 |

|

SU1320821A1 |

Авторы

Даты

1988-08-30—Публикация

1986-12-24—Подача