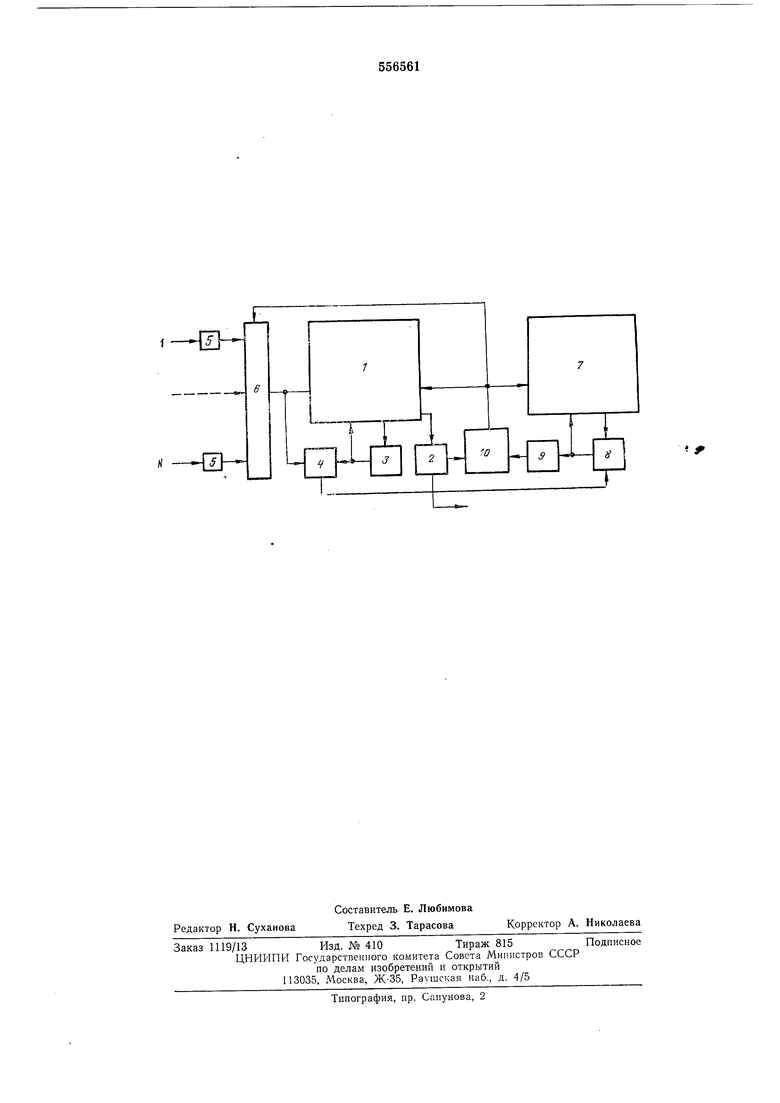

Принимаемые по параллельным каналам связи двоичные знаки посылок через буферные элементы 5 и коммутатор 6 поступают в накопитель 1, где запоминаются в оперативном запоминающем устройстве (ОЗУ). Последовательность подключения N каналов задается блоком 10 управления в зависимости от числа и приоритетности каналов связи, а также скорости передачи информации.

Блок 10 легко реализуется на логических элементах в соответствии с заданным алгоритмом работы.

Для каждого канала связи в соответствующих зонах ОЗУ хранится п двоичных знаков посылки фазового пуска, где п - степень образующего многочлена рекуррентной последовательности (РП), что достаточно для рекуррентной проверки и образования последующих знаков посылки при автономном генерировании знаков. Для рекуррентной проверки из ОЗУ накопителя 1 в блок сумматоров 3 поступают знаки, соответствующие ненулевым коэффициентам образующего многочлена РП. На выходе схемы 4 сравнения появляется сигнал при удовлетворении рекуррентной проверки знака, принимаемого из канала связи. Эти сигналы поступают на сумматор 8, который осуществляет суммирование их в двоичном коде с т-разрядным числом, хранящимся в наколителе 7 и соответствующим результатам предществующих проверок для данного канала.

Разрядность сумматора 8 выбирается из следующего соотнощения:

m log2/(,

где К - пороговое значение серии проверок знаков на соответствие рекуррентному закону.

Дещифратор 9 выдает сигнал в блок 10 управления в том случае, если для данного каиала зиачение т-разрядной суммы превышает пороговое значение, который прекращает цикл опроса анализируемого канала по входу, включает цепь автономной генерации знаков РП: выход накопителя 1 - блок 3, и подключает дешифратор 2.

Выделенный сигнал фазового пуска переводит блок 10 в исходный режим работы данного канала или при необходимости - к переходу к обслуживаиию других дополнительных каналов связи.

Таким образом, сумматор 8 в совокупности с дешифратором 9 и накопителем 7 обеспечивает подсчет рекурреитных проверок для всех Л параллельных каналов, т. е. выполняет функции Л счетчиков серии совпадений. Кроме того, накопитель 1 в совокупности с коммутатором 6 и блоком 10 обеспечивает прием

посылок фазового пуска с соответствующими проверками по всем параллельным каналам, т. е. выполняет функции N регистров сдвига с переключателями режима работы и селекторами фазирующих сигналов. В результате этого существенно уменьшается объем оборудования при сохранении общего числа параллельно включенных каналов связи.

Формула изобретения

Устройство для выделения рекуррентных сигналов фазового пуска в многоканальных системах связи, содержащее накопитель знаков, соединенный с дешифратором пусковых комбинаций и блоком сумматоров по модулю

два, выход которого подключен к схеме сравнения н накопителю знаков, отличающеес я тем, что, с целью повыщения быстродействия, в него введены буферные элементы, коммутатор, накопитель результатов и последовательно соединенные сумматор, дещифратор пороговых значений и блок управлепия, подключенпый к управляющим входам коммутатора, накопителя знаков и накопителя результатов, выход которого соединен с входом сумматора, к второму входу которого подключена схема сравнения, при этом буферные элементы подключены к коммутатору, выход которого соединен с сигнальным входом накопителя знаков и вторым входом схемы сравнения, а дешифратор пусковых комбинаций подключен к блоку управления, причем выход сумматора соединен с входом накопителя результатов. Источник информации, принятый во внимание при экспертизе:

1. Гордой Ф. Г. и Пурмухаммедов Л. X. О фазировании датчиков испытательных тестов.-«Вонросы радиоэлектроники. Сер. XI. Вып. 6, 1965 (нрототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения рекуррентных сигналов фазового пуска в многоканальных системах связи | 1976 |

|

SU605326A1 |

| Устройство для выделения рекуррентныхСигНАлОВ фАзОВОгО пуСКА B МНОгОКАНАльНыХ СиСТЕМАХ СВязи | 1979 |

|

SU849519A2 |

| Устройство фазового пуска рекуррентной последовательности | 1990 |

|

SU1829122A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2254676C2 |

| Приемное устройство рекуррентных кодовых последовательностей | 1982 |

|

SU1054921A1 |

| Устройство фазирования циклов многоканальной системы передачи дискретной информации | 1980 |

|

SU896782A1 |

| Устройство выделения рекуррентного синхросигнала с исправлением ошибок | 1976 |

|

SU582578A1 |

| Устройство для выделения м-последовательности | 1976 |

|

SU568191A1 |

| Устройство для приема рекуррентного сигнала фазового пуска | 1990 |

|

SU1730732A1 |

Авторы

Даты

1977-04-30—Публикация

1974-06-14—Подача