сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство рекуррентного фазового пуска | 1986 |

|

SU1356250A1 |

| Устройство фазового пуска | 1986 |

|

SU1350839A1 |

| Устройство для выделения рекуррентного синхросигнала | 1978 |

|

SU758549A2 |

| Устройство фазового пуска | 1979 |

|

SU866773A1 |

| УСТРОЙСТВО ФАЗОВОГО ПУСКА | 1995 |

|

RU2115248C1 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Анализатор рекуррентного сигнала фазового пуска | 1981 |

|

SU995361A2 |

| Устройство фазового пуска | 1986 |

|

SU1415447A2 |

| Приемное устройство рекуррентных кодовых последовательностей | 1982 |

|

SU1054921A1 |

| Приемник рекуррентных последовательностей | 1985 |

|

SU1256232A1 |

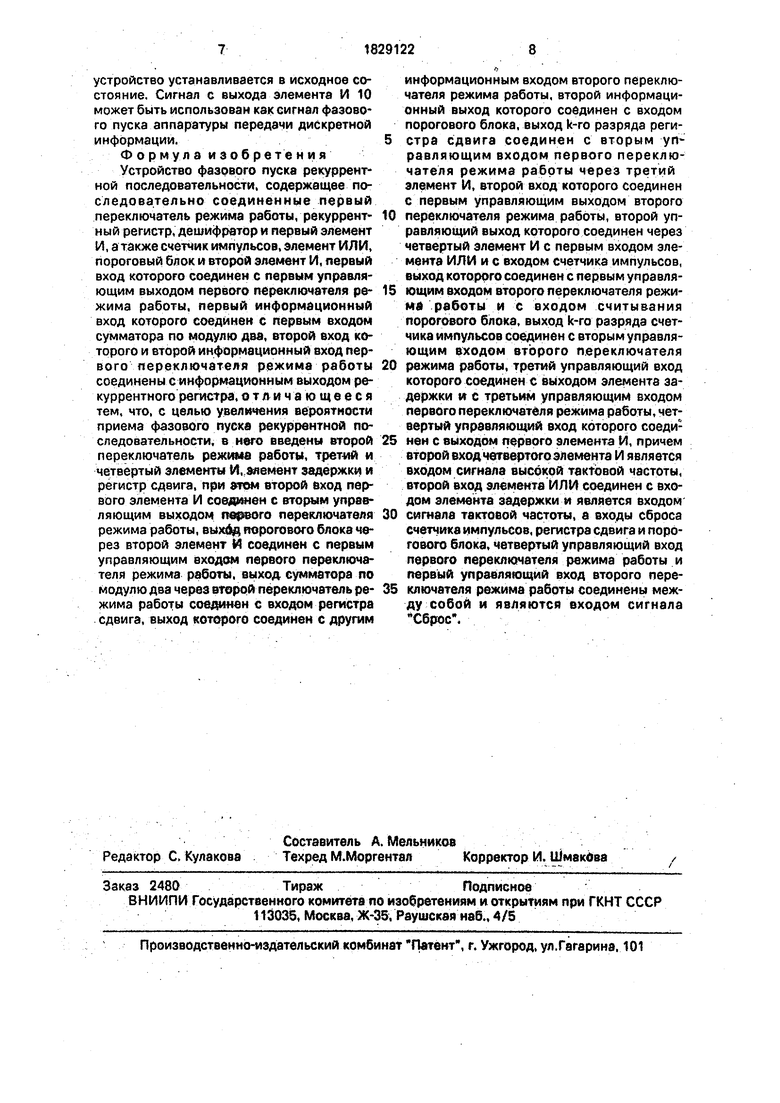

Изобретение относится к технике связи и может быть использовано для увеличения вероятности фазового пуска рекуррентной последовательности. Цель изобретения - увеличение вероятности приема фазового пуска рекуррентной последовательности, Устройство фазового пуска рекуррентной последовательности содержит первый переключатель 1 режимов работы, рекуррентный регистра, сумматор 3 по модулю два, дешифратор 4, второй переключатель 5 режимов работы, регистр сдвига 6. пороговый блок 7. элемент ИЛИ 8, элементы И 9, 10 и 11, счетчик 12 импульсов, элемент И 13 и элемент задержки 14. 1 ил.

00

ю

Ч

ю ю

Изобретение относится к технике связи и может быть использовано для увеличения вероятности фазового пуска рекуррентной последовательности.

Цель изобретения -увеличение вероятности фазового пуска рекуррентной последовательности.

Предлагаемое устройство фазового пуска рекуррентной последовательности имеет существенные признаки, отличающие его от прототипа как по составу элементов - это второй переключатель режима работы, третий и четвертый элементы И, элемент задержки, регистр сдвига, так и по связям между элементами, что обеспечивает положительный эффект, заключающийся в увеличении вероятности фазового пуска рекуррентной последовательности. Введенная совокупность новых признаков позволяет устранить недостатки, присущие известному устройству.

На чертеже изображено устройство фазового пуска рекуррентной последовательности.

Устройство фазового пуска рекуррентной последовательности содержит переключатель 1 режимов работы с двумя информационными входами и информационным выходом, четырьмя управляющими входами и двумя управляющими выходами, рекуррентный регистр сдвига 2 на п разрядов, сумматор 3 по модулю 2, дешифратор 4, переключатель 5 режимов работы с двумя информационными входами и двумя информационными выходами, тремя управляющими входами и двумя управляющими выходами, регистр сдвига 6 на (k+N) разрядов с информационным входом, выходом и выходом с разряда к, входом тактовой (сдви- гающей)частоты, пороговый блок 7, элемент ИЛИ 8, элементы И 9, 10 и 11.,счетчик 12 с объемом счета (k+N) и дополнительным выходом с разряда к, элемент И 13, элемент задержки 14, второй вход элемента ИЛИ 8 является входом тактовой частоты F, второй вход элемента И 13 является входом высокой тактовой частоты т,при этом f (k+N)F, входы Сброса счетчиков импульса, регистра сдвига и порогового элемента и четвертый управляющий вход первого переключателя режима работы и первый управляющий вход второго переключателя режима работы соединены между собой и являются входом сигнала Сброс. В данном устройстве РП считается выделенной (принятой), если на участке длиной N бит, принятых из канала, находится менее m ошибок, после чего следует k неискаженных бит, при этом обратная связь приемного рекуррентного регистра 2 замыкается на

безыскаженном участке. Проверка наличия в принимаемой последовательности указанных критериев осуществляется с приемом каждого бита, для чего производится

накопление на регистре сдвига 6 сигналов сравнения с сумматора 3 обьемом (k+N) бит и анализ на наличие в них обоих критериев. Анализ проводится с высокой частотой f (k+N), что и позволяет провести его за

такт частоты F.

Предлагаемое устройство работает следующим образом:

Перед началом работы сигналом по цепи Сброс элементы устройства устанавливаются в исходное состояние, при этом

-разрешается прохождение информационных сигналов, поступающих на первый информационный вход переключателя 1,че- рез его информационный выход на вход регистра 2;

-с второго управляющего выхода переключателя 1 на второй вход элемента И 10 подается запрещающий сигнал;

-пороговый блок 7 и счетчик 12 устанав- ли ваются в нулевое состояние;

-элементы регистра сдвига 6 устанавливаются в состояние

-на первом управляющем входе переключателя 5 устанавливается сигнал, разрешающий прохождение сигналов с выхода сумматора 3 на вход регистра 6.

Двоичные знаки рекуррентной последовательности, принимаемые из канала связи с частотой Р,через переключатель 1 поступают на вход рекуррентного регистра сдвига 2, обратная связь которого при этом разомкнута. Получаемая на выходе регистра 2 последовательность сравнивается сумматором 3 с входной последовательностью. При

этом, если знаки рекуррентной последовательности, поступающие из канала связи не искажены, то с выхода сумматора 3 будет поступать последовательность нулей. При помехах в канале связи с выхода сумматора

3 наряду с нулями (признаками сравнения) будут поступать и единицы (сигналы несравнения). Эта последовательность сигналов сравнения и сигналов несравнения с каждым битом информации, приходящей

из канала связи, через переключатель 5 поступает на вход регистра сдвига б, который через (k+N) тактов будет ими заполнен.

После каждой записи в регистр сдвига б сигнала с сумматора 3 содержимое регистра

б анализируется на соответствие критериям выделения РП. Для этого определяется наличие или отсутствие ошибок в первых k знаках регистра сдвига 6 и производится подсчет числа знаков несравнения, нахо- дящихся во всем регистре сдвига б (фактмчески в последних N его знаках). Отсутствие ошибок в первых k знаках регистра 6 говорит о заполнении в данный момент рекуррентного регистра 2 безыскаженными знаками РП, а наличие в регистре 6 числа ошибок менее m о том, что из канала действительно поступает РП.

Указанная проверки производятся следующим образом.

С приходом на второй вход элемента ИЛ И. 8 импульса тактовой частоты F на выходе элемента ИЛИ 8 появляется сигнал, который поступает на тактовый вход регистра 6, в первый разряд регистра 6 производится запись сигнала с выхода сумматора 3 и сдвиг содержимого регистра 6 на один разряд. Одновременно сигнал частоты F поступает на вход элемента задержки 14. Пройдя элемент задержки 14 сигнал с его выхода поступает на третий управляющий вход переключателя 5 и на третий управляющий вход переключателя 1, при этом замыкается обратная связь регистра 6, с первого управляющего выхода переключателя 1 на второй вход элемента И 9 поступает разрешающий сигнал, с первого управляющего выхода переключателя 5 на первый вход элемента 11 поступает разрешающий сигнал, с второго управляющего выхода переключателя 5 на второй вход элемента И 13 поступает разрешающий сигнал, при этом через элемент И 13 высокая частота f поступает на вход счетчика 12, а через элемент ИЛИ 8 она поступает на тактовый (сдвигающий) вход регистра 6, Счетчик 12 начинает вести подсчет поступающих на его вход импульсов, а содержимое регистра 6 начинает сдвигаться, при этом сигналы с его выхода через переключатель 5 поступают на его вход и на вход порогового блока 7.

Если в первых k разрядах регистра 6 были знаки несравнения (ошибки), то они через открытый элемент И 11 поступят на второй управляющий вход первого переключателя, при этом с первого управляющего выхода переключателя 1 на первый вход элемента И 9 прекращается поступление разрешающего сигнала, что будет свидетельствовать о наличии ошибок в первых k знаках регистра 6 и знаках,заполняющих регистр 2, т.е. первый критерий приема РП не выполняется. Если же в первых k знаках регистра 6 не будет сигналов несравнения, то на второй управляющий вход первого переключателя сигналы ошибок не поступают и на первый вход элемента И 9 с первого управляющего выхода переключателя 1 будет продолжать поступать разрешающий сигнал.

Через k тактов работы устройства на выходе k счетчика 12 появляется сигнал, который поступает на второй управляющий вход переключателя 5, при этом с первого 5 управляющего выхода переключателя 5 снимается разрешающий сигнал, который поступал на первый вход элемента И 11 и последующие после k тактов знаки несравнения с регистра б через элемент И 11 не

0 будут поступать на второй управляющий вход переключателя 1, что обеспечит исключение влияния на разрешающий сигнал с первого управляющего выхода переключа- -теля 1 знаков,находящихся между разрядом

5 k и концом регистра 6{обьем N знаков).

Знаки несравнения, продвигаясь по регистру поступают на второй информационный вход переключателя бис второго информационного выхода переключателя 5

0 поступают на вход регистра 6 и на вход порогового блока 7, который производит их подсчет. Через (k+N) тактов работы устройства на выходе счетчика 12 появляется сигнал, который поступает на первый

5 управляющий вход переключателя 5, обратная связь регистра б размыкается, при этом его состояние будет таким же, как до замыкания обратной связи (записи в него последнего знака с сумматора 3). Сигналом со

0 счетчика 12 опрашивается также состояние порогового блока 7. Если в регистре 6 число несравнений было больше заданного гл, то по истечении (k+N) тактов на выходе порогового блока 7 сигнала не будет, и с приходом

5 очередного импульса частоты F в регистр б запишется очередной сигнал с сумматора 3 и снова будет производиться анализ содержимого регистра 6. Если же число несравнений будет меньше либо равно гп, то на

0 выходе порогового блока 7 появится сигнал, который поступает на второй вход элемента И 9. Если на первый вход элемента И 9 с первого управляющего выхода переключателя 1 поступает разрешающий сигнал (т.е.

5 в первых k разрядах регистра б нет сигналов несравнения - регистр 2 заполнен неискаженными знаками), то на выходе элемента И 9 появляется сигнал, который поступает на первый управляющий вход переключате0 ля этом через второй информационный вход и информационный выход переключателя 1 замыкается обратная связь рекуррентного регистра 2 и регистр переходит в режим автономной работы.

5 формируя знаки РП, синхронные со знаками, приходящими из канала связи.

При появлении на нем контрольной : комбинации на входе дешифратора 4 появляется сигнал, который через открытый элемент И 10 поступает на его выход и

устройство устанавливается в исходное состояние. Сигнал с выхода элемента И 10 может быть использован как сигнал фазового пуска аппаратуры передачи дискретной информации.

Фор мула изобретения Устройство фазового пуска рекуррентной последовательности, содержащее последовательно соединенные первый переключатель режима работы, рекуррентный регистр, дешифратор и первый элемент И, а также счетчик импульсов, элемент ИЛИ, пороговый блок и второй элемент И, первый вход которого соединен с первым управляющим выходом первого переключателя режима работы, первый информационный вход которого соединен с первым входом сумматора по модулю два, второй вход которого и второй информационный вход первого переключателя режима работы соединены с информационным выходом рекуррентного регистра, отличающееся тем, что, с целью увеличения вероятности приема фазового пуска рекуррентной последовательности, в него введены второй переключатель режиме работы, третий и четвертый элементы И, элемент задержки и регистр сдвига, при атом второй вход первого элемента И соединен с вторым управляющим выходом первого переключателя режима работы, выход порогового блока через второй элемент И соединен с первым управляющим входом первого переключателя режима работы, выход сумматора по модулю два через второй переключатель режима работы соединен с входом регистра сдвига, выход которого соединен с другим

информационным входом второго переключателя режима работы, второй информационный выход которого соединен с входом порогового блока, выход k-ro разряда регистра сдвига соединен с вторым управляющим входом первого переключателя режима работы через третий элемент И, второй вход которого соединен с первым управляющим выходом второго

переключателя режима работы, второй управляющий выход которого соединен через четвертый элемент И с первым входом элемента ИЛИ и с входом счетчика импульсов, выход которого соединен с первым управляющим входом второго переключателя режима работы и с входом считывания порогового блока, выход k-ro разряда счетчика импульсов соединен с вторым управляющим входом второго переключателя

режима работы, третий управляющий вход которого соединен с выходом элемента задержки и с третьим управляющим входом первого переключателя режима работы, четвертый управляющий вход которого соединен с выходом первого элемента И, причем второй вход четвертого элемента И является входом сигнала высокой тактовой частоты, второй вход элемента ИЛИ соединен с входом элемента задержки и является входом

сигнала тактовой частоты, а входы сброса счетчика импульсов, регистра сдвига и порогового блока, четвертый управляющий вход первого переключателя режима работы и первый управляющий вход второго переключателя режима работы соединены между собой и являются входом сигнала Сброс,

| Устройство фазового пуска | 1979 |

|

SU866773A1 |

Авторы

Даты

1993-07-23—Публикация

1990-10-03—Подача