(54) УСТРОЙСТВО ФАЗИРОВАНИЯ ЦИКЛОВ

ШОГОКАНАЛЬНОЙ -СИСТЕМЫ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ

1

Изобретение относится к электро- связи и может быть использовано для цикловой синхронизации многоканальной системы при временном уплотнении дискретизированного телефонного или группового канала связи.

Известно устройство фазирования циклов многоканальной системы передачи дискретной информации с временным разделением каналов, содержащее на приеме объединенные по входу сумматор по модулю два и блок, поиска, фазирующей последовательности, выход которого через датчик фазирующей последовательности подключен к второму входу сумматора по модулю два, выход которого подключен ко входу pacпpeдeлитeляj к управляющему входу которого через счетчик циклов подключен выход дешифратора 1.

Однако известное устройство имеет сравнительно большое время фазирования.

Цель изобретения - сокращение зремени фазирования

Указанная цель достигается тем, что в-.устройство фазирования циклов, многоканальной системы передачи дискретной информации с временным разделением каналов, содержащее на приеме объединенные по входу сумматор по модулю два и блок поиска фазирукнцей последовательности, выход

to которого через датчик фазирующей последовательности подкшзчен к второму входу сумматора по модулю два, выход которого подключен ко входу распределителя, к управлякмцему входу

IS которого через счетчик циклов подключен выход дешифратора, введены на приеме датчик синхронизирукзщей последовательности, кодопреобразователь, анализатор, а также последовательно

20 соединенные коммутатор, блок поиска синхронизирующей последовательности и блок управления, к второму и третьему входам которого подключейы Соответственно выход анализатора и второй ьыход блока поиска фазирующей последовательности, к второму входу которого непосредственно и через кодопреобразователь к второму входу датчика фазирукадей последовательности подключен первый выход блока управления, второй выход которого подключен к одному из входов коммутатора и второму входу блок поиска синхронизирующей последовательности, второй выход которого подключен к второму входу кодопреобразователя и входу датчика синхронизирующей последовательности, выходы которого подключены ко входам дешифратора, при этом выходы распределителя подключены ко входам коммутатора, второй выход которого через анализатор подключен к второму входу счетчика циклов.

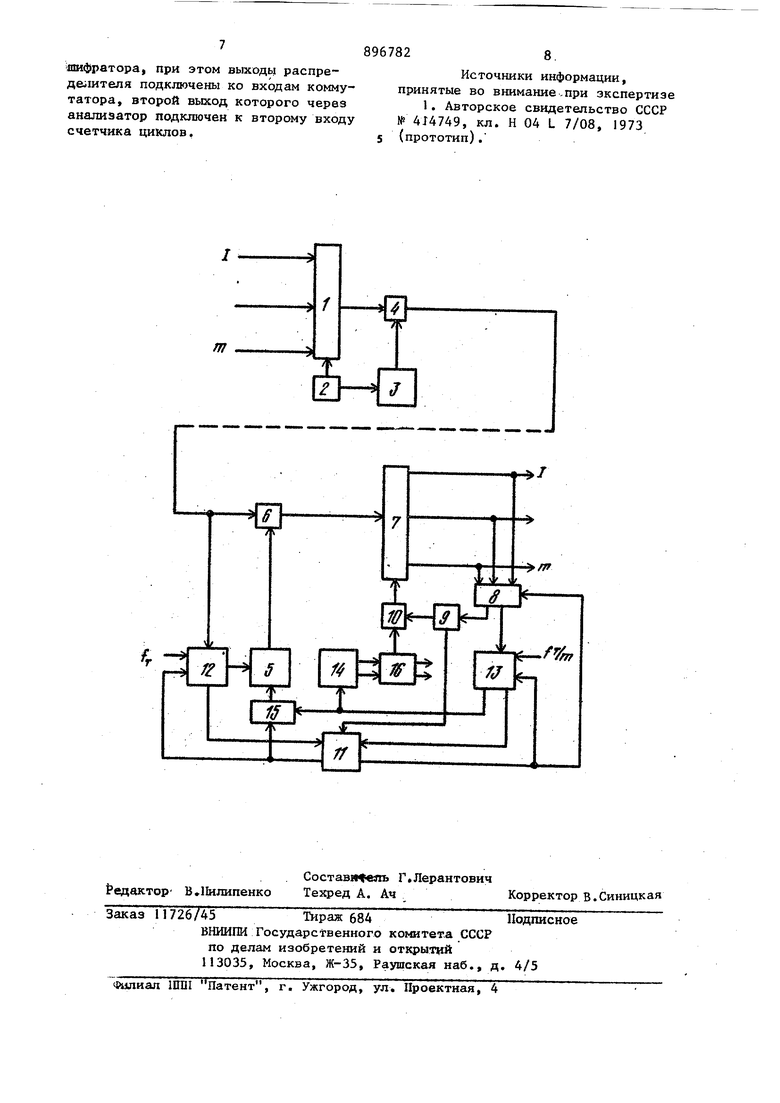

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство содержит на передаче распределитель 1, счетчик 2 циклов, датчик 3 фазирующей последовательности (ФП) и сумматор 4 по модулю два, а на приеме датчик 5 фазирующей последовательности, сумматор 6 по модулю два, распределитель 7, коммутатор 8, анализатор 9, счетчик 10 циклов, блок И управления, блок 12 поиска фазирующей последовательности , блок 13 поиска синхронизирунмцей последовательности (СП) , датчик 14 синхронизирующей последовательности кодопреобразователь 15 и дешифратор 16.

Устройство работает следующим образом.

На передающем конце линии связи распределитель 1, управляемый счетчиком 2 циклов, поочередно подключает информационные каналы,I-т к . общему каналу связи, причем один из каналов, например т-ый используется в качестве канала синхронизации.

Датчик 3 фазирующей последователности вырабатывает непрерывно рекуррентную последовательность максимального периода 2 -1 дв. знаков, описываемую многочленом

риИ-а х - а... .0.,

которая складывается.в сумматоре 4 по модулю два со знаками, поступаюгщми с выхода распределителя 1.

Таким образом в канал связи будет передаваться случайная равновероятная последовательность двоичных знаков независимо от статистической

структуры йоследовательностей в информационных каналах. В результате этого повьпиается устойчивость работы приемного устройствасинхронизации тактовых частот, что обеспечивает более высокую стабильность в работе и приемного устройства цикловой синхронизации.

При этом в канале синхронизации будет следовать каждый т-ьй знак

исходной Ф11, образуя рекуррентную СП описывае1 ю многочлелом

bxf,

.,

который однозначно определяется многочленом Р( X ).,

В частном случае, когда , гдеt l,2,3...(l(x)P(x).

На приемном конце линии связи знаки, вырабатываемые датчиком 5 ФП, исключаются с помощью сумматора b по

модулю два из принимаемой последовательности знаков, после чего производится ее раскоммутация распределителем 7 по информационным каналам и каналу синхронизации.

При наличии синхронизма в работе приемного устройства на вход анализатора 9, подключенного через коммутатор 8 к каналу синхронизации,будет поступать нулевая последовательность (при отсутствии ошибок в канале связи).

В том случае, когда происходит сбой цикловой фазы датчика 5 ФИ

и распределителя 7, управляемого счетчиком 10 циклов, на входе анализатора 9 будет иметь место случайная равновероятностная последовательность единиц и нулей. Тогда блок 11 управления включает блок 12 поиска фазирующей последовательности для выделения й-значных комбинаций и синхронизации датчика 5 ФП, а также блок 13 поиска СИ для выделения СП по каналам и фазирования датчика 14 СП.

Указанные последовательности.могут быть выявлены на основе рекуррентных проверок в соответствии с многочленами Р(х) и (l(x).

Ввиду того , что в информационных каналах комбинации.передаваемых сообщений могут -периодически чередоваться с комбина1шями отсутстпия информации (из-за режима асинхронного сопряжения информационных каналов) то в предлагаемом устройстве нет необходимости через каждые К циклов прерывать передачу информаили для передачи комбинаций фазирования. Введение датчиков 5 ФП и 14 СП в синхронизм может быть осуществлено автоматически и по информационным каналам, где отсутствует передача информации в течение времени, равном или превышающем дв, знаков (где 2 - длина селектируемого отрезка ФГ1 или СП) , что в конечном счете сокращает время фазирования. Выделение в блоке 13 поиска СП серии знаков без ошибок (S - число проверок на соответствие рекуррентному закону образования СП) достаточно для фазирования датчика 14 СИ, причем.селектируемые И знаков СП могут быть преобразованы кодопреобразователем 15 в соответ ствующие знаки ФП и для фазирования датчика 5 ФП, если он не успел засинхронизироваться от блока 12 поиска ФП. В частном случае, когда происходит рассинхронизация, например, тол ко датчика 5 ФП, на входе анализатора 9 будет присутствовать рекуррент ная последовательность (с,к. сложени по модулю два двух несфазированных рекуррентных последовательностей образуют ту же Сс.мую рекуррентную последовательность), но с отлич ным фазовым сдвигом, выделение которой блоком 13 поиска СИ будет про изведено без осуществления операции поиска по каналам, что повышает быстродействие фазирования дятчикя 5 5 ФП через кодопреобразователь 15. При рассинхронизации только рас пределителей достаточно с помощью анализатора 9 определить канал син ронизации, где следует нулевая посл довательность, чтобы сфазировать счетчик 10 циклов. Кроме того, счет 10 циклов может быть засинхронизирован и от датчика 14 СП при вьщел нии на дешифраторе 16 п-значных комбинаций соответствующих началу цикла. Таким образом,.в предлагаемом у ройстве фазирования циклов многоканальной системы передачи дискрет 24 информации с временным разделавшем каналов, синхронизация может быть восстановлена после сбоя на любом отрезке принимаемой информационной. последовательности, причем с разграничением случаев рассинхронизации датчиков или распределителей. При этом при отсутствии передаваемой информации на одном или несколь ких информационных каналах, позволяет устройству автоматически с повышенным быстродействием обеспечить захват цикловой фазы, в результате этого существенно сокращается время фазирования. Формула изобретения Устройство фазирования цик;1Ов многоканальной системы передачи дискретной информации с временньм разделе- нием каналов, содержащее на приеме объединенные по входу сумматор по модулю два и блок поиска фазирующей последовательности, выход которого через датчик фазирующей последовательности подключен к второму входу сумматора по модулю два, выход которого подключен ко входу распределителя, к управляющему входу которого через счетчик циклов подключен выход дешифратора, отличающееся тем, что, с целью сокращения времени фазирования, введень на приеме датчик синхронизирующей последовательности, кодопреобразователь, анализатор, а также последовательно соединенные коммутатор, блок .поиска синхронизирующей последовательности и блок управления, к второму и третьему входам которого подключены соответственно выход анализатора и второй выход блока поиска фазирующей последовательности, к второму входу которого непосредственно и через кодопреобразователь к второму входу датчика фазирующей.последовательности подключен первый выход блока управления, второй выход которого подключен .К одному из входов коммутатора и второму входу блока поиска ,1 синхронизирующей . последовательности, второй выход которого подключен к второму входу кодопреоо разователя и входу датчика синхронизирующей последовательности, выходы которого подключены ко входам дешифратора, при этом выходц распределителя подключены ко входам коммутатора, второй выход которого через анализатор подключен к второму входу счетчика циклов. 8967828. Источники информации, принятые во внимание-при экспертизе 1. Авторское свидетельство СССР 4М749, кл. Н 04 L 7/08, 1973 5 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи ипРиЕМА диСКРЕТНОй иНфОРМАциипО пАРАллЕльНыМ КАНАлАМ СВязипЕРЕМЕННОй длиНы | 1978 |

|

SU794753A1 |

| Устройство циклового фазирования | 1978 |

|

SU725258A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для выделения рекуррентных сигналов фазового пуска в многоканальных системах связи | 1974 |

|

SU556561A1 |

| Устройство для выделения рекуррентныхСигНАлОВ фАзОВОгО пуСКА B МНОгОКАНАльНыХ СиСТЕМАХ СВязи | 1979 |

|

SU849519A2 |

| Устройство для синхронизации @ -последовательности с инверсной модуляцией | 1983 |

|

SU1156264A1 |

| Устройство для передачи и приема дискретной информации по параллельным каналам связи переменной длины | 1989 |

|

SU1658407A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

fr

Авторы

Даты

1982-01-07—Публикация

1980-04-07—Подача