(54) УСТРОЙСТВО ДЛЯ КВАНТОВАНИЯ СЛУЧАЙНОГО. ПРОЦЕССА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для квантования случайных процессов | 1982 |

|

SU1084812A1 |

| Устройство для квантования случайного процесса | 1974 |

|

SU516188A1 |

| Устройство аналого-цифрового преобразования | 1980 |

|

SU949806A1 |

| Адаптивный временных дискретизатор | 1974 |

|

SU660239A1 |

| Устройство для имитации цифрового сигнала ошибки следящего привода | 1987 |

|

SU1472870A1 |

| Устройство для сжатия информации | 1980 |

|

SU930333A1 |

| Устройство для аналого-цифрового преобразования | 1982 |

|

SU1027813A2 |

| Устройство для определения экстре-МАльНыХ зНАчЕНий СлучАйНыХпРОцЕССОВ | 1978 |

|

SU805358A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1978 |

|

SU738151A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056250A2 |

1

Изобретение относится к области вычислительной техники и может найти применение при анализе случайных процессов.

Известно .устройство для квантования случайного процесса, содержащее блок уп- равления, аналого-цнфровой преобразователь блок сравнения, распределитель, .счетчики, дешифратор, блок усреднения, логические элементы l. Недостатком этого устройства является его сложность.

Наиболее близким техническим решением к данному изобретению является устройство для квантования случайного процесса, содержащее блок управления, блок вычитания, первый и второй входы которого соединены соответственно с выходами первого и второго аналоговых фиксаторов, первые входы которых являются входом устройства и соединены с первым входом аналого-цифрово- го преобразователя, выход которого является выходом устройства 2,

Недостатком этого устройства является низкая точность квантования случайного процесса.

Целью изобретения является повышение точности.

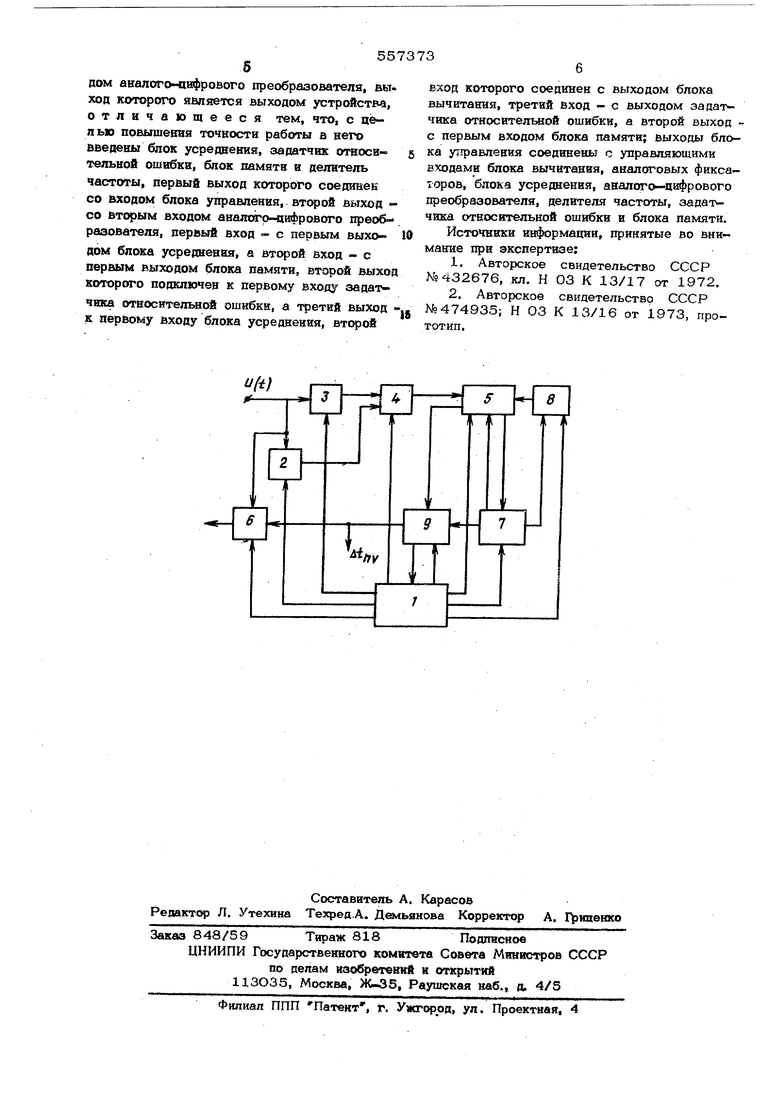

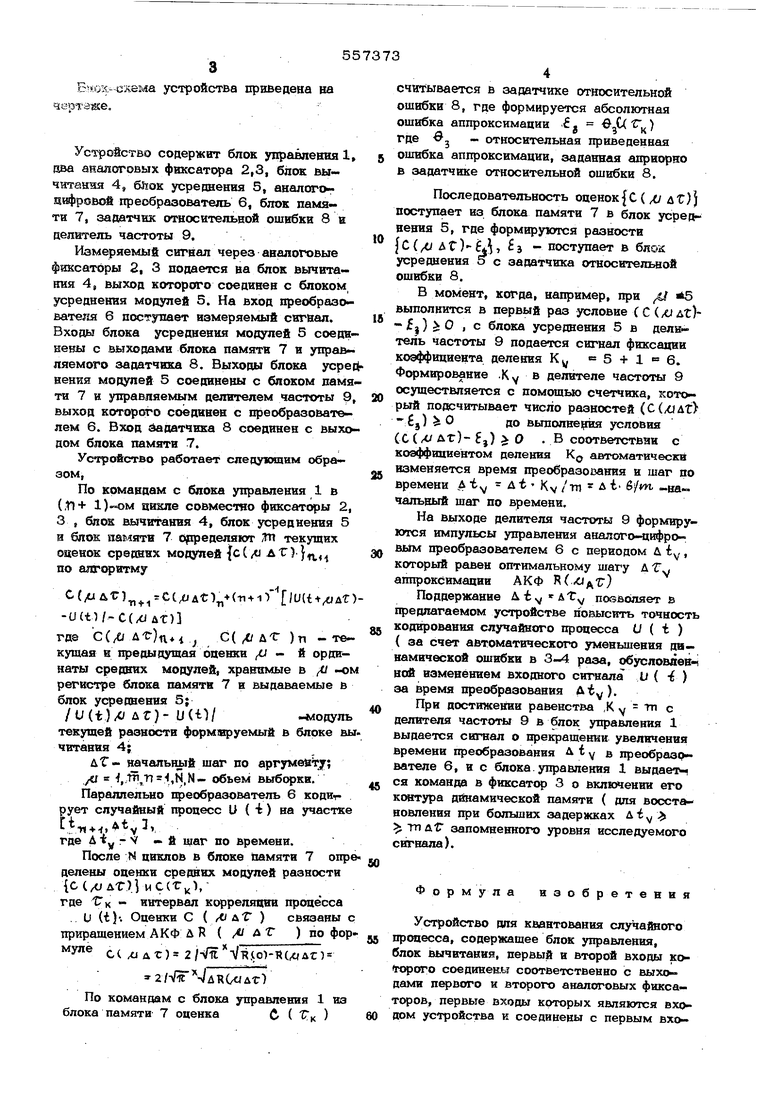

Для достижения этой цели в предложенное устройство введены блок усреднения, задатчик относительной ощибки, блок памяти и делитель частоты, первый выход которого соединен с6 входом блока управления, второй выход - со вторым входом аналогоцифрового преобразователя, первый вход - с первым выходом блока усреднения, а второй вход - с первым выходом блока памяти, второй выход которого подключен к первому входу задатчика относительной ошибки, а третий выход - к первому входу блока усреднения, второй вход которого соединен с выходом блока вычитания, третий вход с выходом задатчика относительной ошибки, а второй выход - с первым входом блока памяти. Выходы блока управления соединены с управляющими входами блока вычитания, аналогоБьк фиксаторов, блока усреднения, аналого-цифрового преобразователя, делителя частоты, задатчика относительной ошибки и блока памяти. Brsox-cxeMa устройства приведена на чертзже, ; Устройство содержит блок управления 1, два аналоговых фиксатора 2,3, блок вычитания 4, бйок усрепвения 5, аналогог цифровой преобразователь 6, блок памяти 7, задатчшс относительной ошибки 8 и делатель частоты 9. Измеряемый сигнал через аналоговые фшссаторы 2, 3 подается на блок вычитания 4, выход которого соединен с блоком, усреднения модулей 5. На вход преобразователя 6 поступает измеряемый сигнал. Входы блока усреднения модулей 5 соединены с выходами блока памяти 7 и управляемого за датчика 8. Выходы блока ycpe нения модулей 5 соединены с блоком памя ти 7 и управляемым делителем частоты 9 выход которого соединен с преобразователем 6. Вход дадатчика 8 соединен с выхо дом блока памяти 7. Устройство работает следу1сипим образом, По командам с блока управления 1 в (,П+ 1)-ом аикле совместно фиксаторы 2, 3 , блок вычитания 4, блок усреднения 5 и блок памяти 7 определяют /тп текущих оценок срернях модулей |c( л) }n,«i по алгоритму C(/U&tr) )+(TI-(-l) |U{t+ At -uctH-C(ut)3 где С(/0 utr) С(ДС- )п -текущая и предыдущая опенки - и ординаты средних модулей, хранимые в -о регистре блока памяти 7 и выдаваемые в блок усреднения 5; /U(t)/0 ДГ}- UC-fcl/-модуль текущей разности формируемый в блоке в читания 4; дГ- начальный шаг по аргумегйт/; ,, объем выбелки. Параллельно преобразователь 6 кодитрует случайный процесс LJ ( i) на участке А iy - V шаг по времени. После N циклов в блоке памяти 7 опр делены оценки средних модулей разности {С(лДГ)ЛиС(Т),где fк - интервал корреляции процеЪса и (t)-. Оценки С (уСдГ ) связаны приращением АКФ и R ( Д Т ) по фо С( J д-с) 2/TrflN-R.(o)-RUAC) ) По командам с блока управления блока памяти 7 оценкаС ( Тк считывается в задатчике относительной ошибки 8, где формируется абсолютная ошибка аппроксимации f g tTj) где 5 - относительная приведенная ошибка аппроксимации, заданная априорно в задатчике относительной ошибки 8. Последовательность оценок{С ( х/ д Т)j поступает из блока памяти 7 в блок усреднения 5, где формируются разности {с ( ДС) 6i, f 3 - поступает в блок усреднения о с задатчика относительной ошибки 8. В момент, когда, например, при д/ 5 выполнится в первый раз условие С С (л At) J) i О , с блока усреднения 5 в делитель частоты 9 подается сигнал фиксации коэффициента деления Ку, «бч-Х б. Формирование .К у в делителе частоты 9 осуществляется с помощью счетчика, который подсчитывает число разностей (С(лдГ б, выполнения условия (С (4J дт)- f j) 0 .В соответствии с коэффициентом деления К, автоматически изменяется время преобразования и шаг по времени Д ty Д t KV /тп - Д 6/ -начальный шаг по времени. На выходе делителя частоты 9 формируются импульсы управления аналого-цифровым преобразователем 6 с периодом и ty, который равен оптимальному шагу ДГ аппроксимации АКФ К(С1дТ) Поддержание At. ДТ поеволяет в предлагаемом устройстве повысить точность кодирования случайного процесса U ( t ) ( за счет автоматического уменьшения динамической ошибки в 3-4 раза, обусловяен-i ной изменением входного сигнала U ( -i ) за время преобразования ). При достижении равенства ,К у i с делителя частоты 9 в блок управления 1 выдается сигнал о прекращении увеличения времени преобразования Д t у в преобразо вателе 6, и с блока. управления 1 выдаетн ся команда в фиксатор 3 о включении его контура динамической памяти ( для восстановления при больших задержках Д i у тп д-Г запомненного уровня исследуемого се1гнала). Формула изобретения Устройство для квантования случайного процесса, содержащее блок управления, блок вычитания, первый и второй входы кокфого соединев.ь соответственно с выходами первого и второго аналоговых фиксаторов, первые входы которых являются входом устройства к соединены с первым входом аналогочанфрового преобразователя, ашход которого является выходом устройства, отличающееся тем, что, с цёпыо повышения точности работы в него введены блок усреднения, задатчик относительной ошибки, блок памяти и делитель частоты, первый выход которого соединен со входом блока управления, второй выход - со вторым входом аналого-цифрового преобразователя, первый вход - с первым выхо дом блока усреднения, а второй вход - с первым выходом блока памяти, второй выхо которого подключен к первому входу задатчика относительной ошибки, а третий выход к первому входу блока усреднения, второй вход которого соединен с выходом блока вычитания, третий вход - с выходом за датчика относительной ошибки, а второй выход с первым входом блока памяти; выходы блока управления соедннены о управляющими входами блока вычитания, аналоговых фиксаторов, блока усреднения, аналого-цифрового преобразователя, делителя частоты, задатчика относительной ошибки и блока памяти. Источники информации, принятые во внимание при экспертизе; 1.Авторское свидетельство СССР 432676, кл. Н 03 К 13/17 от 1972. 2.Авторское свидетельство СССР №474935; Н 03 К 13/16 от 1973, прототип.

Авторы

Даты

1977-05-05—Публикация

1975-06-25—Подача