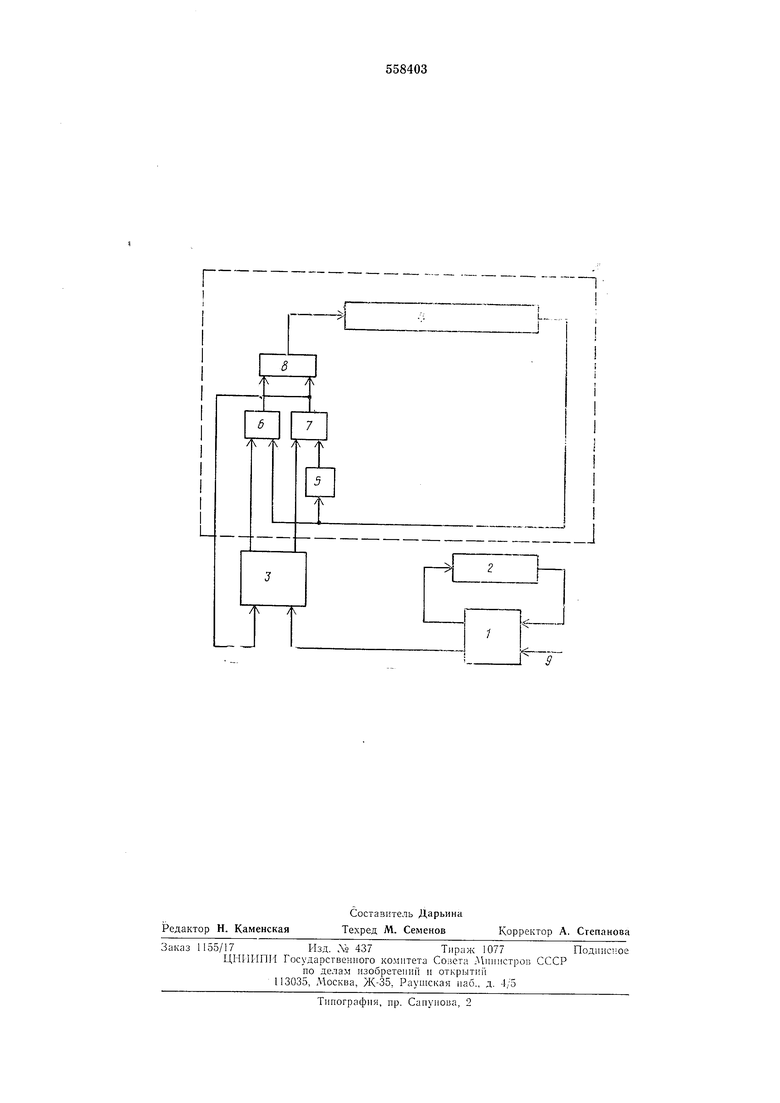

no цепи: полусумматор 1 - динамический регистр 2, код старших разрядов - по цепи: элемент б И - элемент 8 ИЛИ - динамический регистр 4.

При исступлении импульсов счета на вход 9 и переполнении динамического регистра 2, на выходе цепи переноса сумматора появляется сигнал переполнения, переводящий триггер 3 в единичное состояние, приводящее к появлению разрешающего потенциала на первом входе элемента 7. Инвертированный код с динамического регистра 4 поступает на второй вход элемента 7 и сигнал с первого же поступившего разряда (младшего) проходит через элементы 7 и 8, записывая «1 на место младшего разряда динамического регистра 4. Сигнал с выхода элемента 7 устанавливает также триггер 3 в исходное состояние, в результате чего сигналы всех остальных разрядов динамического регистра 4 переписываются в него без изменения через элемент 6. Один цикл циркуляции кода в динамическом регистре 4 осуществляется за время, равное времени заполнения счетчика на динамическом регистре 2 и полусумматоре 1.

Второй сигнал переполнения вновь установит триггер 3 в единичное состояние. При этом проипвертированный код с выхода регистра 4 запишет единицу на место второго разряда регистра 4 и установит триггер 3 в исходное нулевое состояние.

Дальнейшая работа двоичного счетчика осуществляется аналогичным образом.

По окончании счета в динамическом регистре 2 циркулируют младшие разряды, в динамическом регистре 4 - старшие разряды выходного кода.

Формула изобретения

Двоичный счетчик, содержащий полусумматор, выход которого соединен со входом динамического регистра младших разрядов, выход которого подключен к одному входу полусумматора, а второй вход полусумматора является входом двоичного счетчика, первый и второй элементы И, соединенные через элемент ИЛИ со входом динамического регистра старших разрядов, соединенного выходом с

первым входом первого элемента И, отличающийся тем, что, с целью упрощения устройства, в него введен триггер, нодключенный шиной установки в нулевое состояние к выходу второго элемента И, шиной установки

в единичное состояние - к выходу переноса полусумматора, нулевым выходом - ко второму входу первого элемента И, единичным выходом - к первому входу второго элемента И, второй вход которого соединен через инвертор

с выходом динамического регистра старших разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования ветви графа | 1986 |

|

SU1348847A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для нормализации кодов Фибоначчи | 1980 |

|

SU951291A1 |

| Счетчик последовательности импульсов | 1974 |

|

SU538492A1 |

| Накапливающий сумматор | 1990 |

|

SU1829031A1 |

| Счетчик импульсов | 1979 |

|

SU790346A1 |

| Устройство для преобразования двоичных кодов приращения функции | 1975 |

|

SU550657A1 |

| МАСШТАБИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360661A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

Авторы

Даты

1977-05-15—Публикация

1973-10-26—Подача