(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор последовательности импульсов | 1984 |

|

SU1309275A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Счетное устройство | 1979 |

|

SU856011A1 |

| Устройство для обучения основам вычислительнй техники | 1981 |

|

SU1005156A1 |

| Устройство для магнитной записи сигналов времени | 1983 |

|

SU1111200A1 |

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1385327A1 |

| Амплитудный анализатор | 1988 |

|

SU1737273A1 |

| МНОГОУРОВНЕВЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛИТЕЛЬНОСТИ ВЫБРОСОВ И ПРОВАЛОВ НАПРЯЖЕНИЯ | 1991 |

|

RU2054195C1 |

| Генератор серии задержанных импульсов | 1985 |

|

SU1372598A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

Изобретение относится к цнфровой технике и может быть применено в аппаратуре,, .обработки цифровой информации, в измерительной аппаратуре, в частности в элект-: ройных нзмерителях времени.

Известно пересчетное устройство, сод вржащее основной регистр с дешифратором на входе и дополнительный регистр с шифратором на входе, выходы, которого соединены со входами дешифратора, а входы шифратора соединены с выходами основного регистра 1..

Недостаток устройства - структурная сложность.

Наиболее близким по технической сущности к нзрбретению является пересчетное устройство, содержащее регистр с дешифратором , иа входе, выходы которого соединены с дополнительным регистром с шифратором на входе (2..

Недостатки устройства - структурная «ёложность и большое колнчество оборудо-. вания, необходимое для дешифрации, хранения шифрации информации о переносах,

Цель изобретения - повышение надежности работы устройства.

С этой целью в делитель частоты следования импульсов, содержащий регистр с дешифратором на входе, введены счетчик адреса, счетчик числа, блок совпадения и анализатор переполненнй, импульсный выход которого соединен со счетным входом счетчика числа, а потенциальный выход - с потенциальным входом блока совпадения, синхронизирующий вход которого соединен с синхронизнрующим, входом анализатора переполненнй с входом записи счетчика чнсла и с выходом младшего разряда счетчика

10 адреса, а стробирующий вход - с установочным входом анализатора переполненнй Н выходом переполнения счетчнка адреса, разрядные выходы которого соединены с соответствующими адресными входами ре,с гисгра с дешифратором на входе, информационные входы Н выходы которого соединены соответственно с информацноннымн выходами и входами счетчика числа, выход переполнения которого соедннен с входом управления анализатора переполненнй, строби20 рующнй вход которого подключен к счетному

входу счетчнка адреса и к входной, щине.

при этом анализатор переполнений содержнт

. регистр сдвига и элемент И, прнчем стробирующий вход анализатора переполнений соединен с первым входом элемента И, синхронизирующий вход - с вторым входом элемента И и синхронизирующим входом регистра сдвига, установочный вход - с обнуляющим входом второго разряда регистра сдвига, нулевой выход которого подключен к его единичному входу и третьему входу элемента И, вход управления - с информационным входом первого разряда регистра сдвига, а импульсный и потенциальный выходы - соответственно с выходом элемента И и с единичным выходом второгр разряда регистра сдвига, а блок совпадения содержит триггер и элемент ИЛИ, первый вход которого является стробирующим входом блока совпадения, а второй вход соединен Ч; выходом триггера, первый и второй входы которого являются соответственно потенциальным и синхронизирующим входами блока совпадения.

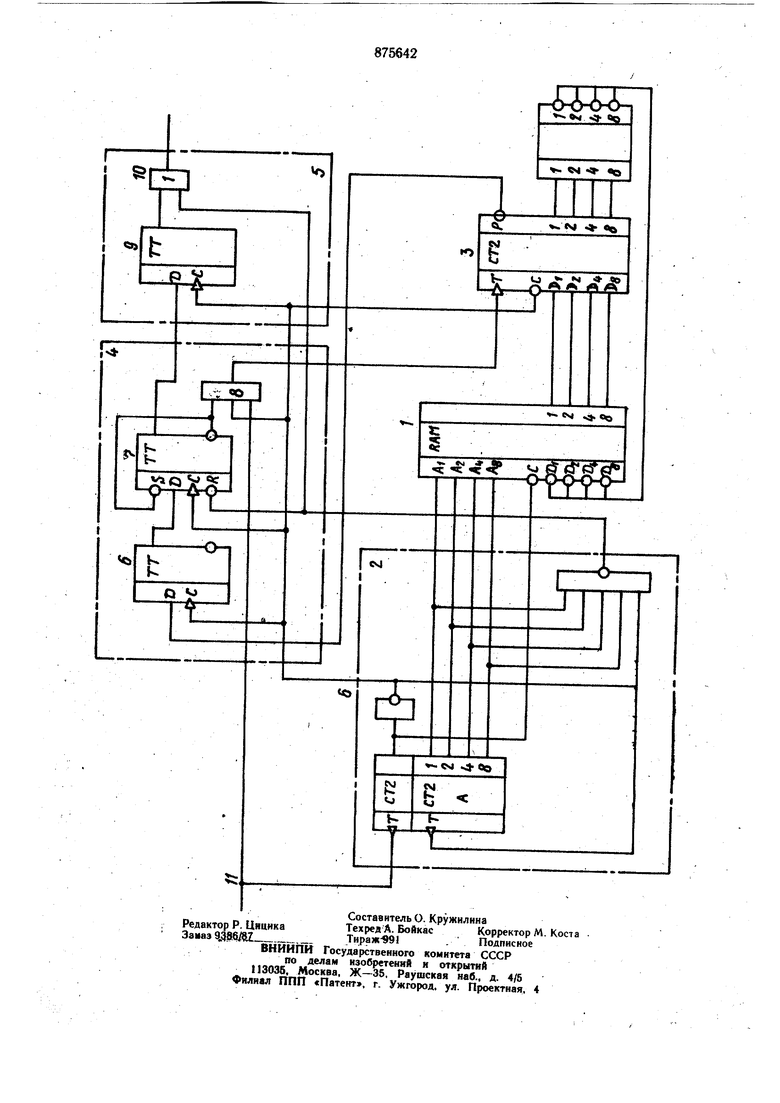

На чертеже представлена структурная qxeMa устройства.

Оно содержит регистр I с дешифратором на входе (запоминающий блок с дешифратором адреса), счетчик. 2 адреса, счетчик 3 числа, анализатор 4 переполнений, бдок 5 совпадения.

Анализатор 4 переполнений состоит из триггеров 6 и 7 регистра сдвига и элемента 8 И.

Блок 5 совпадения включает в себя триггер 9 (возможно D-триггер) и элемент 10 ИЛИ.

Позицией 11 обозначена входная шина устройства; счетчики 2 и 3 могут быть как двоичными, так и декадными (при десятичном пересчете).

Работает устройство следующим образом.

С помощью счетчика 2 и дешифратора на входе регистра 1 информация из регистра поочередно потетрадно переписывается в счетчик 3 и возвращается на то же место в регистр, причем возвращается неизменной, если отсутствовал при данном состоянии счетчика 2 сигнал на счетном входе счетчика 3.

Сигнал на счетном входе счетчика 3 формируется анализатором 4 в каждом цикле переполнения счетчика 2. Поданный на установочный вход анализатора 4 сигнал формирует разрешение добавления единицы в.следующую тетраду. Разрешение добавления единицы снимается, если нет переноса сигнала с выхода переполнения счетчика 3 из предыдущей тетрады.,

Таким образом, первые (младшие) разряды делителя частоты находятся в составе счетчика 2 и его переполнение является сигналом переноса в следующие разряды - начальную тетраду, размещенную в регистре 1, перенос из Которой в следующую тетраду регистра 1 сформируется анализатором 4, когда переполнится начальная тетрада и так далее.

Рассмотрим процесс работы делителя частоты детальнее.

Предположим, что регистр I и счетчик 3 обнулены, а разряды счетчика 2 имеют состояния «1. Поступивший на шину 11 положительный импульс (будем считать его нулевым) своим отрицательным фронтом переведет младший разряд счетчика 2 в состояние «О. При этом сформируется сигнал записи кода в регистр 1 и сигнал переполнения счетчика 2, который установит триггер 7 анализатора 4 в состояние «О. Триггер 6 анализатора 4 установится в состояние «1, поскольку на выходе переполнения счетчика 3 будет присутствовать уровень «1, свидетельствующий об отсутствии

переполнения в счетчике 3.

Поступивший на щину 11 следующий положительный импульс (будем считать его первым) пройдет через элемент 8 и изменит состояние счетчика 3 на «-f 1 (по переднему фронту). Отрицательный фронт поступившего импульса счета переведет младший разряд счетчика 2 в состояние «L, сформирует задний фронт импульса записи в регистр I и тем самым зафиксирует в регистре 1 по адресу «15 код «0001, изменит

5 состояние старших разрядов счетчика 2 на «0000, на выходе младшего разряда появится уровень «О, который откроет вход записи числа, хранящегося в регистре 1 по адресу «О в счетчик 3.

0 Следующий импульс (второй) на входной шине II своим отрицательным фронтом изменит состояние младшего разряда счетчика 2, сформирует окончание записи в счетчике 3, перепишет состояние «1 в триггеры 6 и 7, тем самым запретив передачу импульса на

счетный вход счетчика 3, запишет в триггер 6 состояние «1 и откроет вход записи кода в регистр 1.

Третий импульс на входной шине 11 сформирует задний фронт импульса записи кода в регистр 1, и тем самым зафиксирует в регистре 1 по адресу «О код «О, изменит состояние старших разрядов счетчика 2 на «0001 и откроет вход записи числа, хранящегося в регистре 1 по адресу «1

5 в счетчик 3.

Последующие входные импульсы (4, 5, ..., 32) поочередно переберут все адреса тетрад в регистре 1 от первого до пятнадцатого и из каждого из них считают в счетчик 3 и запишут обратно в регистр 1 код «0000.

33-й импульс после выборки по пятнадцатому адресу кода «0001 ; в счетчике 3 добавит к нему «4-1 и код «0010 вернется в регистр 1 по 15-му адресу.

Аналогичные циклы с периодом, равным

, периоду переполнения счетчака, будут повторяться до тех пор, пока по пятнадцатому адресу не будет записан, а затем выбран код «1111 код переполнения счетчика 3 (по 480-му импульсу).

В этот период на выходе переполнениГ счетчика 3 появится уровень «О, который будет зафиксирован по заднему фронту с 480-го импульса в триггере 6, по 482-му импульсу будет переписан в триггер 7 и разрешит прохождение 483-го импульса на счетный вход счетчика 3.

С приходом 512-го импульса по адресу «00 будет храниться код «0001, а по остальнь1м адресам - код «0000 и по адресу «15 будет код, который, начиная с кода «0000, будет меняться на «-f I через каждые 32 импульса.

Перенос в более старшие тетрады осуществляется аналогично, с той лишь разницей, что сигналы переполнения на выходе счетчика 3 будут поочередно появляться, иачиная с адреса пятнадцать до адреса, в который осуществляется перенос, причем, обязательно последовательно в одном цикле между сигналами переполнения счетчика 2. Необходимо отметить, что наличие сигнала переполнения с выхода счетчика 3 лишь в одном из адресов (а не поочередно, начиная с пятнадцатого адреса) ие вызывает Сформирования импульса на импульсном выходе анализатора, так как хотя сигнал на выходе младшего разряда счетчика 2 стремится по синхровходу переписать состояиие «О из триггера 6 в триггер 7, триггер 7 надежно остается в состоянии «1, определяемом связью нулевого выхода триггера 7 со своим единичным входом.

Поделенный импульс формируется в блоке совпадения 5, в котором триггер 9 формирует сдвинутый потенциал . разрешения счетного импульса счетчика 3.

Если во всех тетрадах регистра I хранится код «1IH, то, начиная с момента поступления импульса с выхода nepencknнения счетчика 2, триггер 7 будет сохранять состояние «О до следующего момента поступления следующего импульса. Тогда сдвинутый на период импульса с выхода младшего разряда счетчика 2 на триггере 9 потенциал поступит, как разрещающнй, на вход элемента ИЛИ 10, и отрицательный импульс переполнения с вывода счетчика 2 появится на шине, пройдет на выход и в следующем за этим периоде переполнения счетчика 2 в регистре 1 будут записаны по всем адресам коды «0000.

Таким образом, период следования импульса на выходной шине в 2 X А X 4 раз больше периода входных импульсов на шине И, где 2 - коэффициент пересчета млаД шего разряда счетчика адреса 2; А - количество используемых адресов (коэффициент пересчета старших разрядов счетчика адреса 2); 4 - коэффициент пересчета счет 1ика числа 3.

Технико-экономические преимущества устройства выражаю1-ся экономией элементов памяти и комбинационных логических элементов, что яри выполнении его в интегральном исполнении позволяет уменьшать площадь кристалла и количество полупровод никовых переходов, и, следовательно, получить экономию оборудования, затрат труда, уменьшения стоимости.

Формула изобретения

. Делитель частоты следования импульсов, содержащий регист с дещифратором на входе, отличающийся тем, что, с целью упрощения устройства, в него введены счетчик адреса, счетчик числа, блок совпадения и анализатор переполнений, импульсный выход которого соединен со счетным входом

счетчика числа, а потенциальный выход - с потенциальиым входом блока совпадения, синхронизирующий вход которого соединен с сиихронизирующим входом анализатора переполнений с входом записи счетчика чис: ла, и с выходом младшего разряда счетчика ,

® адреса, а стробирующий вход - с установочным входом анализатора переполнений и выходом переполнения счетчнка адреса, разрядные выходы которого соединены с. соответствующими адресными входами регистра с дешифратором на входе, информационные входы и выходы которого соединены соответственно с информационными выходами и входами счетчика числа, выход переполнения которого соединен с входом управления анализатора переполнений,стробирую0 щий вход которого подключен к счетному входу счетчика адреса и к входной шине.

5 соединен с первым входом элемента И, синхронизирующий вход - с вторым входом элемента И и синхронизирующим входом регистра сдвига, установочный вход - с обнуляющим входом вт9ро1х разряда регистра сдвига, нулевой выход которого подключен к его единичному входу и третьему входу элемента И, вход управления - с информационным входом первого разряда регистра сдвига, а импульсный и потенциальный выходы соответственно с выходом

5 элемента И и с единичным выходом второго разряда регистра сдвига.

O ,а второй вход соединен с выходом триггера, первый и второй входы которого являются соответственно потенциальным и синхронизующим входами блока совпадения. Источники информации,

J принятые во внимание при экспертизе

.

Авторы

Даты

1981-10-23—Публикация

1980-02-19—Подача