Изобретение относится к информационно-измерительной технике и обработке сигналов и может использоваться при увеличении частоты дискретизации цифровой последовательности.

Известен цифровой транверсальный фильтр, содержащий линию задержки с отводами и преобразователь кода, выполненный в виде постоянного запоминающего устройства (ПЗУ).

Недостатком этого фильтра являются большие аппаратурные затраты, обусловленные необходимостью использования ПЗУ большого объема, равного 2 N+1 m двоичных чисел, где N - число отводов линии задержки; m - разрядность входных чисел. Например, при реализации фильтра с 96 отводами v 16-разрядными входными данными требуемый обьем ПЗУ составит 2 двоичных чисел, что практически нереализуемо.

Наиболее близким к предлагаемому яв- (У) ляется цифровой нерекурсивный фильтр. / содержащий группу из N последовательно соединенных регистров сдвига, блок постоянной памяти, три регистра, сумматор, программно-временной блок, формирователь поправки, блок коммутаций, элемент ИСК-.

ЛЮЧАЮЩЕЕ ИЛИ.

Алгоритм работы фильтра основан на гО преобразовании уравнения свертки для вы- 00 числения выходного сигнала цифрового не- sQ рекурсивного фильтра таким образом, что Qs для заданных коэффициентов фильтра вы- ко ходное значение можно вычислить с помощью лишь операций сложения и сдвига. Это достигается путем введения функции разрядов отсчетов входной последовательности с N двоичными, аргументами (N - дли- на импульсного отклика фильтра) и выполнения сложения сдвинутых значений этой функции. Функция характеризуется конечным числом возможных значений, которые хранятся в ПЗУ.

Недостатком этого фильтра являются большие аппаратурные затраты, которые обусловлены большим объемом требуемого ПЗУ, когда импульсный отклик фильтра имеет значительную длину.

Цель изобретения - уменьшение аппаратурных затрат на реализацию фильтра.

Поставленная цель достигается тем, что в цифровой интерполяционный фильтр, содержащий группу регистров, выходы разрядов каждого предыдущего регистра группы соединены с одноименными информационными входами разрядов каждого последующегорегистрагруппы, программно-временной блок, первые, второй третий и четвертые выходы которого соединены соответственно с одноименными адресными входами блока коммутации, тактовыми входами первого, второго регистров и одноименными управляющими входами третьего регистра, выходы блока коммутации соединены с одноименными информационными входами первого регистра, блок постоянной памяти, выходы которого соединены с одноименными информационными входами второго регистра, выходы которого соединены с одноименными первыми входами суммы сумматора, выходы разрядов суммы которого соединены с одноименными информационными входами разрядов третьего регистра, выходы разрядов которого являются информационными выходами фильтра, введены четвертый и пятый регистры, триггеры и шина нулевого потенциала, информационные входы разрядов первого регистра группы являются информационными входами, фильтра, выход младшего разряда и последовательный информационный вход каждого регистра группы объединены соответственно и подключены к соответствующим информационным входам блока коммутации, тактовый вход программно- временного блока объединен с тактовыми входами регистров группы, третьего, четвертого и пятого регистров и является тактовым входом фильтра, вход Пуск программно-временного блока является входом Пуск фильтра пятые, шестые, седьмой, восьмые, девятый и десятый выходы программно-временного блока соединены соответственно с одноименными управляющими входами регистров группы, одноименными первыми входами блока постоянной памяти.ус- тановочным входом второго регистра, одноименными управляющими входами четвертого регистра, тактовыми входами первого, второго триггеров и установочными входами первого, второго

триггеров, третьего, четвертого и пятого регистров, выходы первого регистра соединены с одноименными вторыми входами блока постоянной памяти, вторые входы суммы сумматора подключены к выходам одноименных разрядов третьего регистра, выход младшего разряда которого соединен с последовательным информационным входом четвертого регистра, выходы которого явля0 ются информационными выходами фильтра, информационный вход и выход первого триггера подключены соответственно к выходу старшего разряда суммы сумматора и последовательному информационному вхо5 ду третьего регистра, выходы разрядов переноса сумматора соединены с одноименными информационными входами разрядов пятого регистра, кроме информационного входа младшего рахряда, инфор0 мационный вход младшего разряда пятого регистра подключен к шине нулевого потенциала, информационный вход и выход второго триггера подключены соответственно к выходу старшего разряда переноса сумматора и по5 следовательному информационному входу пятого регистра, выходы которого соединены с одноименными входами переноса сумматора, управляющие входы пятого регистра подключены к одноименным чет0 вертым выходам программно-временного блока, одиннадцатый выход которого является управляющим выходом фильтра.

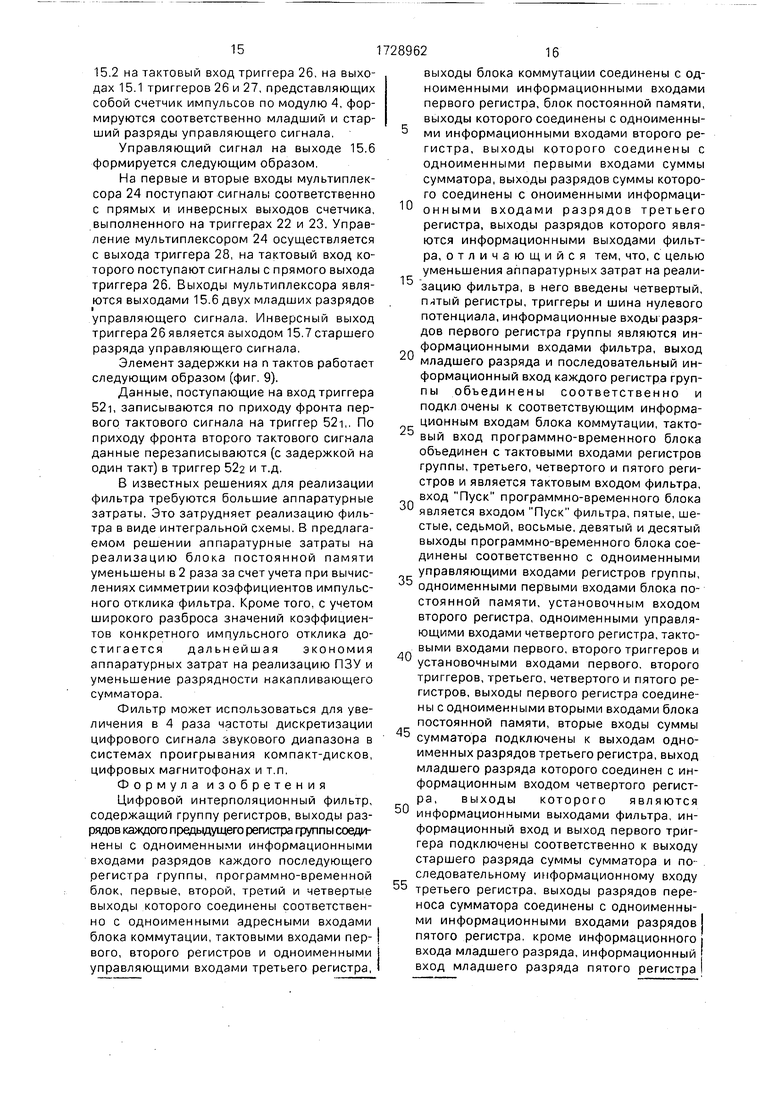

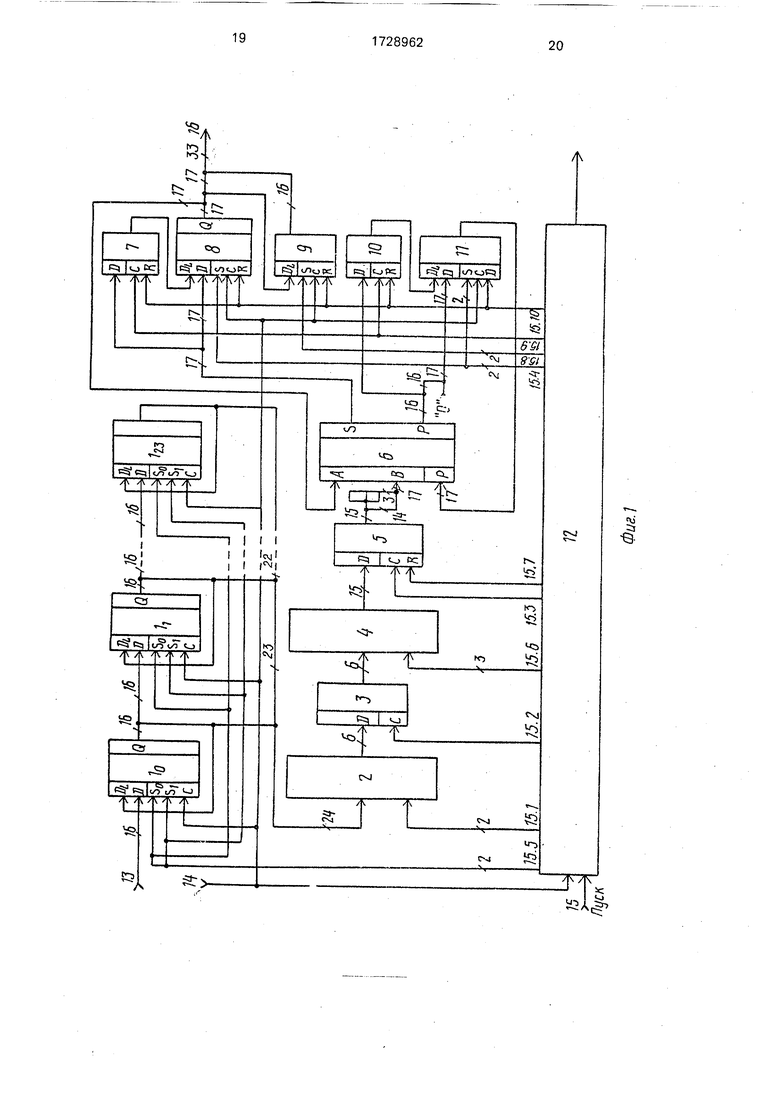

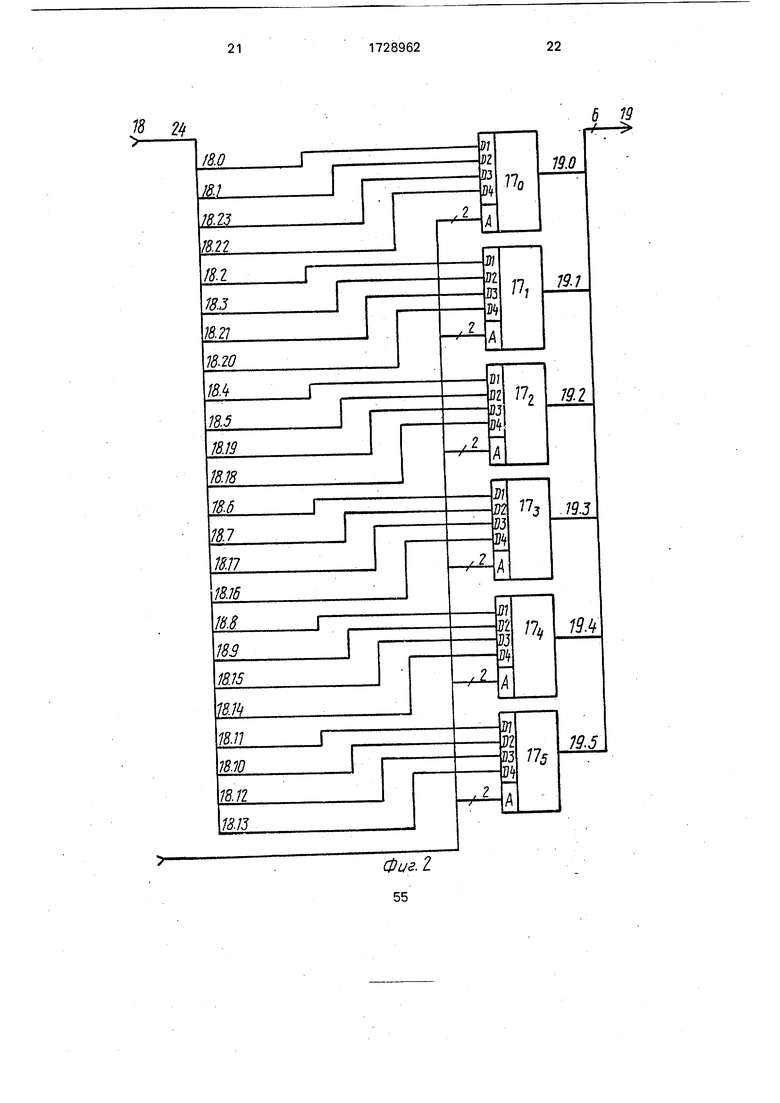

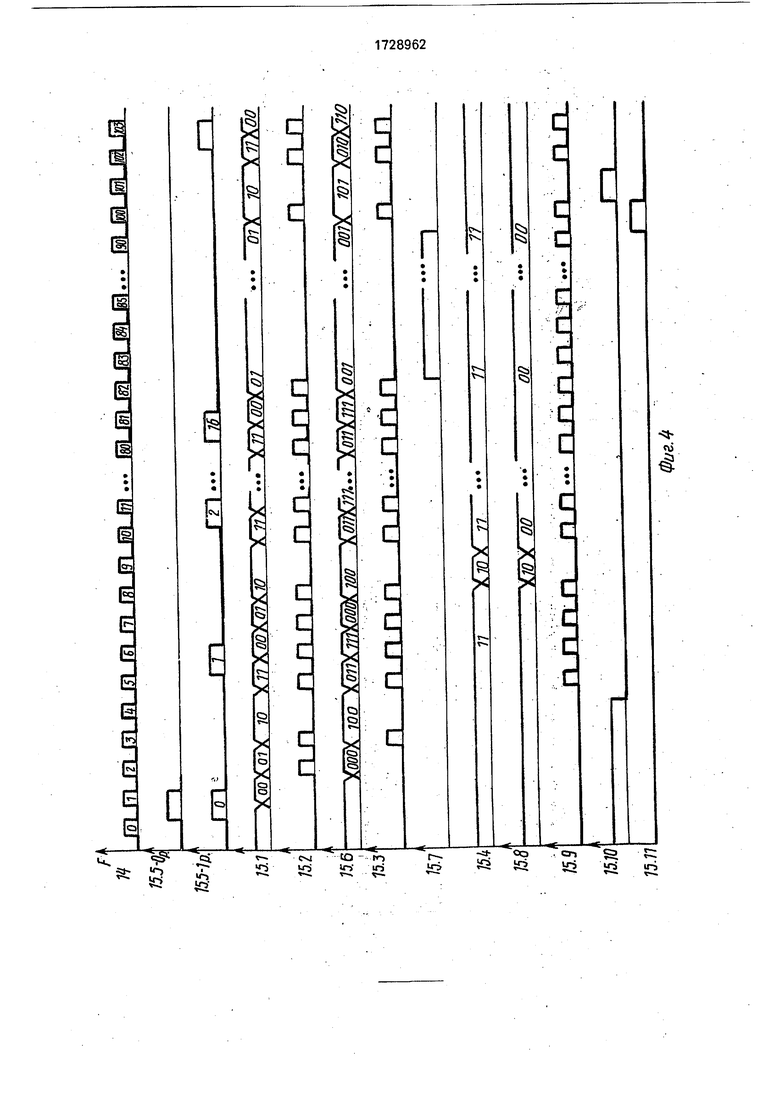

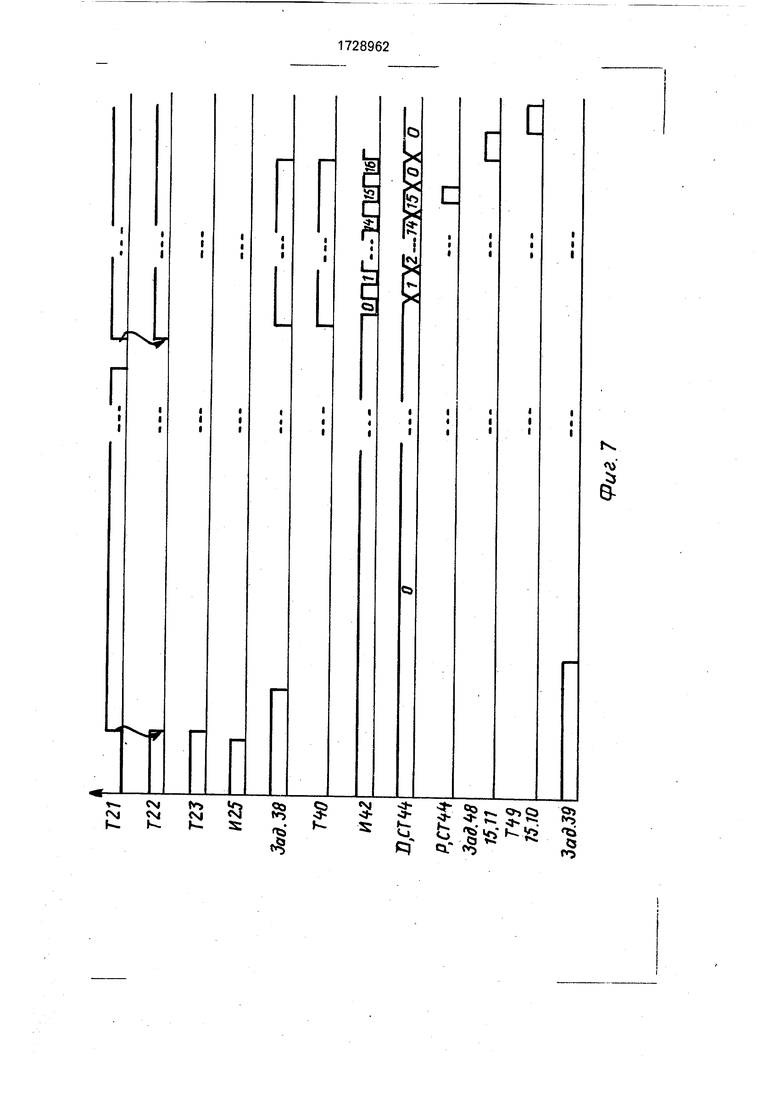

На фиг. 1 приведена функциональная схема цифрового интерполяционного филь5 тра; на фиг. 2 - функциональная схема блока коммутации; на фиг. 3 - функциональная схема сумматора; на фиг. 4 - временные диаграммы, поясняющие работу фильтра, на фиг. 5 - функциональная схема программно-вре0 менного блока; на фиг. 6-8 - временные диаграммы работы программно-временного блока; на фиг. 9 - функциональная схема элемента задержки на п тактов.

Фильтр содержит (фиг. 1) группу регист5 ров 1о...123, блок 2 коммутации, первый ре: гистр 3, блок 4 постоянной памяти, второй регистр 5, сумматор 6, первый триггер 7, третий и четвертый регистры 8 и 9, второй триггер 10, пятый регистр 11, программно0 временный блок 12, информационный вход 13, тактовый вход 14, вход 15 Пуск и информационные выходы 16.

Блок 2 коммутации содержит (фиг. 2) мультиплексоры 17о...17д. входы 18 данных

5 и выходы 19 данных.

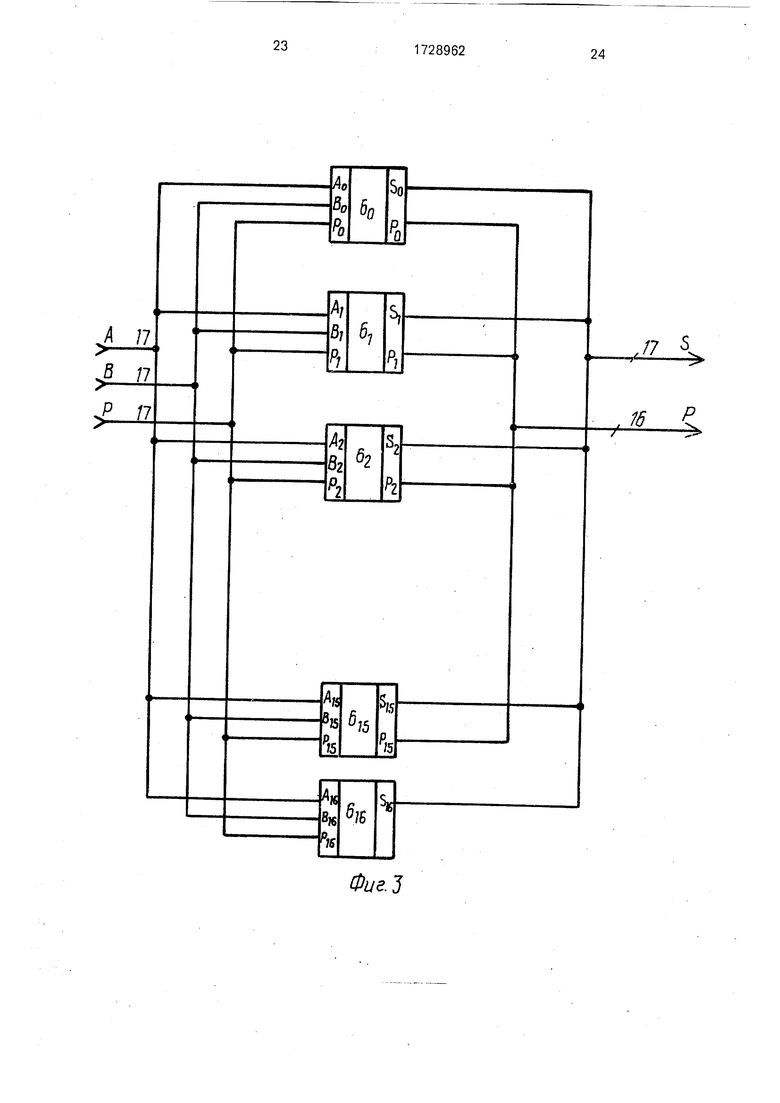

Сумматор 6 содержит (фиг. 3) полные одноразрядные сумма торы 6o...6ie.

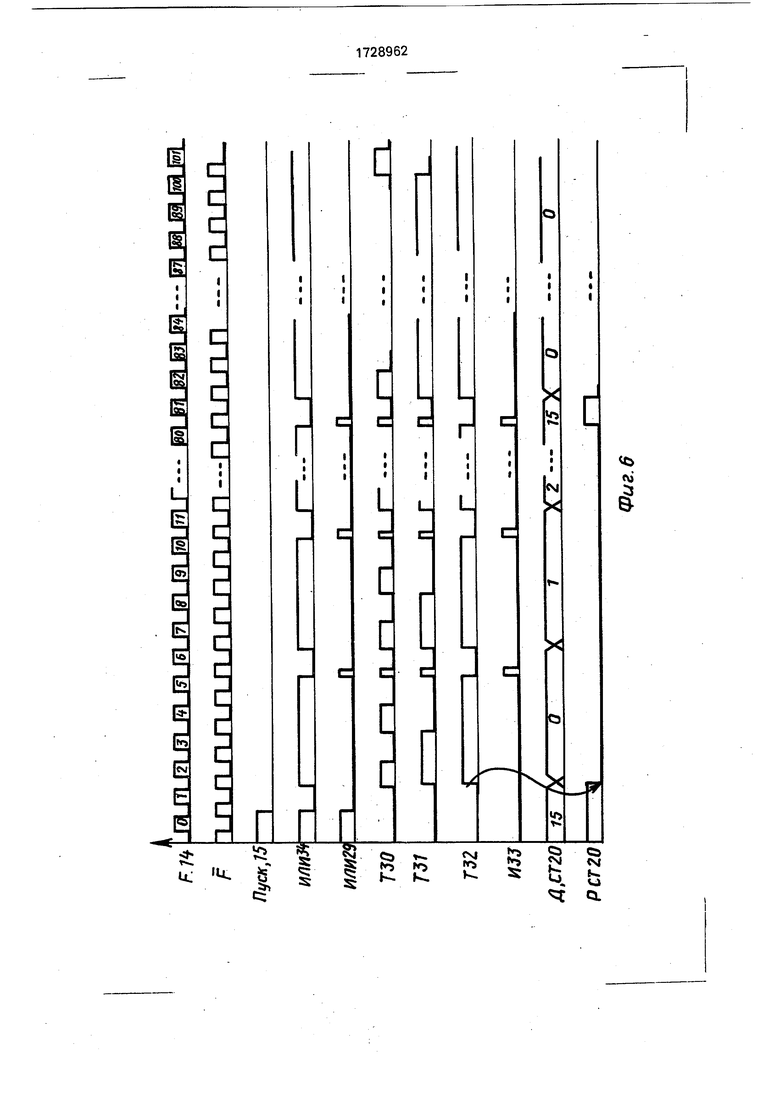

Программно-временной блок 12 содер- жит(фиг. 5)счетчик 20. триггеры 21-23, мультиплексор 24, элемент 1/125, триггеры 26-28,

элемент ИЛИ 29, триггеры 30-32, элемент И 33, элемент ИЛИ 34, элемент 35 задержки на три такта, элементы И 36 и 37, элемент 38 задержки на два такта, элемент 39 задержки на четыре такта, триггер 40, элемент ИЛИ 41, элементы И 42 и 43, счетчик 44, элемент И 45, элементы НЕ 46 и 47, элемент 48 задержки на два такта, триггер 49 и элементы ИЛИ 50 и 51.

Элементы 35, 38, 39 и 48 задержки на п тактов содержит (фиг. 9) триггеры 521,..52п.

Идеальная процедура интерполяции при увеличении частоты дискретизации в L раз предполагает формирование последовательности v(n), включающей L-1 отсчет с нулевой амплитудой в интервалах между значениями исходной последовательности х(п). Затем последоветельсность v(n) пропускает через идеальный фильтр нижних частот с характеристикой, равной L в полосе частот I о) я/Т и равной нулю в полосе частот л /Т I а) я /Т1, где Т1 T/L - новый период дискретизации.

Поскольку создать идеальный фильтр нижних частот практически невозможно, то используются цифровые фильтры, аппроксимирующие идеальную характеристику. Для большинства случаев (например, в звуковой технике) приемлимыми являются значения отклонения характеристики порядка ± 70 дБ в полосе задерживания и ± 0,3 дБ в полосе пропускания. Этим условиям для случая L 4 удовлетворяет фильтр с конечной импульсной характеристикой длины, равной 96, и с линейной фазой.

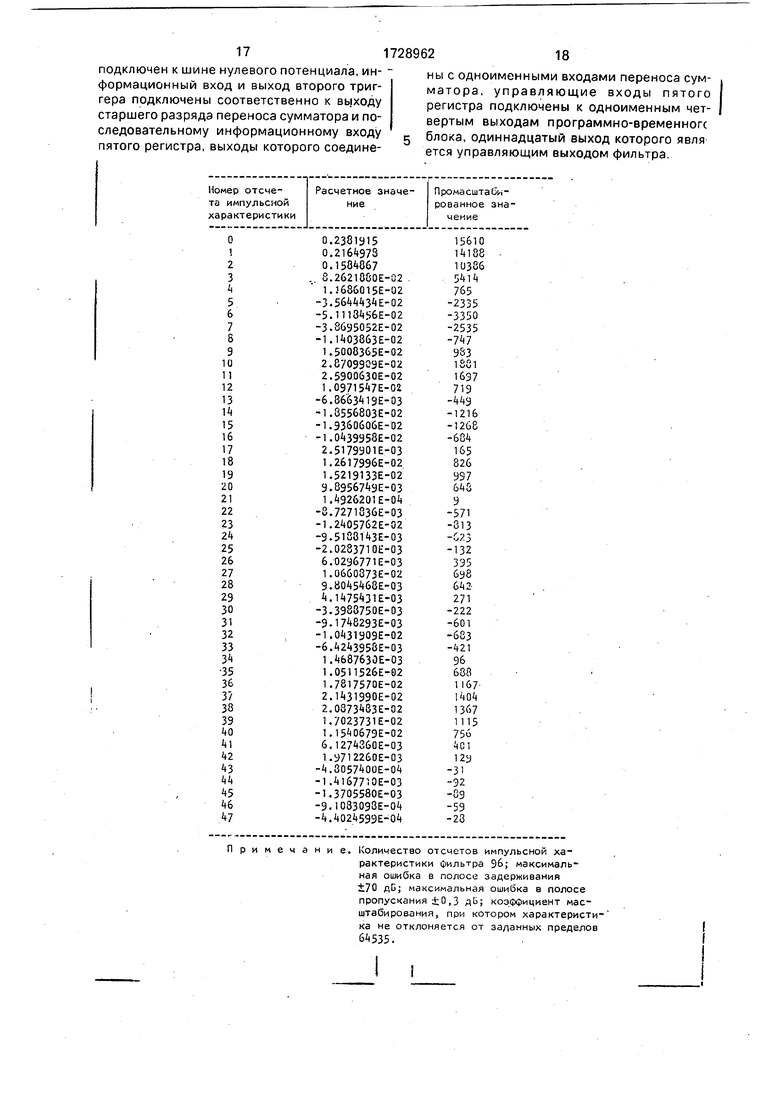

Расчетные значения коэффициентов такого фильтра приведены в таблице.

Учитывая то обстоятельство, что только 1/4 часть входных отсчетов является нулевой, можно по 24 входным отсчетам х(п), . х(п-1),..., х(п-23) получить четыре последовательных значениях выходных отсчетов у0(п) yi(n), y2(n), уз(п).

Учет симметрии коэффициентов п hgs-i.

i 0,1 47 позволяет уменьшить объем

ПЗУ, необходимый для хранения значений частичных сумм произведений с участием этих коэффициентов.

Выходные отсчеты цифрового интерполяционного фильтра вычисляются согласно следующим выражениям:

Y0(,-j) ((п-2),6х1п-ЖЬиХ(п-6) b xto-S) h xin-m (x( foiaxfo-3/ b20x.(T S) 8xf/7-7y+hjeA -9/+fr+0x(n-tO/ (г7 - in- bigx(i7- Wj +h fo-tfA + Ьз5х.6ь15)Ь47.хГг7-12У + Ь7 x (n- 2.2)J h1s(n-20f+h2j(n-1®Jt. (731хСгг -16/ + Ь39лГп- } +Ь„хЈп-13/} }И)

Y n VCLyfoAhgXfa-Z) Ь„х(п-4/ «Ьих(л-6)Ч„х(п-8) - b«j fo-li J

Lb4x(i7-1)J h,,xfP-3)f 2fXfn-S)J+hMxfn:7y Ьлх(г}-9);Ь((

(n- 2 lA f,8x(r -I9) «h26x(n-i7) IS A

bv6x - yj b6xfi7-22y+n Afrj-20y .)J + f/3ff(n-(6)- h;jjX(ro-f f)J+

42

Л{Г7-13)},

Y2(r)Ј2J{fh2x(n)1+b1ej fn-2} hf8x(n- f} +

t Ь26ХСП -б/+ И31(К(/7 8) т7ихГг7-11)Ъ016А(г7-1)

(гг-зУ Ь2з 1(п-5Аь х(г лЛнзбх(-9А t fn-lo xfrj-ZSytbjXfn l/ hj fn-ig) хГп-17)(п-15У Ч5хГи-12/ - hJxfr-22 h0)t(r1-2«J h,2)x(n-{8)J 1,г&хСп- бАьэтх(п-)гх(п-1Л }/ С Y3fn) Ј (пА h X/n-2J h 9X(n- ) /Ь х -бАн иСв-в Ь хГп-ИЛ дГп А

h1sx -3AMn-s) Vfn 7; T4x 9jV,

„xfr- v(- VM9jJJ

b -iT xru-K xfo-izy t х(г7-г2) « hl2x(f7-2(Ah20x( i7-t8)J Ьгб x (r -16)J hM(n- ) h,e xfn -f3)J|} ,

I. .W

где X(K)J - j-й разряд входного отсчета х(к); m - количество разрядов входных отсчетов(т 16).

Согласно формулам (1)-(4) вычисление значений выходных отсчетов производится путем накопления взвешенных сумм произведений j-x разрядов входных отсчетов на

соответствующие значения 24 коэффициентов фильтра, j-ты разряды принимают значения нуля или единицы. При этом суммы из 24 произведений разбиваются на четыре суммы по 6 произведений каждая. В формулах (1)-(4) суммы из б произведений заключены в квадратные скобки. Их возможные значения хранятся .в ПЗУ.

Число возможных значений суммы 6 произведений-равно 26 64. Общее число

различных сумм 6 произведений, необходимых для получения всех четырех выходных отсчетов, равно 8. Заметим, что за счет сигт метрии коэффициентов фильтра для получ( ния уз(п) и уз(п) нужны те же частичны суммы, что и для получения соответственн yi(n) и у2(п). Таким образом, в ПЗУ необходь

мо хранить 8 таблиц по 64 значения в каждой, т.е. всего 8 64 512 значений.

Максимальные значения, которые хранятся в ПЗУ, определяются максимальным значением суммы коэффициентов фильтра, входящих в частичные произведения. Для уменьшения разрядности ПЗУ слагаемые группируются в частичные суммы таким образом (исходя из конкретных значений коэффициентов), чтобы максимальные значения всех частичных сумм были приблизительно равны. Предпосылкой возможности уменьшения разрядности является то, что, как правило, коэффициенты имеют большие значения для начальных индексов и быстро уменьшаются с увеличением индекса-коэффициента. Соотношение между значениями начального и последнего коэффициентов может составлять 10 . Поэтому возможно добиться существенной экономии объема ПЗУ, а также уменьшить разрядность накапливающего сумматора. Необходимые перекоммутации можно осуществить перед подачей разрядов входных отсчетов на ПЗУ.

Выражения (1)-(4) записаны с учетом перегруппировки слагаемых. Максимальное значение (по абсолютной величине) каждой частичной суммы не превышает 2 . С учетом знакового разряда разрядность ПЗУ равна 15.

После накопления слагаемого выходного отсчета, которое формируется младшими разрядами () всех входных данных (в приведенных формулах эти слагаемые заключены в фигурные скобки, младший (нулевой) разряд накопленной суммы больше не будет принимать участие в процессе накопления и может храниться отдельно. Точно так же после накопления слагаемого выходного отсчета, сформированного первыми разрядами () всех входных данных, первый разряд накопленной суммы не будет принимать участие в процессе накопления и может храниться отдельно и т.д. При аппаратурной реализации накапливающего сумматора это позволяет избежать увеличения разрядной сетки сумматора с увеличением количества слагаемых. Разрядная сетка определяется максимальным значением, которое может быть получено при сложении четырех частичных сумм. Для рассматриваемого случая это значение равно 2 , а с учетом знакового разряда необходимо 17 разрядов.

Фильтр работает следующим образом.

Значения входных отсчетов, поступающие на вход 13 устройства, последовательно записываются в группу регистров 1о...123. При этом на n-м шаге записи в первом регистре 1о будет записано значение отсчета х(п), во втором регистре 11 - значение отсче0

5

0

5

0

5

0

5

0

5

та х(п-1), в третьем регистре 12 - значение отсчета х(п-2) и т.д., в двадцать четвертом регистре 123 значение отсчета х(п-23). Запись происходит после установления в середине нулевого периода на входах управления сдвигом влево 15.5 Ор. и сдвигом вправо 15.5 1р. сигналов единичного уровня по приходу фронта тактового сигнала F с входа 14. В середине первого периода тактовой частоты на выходах 15.5 - Ор. и 15.5 - 1р. блока 12 устанавливаются нулевые сигналы, которые переводят регистры 1о...123 в режиме хранения данных. В первом периоде тактовой частоты значения младших (нулевых) разрядов x(n-i)° входных данных х(п), х(п-1)х(п-23)с выходов младших разрядов Qo регистров 1о...123 поступают на вход данных блока 2 коммутации, В блоке 2 коммутации производится коммутация определенных шести из 24 входов не шесть выходов по управлящим сигналам, поступающим с выходов 15.1 блока 12.

Коммутация производится в соответствии с индексами i для x(n-i) в выражениях (1)-(4). В первом такте коммутируются входы, номер которых соответствует значению i в x(n-i) для первых шести составляющих в выражении (1). В следующем такте - для вторых шести составляющих, затем для третьих шести составляющих и, наконец, для четвертых шести составляющих. Затем все циклически повторяется. Например (фиг. 2), в первом такте на выходы 19.0...19.5 будут коммутироваться входы 18.0, 18.2, 18.4, 18.6, 18.8 и 18.11 соответственно, во втором такте - входы 18.1, 18.3, 18.5, 18.7, 18.9, 18.10 и т.д.

С выходов блока 2 коммутации сигналы поступают по шестиразрядной шине на входы регистра 3 и в начале второго периода тактовой частоты заносятся в этот регистр по управляющему сигналу входа 15.2. В это же время значения нулевых разрядов x(n-i)° входных данных, поступающие на входы блока 2, коммутируются в соответствии с описанной процедурой.

В начале третьего, периода тактовой частоты значения этих сигналов записываются в регистр 3.

Во втором периоде тактовой частоты данные, записанные в регистр 3 в его начале, по шестиразрядной шине поступают на входы младших разрядов адреса блока 4. На входах 15.6 старших трех разрядов блока 4 устанавливается код номера таблицы. Номер таблицы соответствует индексу i(...7) для hi в первом слагаемом каждой частичной суммы в (1)-(4). При вычислении уо(п) номера таблиц будут в соответствии с (1) чередоваться следующим образом: i 0, 4, 3, 7. Каждая таблица содержит все возможные

коммутация нулевых разрядов x(n-i)° входных данных в блоке 2 коммутации; запись в регистр 3 данных с выхода блока 2 коммутации, сформированных в предыдущем такте; запись в регистр 5 значения частичной суммы, сформированного на выходах блока 4 в

54 комбинации сумм шести коэффициентов фильтра hi в соответствующей частичной сумме, По значению, поступающему на вход младших разрядов адреса блока 4 во втором периоде тактовой частоты, производится выборка одного из 64, наперед вычисленного из хранящегося в таблице i 0, значения первой частичной суммы. В начале третьего периода тактовой частоты значение частичной суммы записывается по управляющему сигналу в регистр 5 и с его выхода поступает на первые входы в сумматор 6, на входы которого поступают данные с выходов регистра 8, а на входы переноса - данные с выходов регистра 11. Сумматор 6 представ ляет собой набор полных одноразрядных сумматоров (фиг. 3), Значений разрядов переносов, сформированные в определенном такте работы, подаются в следующем тактеа через регистр триггер 10 на входы пе-4 реносов со сдвигом на один разрядов сторф- ну старших разрядов. При этом.на нулев,е$Г вход переноса постоянно подается;щйебое значение (младший вход регистра, соединен с шиной нулевого потенциала).. :

Так как отрицательные значения прёд- ставляются в устройстве в дополнительном коде, то. необходимо продублировать знаковый разряд, поступающий на вход Bi4 сум-. матора 6 в старших разрядах Вfs и Bie первого входа этого сумматора. A Taic как результат суммирования предусматривает-, ся в процессе вычисления сдвигать в стора- ну младших разрядов, то необходима по сдвиге значение вводимого старшего разряда сохранять равным значению старшего разряда. Это обеспечивается путем хране: ния старших разрядов слова суммы и слава переноса в триггерах 7 и 10 соответственно. При сдвиге младшие разряды слова суммы записываются в регистр 9.

В начале третьего периода тактовой частоты значения нулевых разрядов x(n-i)° входных данных с выходов младших разрядов Qo регистров 1о...1аз поступают на вход данных блока 2, где производится соответствующая коммутация.

В начале четвертого периода тактовой частоты производится только обнуление содержимого регистров 8,,9 и 11 и триггеров 7 и 10 по управляющему сигналу с входа 15.10.. В начале пятого периода тактовой частоты производятся следующие операции:

10

15

20

5

о

5

0

5

0

5

предыдущем такте; запись в регистры 8 и 11 и триггеры 7 и 10 значений слова суммы и слова переноса, сформировавшихся в предыдущем такте на выходах сумматора 6 по управляющим сигналам с входов 15.4 и 15.9.

В середине пятого периода тактовой частоты на выходе 15.5- 1р. блока 12 устанавливается единичный сигнал, который переводит регистры 1о...123 в режим сдвига разрядов данных влево (в сторону младших разрядов). Сдвиг производится по приходу фронта импульсов тактовой частоты F. В середине следующего периода на выходе 15.5-1 р. устанавливается нулевой сигнал, переводящий регистры 1с....123 в режим хранения данных. Так как в регистрах 1о...123 выходы младших разрядов Qo соединены с входами данных при сдвиге влево DL, то этот сдвиг будет циклическим.

В начале шестого периода тактовой частоты происходит сдвиг разрядов данных в регистрах 10...123, и значения первых разрядов x(n-i)1 входных данных с выходов млад- ших разрядов Qo входных регистров поступают на входы данных блока 2 коммутации. Кроме того, выполняются все те операции, которые производились в пятом периоде тактовой частоты. В результате в регистрах 8 и 11 и триггерах 7 и 10 запишутся значения слова суммы и слова переноса для суммы значений первой и второй частичных сумм в соответствии с (1).

Действия в седьмом и восьмом периодах тактовой частоты полностью повторяют действия в пятом периоде. В результате в регистрах 8 и 11 и триггерах 7 и 10 записываются значения для суммы значений всех четырех частичных сумм в соответствии с (1),

В девятом периоде тактовой частоты происходит лишь сдвиг данных в регистрах 8, 9 и 11 по управляющим сигналам с входов 15.4 и 15.8. После этого на второй вход сумматора 6 поступает сдвинутая на один разряд в сторону младших разрядов накопленная сумма с выхода регистра 8. На первый вход сумматора 6 поступает значение частичной суммы, выбранное из блока 4 по коду первых разрядов входных данных (т.е. сдвинутых относительно предыдущих, нулевых, разрядов на один разряд), а на вход переноса - сдвинутое на один разряд слово с выходов регистра 11.

Затем в каждых следующих пяти периодах тактовой частоты полностью повторяется процедура, описанная в пятом - девятом периодах. Так будет продолжаться до тех пор, пока в сумматоре 6 и регистрах 8, 9 и 11 не накопятся значения частичных сумм от всех 16 разрядов входных данных. При этом в начале 81-го периода тактовой

11

частоты происходит очередной сдвиг разрядов данных в регистрах 1о...1аз, на выходах которых опять устанавливаются значения нулевых разрядов x(n-i)° входных данных, которые будут использоваться при вычислении второго выходного отсчета у i(n). Операции в 81-м и 82-м периодах полностью повторяются операции в 6-м и 7-м периодах тактовой частоты.

В 83-м периоде тактовой частоты производится только запись в регистры 8 иг 11 и триггеры 7 и 10 значений суммы со слова переноса, сформировавшихся в предыду1 щем такте, т.е. слова суммы со слова переноса результирующего значения уо(п), а также обнуление регистра 5 управляющим сигналом с входа 15.7.

В следующих 16 тактах (84-89) выполняется операция сложения слова суммы и слова переноса. При этом на первый вход сумматора 6 поступает нулевое значение с регистра 5, на второй вход - данные с выхода регистра 8 (слово суммы), а на вход переноса - данные с выхода регистра 11. (слово переноса). На каждом такте в сумматоре 6 производятся сложение слова суммы со словом переноса и запись результатов в регистры 8 и 11 и триггеры 7 и 10 по управляющим сигналам с входов 15.4 и 15.9. Так как разряды выходного слова переноса с регистра 11 поступают на входы слова переноса сумматора 6 со сдвигом на один разряд с сторону старших разрядов, то через 16 тактов в 99-м такте в регистре 11 будет храниться нулевое значение, а в регистре 8-старшие разряды выходного результата уб(п), в регистре 9 - младшие разряды выходного результата уо(п). В середине 99- го такта на управляющем выходе 15.11 формируется импульс, по фронту которого производится перезапись во внешнее устройство значения у0(п) с выхода 16.

В начале 100-го такта производятся запись в регистр 3 значения с выхода блока 2 коммутации, в котором с 82-го такта постоянно сохранялось значение комбинации нулевых разрядов для выборки значения второй частичной суммы для yi(n), запись в регистр 5 значения первой частичной суммы с выхода блока 4. В середине 100-го такта производится обнуление регистров 8, 9 и 11 и триггеров 7 и 10.

Работа устройства в тактах с 101-го по 196-й полностью повторяет работу устройства 4-99-м тактах. Разница состоит лишь в ином формировании номеров таблиц на управляющих выходах 15.6 в соответствии с индексом i (при hi в первом слагаемом каждой частичной суммы) в (2) для вычисления У|(П).

2896212

В середнине 196-го периода тактовой частоты на управляющем выходе 15.1 Т формируется импульс, по фронту которого производится перезапись во внешнее

5 устройство значения yi(n) с выходов 16. Аналогично вычисляется значение у2(п) в 197- 293-м тактах и значение уз(п) в 294-390-м тактах. При этом в начале 372-го периода тактовой частоты вместо сдвига разрядов

10 данных в регистрах 1о...,123 производится, запись нового входного отсчета в регистр 1о и перезапись данных в остальных регистрах Н..123 путем формирования дополнительного единичного сигнала на управляющем

15 выходе 15.5 - Ор, аналогично первому периоду тактовой частоты. В остальном при вычислении последующих выходных значений Уо(п+1), yi(n-H), y2(n+1), уз(п+1), ус(п+2),... ра- бота устройства полностью повторяет опи20 санную.

Блок 12 работает следующим образом (фиг. 1,4-9).

Управляющие сигналы, формируемые на выходах блока 12, периодически повторя25 ются при вычислении каждого выходного злачения. Исключение составляет управляющий сигнал с выхода 15.5 - Ор, который формируется в четыре раза реже.

Начальные установки производятся до

З о начала работы единичным уровнем сигнала Пуск. При этом производятся запись в счетчик 20 двоичного значения 1111 (путем подачи единичных значений на входы данных и тактовый вход счетчика 20) установле35 ниеединичныхзначений-втриггерах 22 и 23, а также обнуление через элемент ИЛИ 29 триггеров 30-32, а через элемент ИЛИ 41 - триггера 40 и второго счетчика 44. На выходе переполнения счетчика 20 уста40 новится активный единичный уровень. Единичные сигналы, поступающие на входы элемента И 25, устанавливают на его выходе, который является выходом 15.5 - Ор., единичный уровень.

45 Единичный уровень с инверсного выхода триггера 40 разрешает прохождение через элемент И 43 импульсов тактовой частоты F. Инвертированные на элементе НЕ 46 импульсы тактовой частоты F посту50 пают на тактовый вход триггера 30.

С приходом1 нулевого значения сигнала Пуск на входах обнуления триггеров 30-32 устанавливается нулевой уровень и импульсами инвертированной тактовой частоты

55 производится счет в счетчике, выполненном на триггерах 30-32 (счет производится по фронту тактовых сигналов), фиг. 6. Через четыре периода тактовой частоты на прямых выходах триггеров 30 и 31 и инверсном выходе триггера 32 установятся единичные значения, по которым на выходе элемента И

33 установится единичное значение, которое через элемент ИЛИ 29 производит обнуление триггеров 30-32. Затем весь процесс повторяется. Сигнал на инверсном выходе 15.5-1 р. триггера 32 является выходным управляющим сигналом.

После установления на прямом выходе триггера 32 единичного значения (в середине 1-го периода тактовой частоты), которое поступает на вход счета счетчика 20, на выходе переноса счетчика 20 установится нулевое значение и, затем, на выходе элемента И 25 устанавливается нулевое значение. Нулевое значение с выхода переноса с задержкой на пол периода тактовой частоты записывается в триггер 21 и с его инверсного выхода поступает на счетчик, выполненный на триггерах 22 и 23..При этом на прямых выходах.триггеров 22 и 23 установится двоичное значение 00, а на инверсных - значение 11. При вычислениях каждого выходного значения у(п) на выходе переполнения счетчика 20 формируется сигнал переполнения Р, который через триггер 21 с задержкой на полпериода тактовой частоты поступает на вход триггера 22 и увеличивает значение счетчика на триггерах 22 и 23 на единицу. При вычислении первого выходного значения на выходах счетчика устанавливается двоичное значение 00, второго - 01, третьего - 10. четвертого - 11, пятого - 00 и т.д. Сигналы переполнения, сформированные при вычислении четвертого , восьмого и т.д. значений, поступают через элемент И 25 на выход 15.5 - Ор.

Сигнал переполнения с выхода счетчика 20 также поступает через элемент 38 задержки на два такта на тактовый вход триггера 40. Содержимое триггера 40 (нулевое значение на прямом выходе) при этом изменяется на противоположное (единичное), на инверсном выходе устанавливается нулевое значение, которое запрещает прохождение импульсов тактовой частоты F через элемент И 43. Единичное значение с прямого выхода триггера 40 разрешает прохождение импульсов тактовой частоты через элемент 42. Импульсы тактовой частоты с выхода элемента поступают на вход счета счетчика 44, на выходе переноса которого через 15 периодов тактовой частоты установится активное единичное значение. После задержки на элементе 48 задержки на два такта этим единичным сигналом через элемент ИЛИ 41 производится обнуление триггера 40 и счетчика 44. При этом опять разрешается прохождение импульсов тактовой частоты F через элемент И 43.

Сигнал с выхода 15.11 элемента 48 задержки на два такта является управляющим

5

сигналом. Этот сигнал, задержанный на один период тактовой частоты на триггере 49, поступает на первый вход элемента ИЛИ 51, на второй вход которого поступает за- 5 держанный на 4 такта на элементе 39 сигнал Пуск. Выход элемента ИЛИ 51 является управляющим выходом 15.10.

Прямой выход триггера 40 является управляющим выходом 15.7. 1 Управляющие сигналы на выходах 15.2, 15.3, 15.4 и 15.8 формируются следующим образом. ,

Сигнал Пуск и сигнал с прямого выхода триггера 32 поступают через элемент 1 ИЛИ 34 на вход данных элемента 35 задержки на три такта. На тактовый вход этой схемы поступают импульсы тактовой частоты с элемента НЕ 46. Задержанный на три „ периода тактовой частоты сигнал с прямого выхода элемента 35 поступает на выход 15.4 младшего разряда управляющего сигнала. На выход старшего разряда этого сигнала постоянно поступает значение логической единицы.

Задержанный на три периода тактовой частоты сигнал с инверсного выхода элемента 15 поступает на 15.8 выход старшего разряда управляющего сигнала. На выход - младшего разряда этого сигнала постоянно поступает значение логического нуля.

Импульсы тактовой частоты F через элемент И 36, управляемый с инверсного выхода элемента 35 з-адержки на три такта, поступают на выходы 15.2 и 15.3.

После установления на инверсном выходе триггера 40 нулевого значения прекращается поступление через элемент И 43 импульсов тактовой частоты. При этом пре- кращается формирование сигналов на выхо- дах 15.2, 5.3, 15.4 и 15.8. Формирование этих сигналов возобновляется после установления на инверсном выходе триггера 40 единичного значения.

Управляющий сигнал на выходе 15.9 формируется следующим образом.

Единичный сигнал с прямого выхода триггера 40 разрешает прохождение тактовых импульсов через элемент И 45 на второй вход элемента ИЛИ 50. На первый вход элемента ИЛИ 50 поступает управляющий сигнал с выхода 15.2. На выходе 15.9 элемента ИЛИ 50 получаем управляющий сигнал.

Управляющий сигнал на выходе 15.1 формируется следующим образом.

На входы обнуления триггеров 26-28 в начале первого периода тактовой частоты поступает сигнал с выхода элемента И 37. который устанавливает на выходах этих триггеров нулевое значение. Импульсами тактовой частоты, поступающими с выхода

5

0

5

15

15.2 на тактовый вход триггера 26, на выходах 15.1 триггеров 26 и 27, представляющих собой счетчик импульсов по модулю 4, формируются соответственно младший и старший разряды управляющего сигнала.

Управляющий сигнал на выходе 15.6 формируется следующим образом.

На первые и вторые входы мультиплексора 24 поступают сигналы соответственно с прямых и инверсных выходов счетчика, выполненного на триггерах 22 и 23. Управление мультиплексором 24 осуществляется с выхода триггера 28, на тактовый вход которого поступают сигналы с прямого выхода триггера 26. Выходы мультиплексора являются выходами 15.6 двух младших разрядов

управляющего сигнала. Инверсный выход триггера 26 является выходом 15.7 старшего разряда управляющего сигнала.

Элемент задержки на п тактов работает следующим образом (фиг. 9).

Данные, поступающие на вход триггера 52i, записываются по приходу фронта первого тактового сигнала на триггер 52i,. По приходу фронта второго тактового сигнала данные перезаписываются (с задержкой на один такт) в триггер 522 и т.д.

В известных решениях для реализации фильтра требуются большие аппаратурные затраты. Это затрудняет реализацию фильтра в виде интегральной схемы. В предлагаемом решении аппаратурные затраты на реализацию блока постоянной памяти уменьшены в 2 раза за счет учета при вычислениях симметрии коэффициентов импульсного отклика фильтра. Кроме того, с учетом широкого разброса значений коэффициентов конкретного импульсного отклика достигается дальнейшая экономия аппаратурных затрат на реализацию ПЗУ и уменьшение разрядности накапливающего сумматора.

Фильтр может использоваться для увеличения в 4 раза частоты дискретизации цифрового сигнала звукового диапазона в системах проигрывания компакт-дисков, цифровых магнитофонах и т.п.

Формула изобретения

Цифровой интерполяционный фильтр, содержащий группу регистров, выходы разрядов каждого предыдущего регистра группы соеди- нены с одноименными информационными входами разрядов каждого последующего регистра группы, программно-временной блок, первые, второй, третий и четвертые выходы которого соединены соответственно с одноименными адресными входами блока коммутации, тактовыми входами первого, второго регистров и одноименными управляющими входами третьего регистра,

1728962

16

выходы блока коммутации соединены с одноименными информационными входами первого регистра, блок постоянной памяти, выходы которого соединены с одноименными информационными входами второго регистра, выходы которого соединены с одноименными первыми входами суммы сумматора, выходы разрядов суммы которого соединены с оноименными информационными входами разрядов третьего регистра, выходы разрядов которого являются информационными выходами фильтра, отличающийся тем, что, с целью уменьшения аппаратурных затрат на реализацию фильтра, в него введены четвертый, плтый регистры, триггеры и шина нулевого потенциала, информационные входы разрядов первого регистра группы являются информационными входами фильтра, выход младшего разряда и последовательный информационный вход каждого регистра груп- пы объединены соответственно и подключены к соответствующим информационным входам блока коммутации, тактовый вход программно-временного блока объединен с тактовыми входами регистров группы, третьего, четвертого и пятого регистров и является тактовым входом фильтра, вход Пуск программно-временного блока является входом Пуск фильтра, пятые, шестые, седьмой, восьмые, девятый и десятый выходы программно-временного блока соединены соответственно с одноименными управляющими входами регистров группы, одноименными первыми входами блока постоянной памяти, установочным входом второго регистра, одноименными управляющими входами четвертого регистра, тактовыми входами первого, второго триггеров и установочными входами первого, второго триггеров,третьего, четвертого и пятого регистров, выходы первого регистра соединены с одноименными вторыми входами блока постоянной памяти, вторые входы суммы сумматора подключены к выходам одноименных разрядов третьего регистра, выход младшего разряда которого соединен с информационным входом четвертого регистра, выходы которого являются 0 информационными выходами фильтра, информационный вход и выход первого триггера подключены соответственно к выходу старшего разряда суммы сумматора и последовательному информационному входу третьего регистра, выходы разрядов переноса сумматора соединены с одноименными информационными входами разрядов пятого регистра, кроме информационного входа младшего разряда, информационный вход младшего разряда пятого регистра

5

0

5

0

5

5

5

17

подключен к шине нулевого потенциала, информационный вход и выход второго триггера подключены соответственно к выходу старшего разряда переноса сумматора и последовательному информационному входу пятого регистра, выходы которого соедине

18

ны с одноименными входами переноса сумматора, управляющие входы пятого регистра подключены к одноименным четвертым выходам программно-временной: блока, одиннадцатый выход которого явля ется управляющим выходом фильтра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции | 1985 |

|

SU1280614A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1292006A1 |

| Цифровой фильтр | 1987 |

|

SU1474676A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

| Цифровой рекурсивный фильтр | 1985 |

|

SU1328925A1 |

| Многоканальный цифровой коррелятор | 1985 |

|

SU1397938A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Устройство для вычисления коэффициентов цифрового фильтра | 1980 |

|

SU961103A1 |

Изобретение относится к информационно-измерительной технике, и обработке сиг- налов и может использоваться при увеличении частоты дискретизации цифровой последовательности. Изобретение позволяет уменьшить аппаратурные затраты на реализацию фильтра за счет снижения емкости блока постоянной памяти. Устройство содержит регистры, блок коммутации, блок постоянной памяти, сумматор, триггеры программно-временной блок, информационный, тактовый входы, вход Пуск и информационные выходы. 9 ил.

Примечание.

Количество отсчетов импульсной характеристики фильтра 96; максимальная ошибка в полосе задерживания дБ; максимальная ошибка в полосе пропускания +0,3 дв; коэффициент масштабирования, при котором характеристи ка не отклоняется от заданных пределов .

И #

6 19

Фие.З

T21 T22

Ш И25

Зад .38 TW №Z

Л/т

P.CTVi

3ad.W 15,11

TtS 75.70

3ad39

i

I

I--I

ngrur-TjTi«na

5ГП(2.(7

n

Фиг. 7

| Цифровой трансверсальный фильтр | 1982 |

|

SU1045384A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1429294A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-23—Публикация

1990-04-02—Подача