I

Изобретение относится к радиотехнике и может использоваться в системах автоматическсго регулирования и управления.

Одним из известных устройств воспроизведения частоты является синтезатор частот, в которо.м частота входного сигнала формируется путем улравляе.мого суммирования различных частот, снимаемых с делителя частоты, причем управление производится в соответствии с кодом, записанным в управляющем регистре .

Однако в известном синтезаторе частот невозможно воспроизводить частоты в широких пределах без изменения частоты источника опорного сигнала, а также невозможно обеспечить точное соответствие частоты сигнала на выходе коду, записанному в управляющий регистр.

Наиболее близким техническим рещением является устройство воспроизведения частоты входного сигнала, содержащее две цепи: первую - входную и вторую - выходную, каждая из которых выполнена в виде последовательно включенных блока зправления, элемента И, счетчика и преобразователя код- частота; а также источник опорной частоты, подключенный к соответствующему входу каждого из преобразователей код-частота и к одпому из входов третьего и четвертого элементов И, вторые входы которых соединены

соответственно с Первым и вторым выходами первого блока управления, а выходы - с третьим входом четвертого элемента И через последовательно включенные реверсивный

счетчик, дешифратор пуля и блок запрета; второй вход первого элемента И является сигнальным входом устройства, второй и третий выходы каждого блока з-правленпя соединены с управляющими входами соответствующего преобразователя код-частота, а входы второго блока управления подключены соответственно к второму выходу первого блока управления и к выходу дещифратора нуля 2.

Однако в этом устройстве невозможно обеспечить точное воспроизведепие частоты входного сигнала, записанной в виде кода в счетчик. Целью изобретения является повышение

точности воспроизведеппя.

Для этого в устройстве воспропзведения частоты входного сигнала, содержащем две цепи: первую - входную и вторую - выходную, каждая из которых выполнена в виде

последовательно включенных блока управления, элемента И, счетчика и преобразователя код-частота; а также источник опорной частоты, подключенный к соответствующему входу каждого из преобразователей код-частота и к одно.му из входов третьего и четвер3

того элементов И, вторые входы которых соединены соответственно с первым и вторым выходами первого блока управления, а выходы - с третьим входом четвертого элемента И через последовательно включенные реверсивный счетчик, дешифратор нуля и блока запрета; второй вход первого элемента И является сигнальным входом устройства, второй и третий выходы каждого блока управления соединены с управляющими входами соответствующего преобразователя код-частота, а входы второго блока управления подключены соответственно к второму выходу первого блока управления и к выходу дешифратора нуля, в каждую из цепей введен умножитель частоты, один вход которого соединен с выходом преобразователя код-частота, другой вход - с источником опорного напряжения, установочные входы соединены с выходами старших разрядов счетчиков, а унравляющие входы умножителей соединены с управляющими входами преобразователя кодчастота, при этом выход первого умножителя частоты соединен со вторым входом второго элемента И, а выход второго умножителя частоты является выходом устройства.

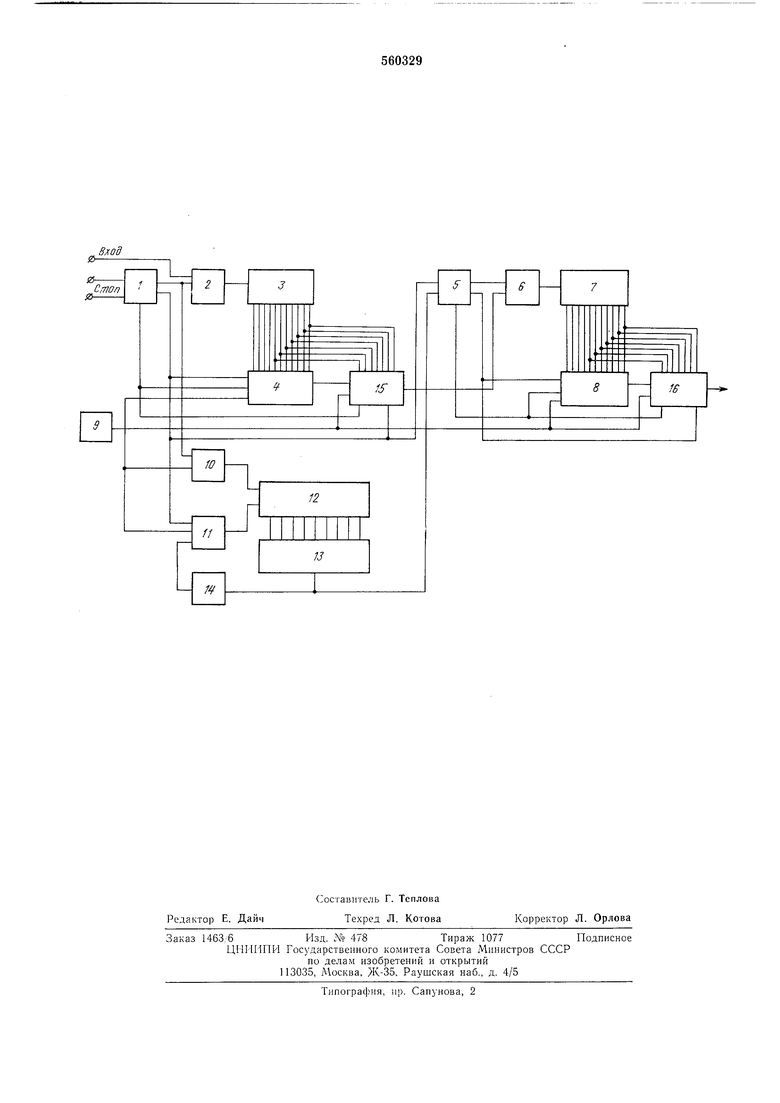

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство воспроизведения частоты входного сигнала содержит две цепи: первую - входную и вторую - выходную. Входная цепь выполнена в виде последовательно включенных блока управления 1, элемента И 2, счетчика 3 и ;Г1реобразователя 4 код-частота. Выходная цепь также выполнена в виде последовательно включенных блока управления 5, элемента И 6, счетчика 7 и преобразователя 8 код-частота. Устройство содержит также источник 9 опорной частоты, подключенный к соответствующему входу каждого из преобразователей 4 и 8 и к одному из входов третьего и четвертого элементов И 10, 11, вто(рые входы которых соединены соответственно с первым и вторым выходами первого блока управления 1, а выходы - с третьим входом четвертого элемента И 11 через последовательно включенные .реверсивный счетчик 12, дешифратор 13 нуля и блок запрета 14, при этом второй вход первого элемента И 2 является сигнальным входом устройства, а второй и третий выходы каждого блока управления 1, 5 соединены с управляющими входами соответствующего преобразователя 4, 8, а входы второго блока управления 5 подключены соответственно к второму -выходу первого блока управления 1 и к выходу дешифратора 13. Каждая из цепей содержит умножители 15, 16 частоты соответственно. Один вход каждого умножителя 15,16 соединен с выходами преобразователей 4, 8 соответственно, другой вход - с источником 9, установочные входы соединены с выходами старших разрядов счетчиков 3, 7, а управляющие входы умножителей 15, 16 соединены с управляющими входами преобразователей 4, 8, при этом

4

выход первого умножителя 15 соединен с вторым входом второго элемента И 6, а выход второго умножителя 16 является выходом устройства.

Устройство работает следующим образом. Перед началом работы все счетчики 3, 7, 12, преобразователи 4, 8 и умножители 15, 16 устанавливаются в исходное Положение, при этом с первого и второго выходов блока управления 1 па элементы И 2, 10, 11 поступает сигнал, запрещающий прохождение входного сигнала через элемент И 2 и сигнала источника 9 олорной частоты через элементы И 10 и 11. Одновременно с дещифратора 13 сигнал ноступает на блок управления 5, с первого выхода которого подается сигнал запрета на элемент И 6. По внешней команде «Пуск, подаваемой на один из входов блока управления 1, с последнего выдается потенциальный сигнал, осуществляющий открытие элементов И 2 и 10, ори этом через элемент И 2 входной сигнал частоты FQ поступает на счетчик 3, а через элемент И 10 оиорный сигнал частоты FoTt - на вход обратного счета реверсивного счетчика 12.

При достижении на счетчике 3 числа Ло значение которого определяется заданной погрешностью от дискретности, на другой вход блока управления 1 подается

сигнал «Стоп. С блока 1 на элементы И 2 и 10 поступает сигнал запрета, прекращается счет иМПульсов входной частоты счетчиком 3 и опорной частоты реверсивным счетчиком 12, при этом на счетике 3 будет зафиксировано число Ло, а на реверсивном счетчике 12 число -

рл/ - рр .т

т - ОП- ИЗМ1

где Р - емкость реверсивного счетчика 13; - число отсчитанных периодов;

Ткзм - время между командами «Пуск и

«Стоп.

Одновременно с подачей запрещающего сигнала на элементы И 2 и 10 с третьего выхода блока управления 1 выдается импульсный сигнал на входы установки кода преобразователя 4 и умножителя 13, при этом в преобразователь 4 запишется число , а в ум1 г-NO NI

нол итель 1о - число

где Ло - число, зафиксированное на счетчике 3; NI - число, зафиксированное младшими

газрядами счетчика 3;

«1 - число младших разрядов счетчика 3.

В момент окончания импульсного сигнала с

третьего выхода блока управления 1 с его

второго выхода выдается нотенциальный сигнал разрешения, поступающий одновременно

на управляющий вход нреобразователя 4, на

второй вход элемента И 11, на первый вход

блока управления 5 и на управляющий вход

умножителя 15. При этом на преобразователь

4, умножитель 15 и на пря.мой вход реверсивного счетчика 12 начинают поступать импуль:;ы опорной частоты. Преобразователь 4 циклически преобразует код числа Ло в частоту „ оп„„ Гх, равную тг . Сигнал частоты Гх с выхо- о да преобразователя 4 поступает на один из входов умножителя 15, который осуществляет дискретное умножение частоты fx, и с его выхода на второй вход элемента И 6 поступает сигнал частоты умш а на пер;вый вход - сигнал разрешения с выхода блока управления 2. Импульсы частотой Гумн за писываются в счетчике 7 в течение времени Гнзм, определяемого прямым счетом опорной частоты реверсивным счетчиком 12 до нулевого состояния, с дешифратора 13 сигнал через блок запрета 14 подается на третий вход элемента И 11 п на вт-орой вход блока управления 5, Ирн этом прекращается счет импульсов счетчиком 7 и реверсивным счетчиком 12. Сигнал с выхода дешифратора 13 для блока управления 2 дредстявляет собой сигнал «Стоп, при котором с его второго выхода импульсный сигнал поступает на управляющие входы установки Преобразователя 8 и умпожителя 16, при этом ,в преобразователь 8 запишется число Л . 3 В умножитель 16 - число N,-c - где NX - число, зафиксированное в счетчике 7; NI - число, зафиксированное младшими разрядами счетчика 7; п-2 П - число младших разрядов счетчика 7. В дальнейшем процесс иреобразования кода в частоту преобразовагелим 8 и умножение его выходной частоты умножителе.м 16 аналогичны преобразованию кода в частоту и умножение этой частоты преобразователем 4 11 ум}1ож1Пеле, 5, при этом с выхода умножителя 16 снимается сигнал частотой FQ. Таким образом, введение умиожителей частоты, функционально связанных с счетчиками входной частоты и преобразователями код-частота, позволяет обеспечить соответствие воспроизюдимои выходной частоты входной, заиисаино в виде кода, с высокой ШЧНОСТЬЮ. Формула изобретения Устройство воспроизведения частоты входного сигнала, содержащее две цепи: первую- входную и вторую - выходную, каждая из которых выполнена в виде последовательно ы люченных блока управления, элемента И, счетчика и гфеобразователя код-частота; а также источник онорной частоты, подключенный к соответствующему входу каждого из преобразователей код-частота и к одному из входов третьего и четвертого элементов И, вторые входы которых соединены соответственно с первым и вторым выходами иервого блока управления, а выходы - с третьим входом четвертого элемента И через последовательно включенные реверсивный счетчик, дешифратор нуля и блок запрета; второй вход первого элемента И является сигнальным входом устройства, второй и третий выходы каждого блока управления соединены с управляющими входами соответствующего преобразователя код-частота, а входы второго блока уиравления подключены соответственно к второму выходу первого блока управления и к выходу дешифратора нуля, отличающееся тем, что, с целью повышения точное 111 воспроизведения, в каждую из цеией введен умножитель частоты, один .вход которого соединен с выходом преобразователя код-частота, другой вход - с н-сточником опорного напряжения, установочные входы соединены с выходами сгаршпх разрядов счетчпков, а управляющне входы умножителей соединены с управляющими входами преобразователя код-частота, при этом выход иервого умиож 1теля частоты соединен с вторым входо.м второго элемента И, а выход второго умножителя частоты является выходом устройства. Источники инфор.мации, принятые во внимание при экспертизе изобретения 1.Патент США Л 3671871, кл. 328-25, 1972. 2.Патент США № 3753125, кл. 328-38, 1973 (прототпп).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство воспроизведения частоты входного сигнала | 1975 |

|

SU572918A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для управления процессом смешения жидких продуктов | 1985 |

|

SU1272314A1 |

| Устройство для отображения векторов, окружностей и дуг на экране электронно-лучевой трубки | 1981 |

|

SU1032475A1 |

| Устройство для обработки и ввода экспериментальный данных в вичислительную машину | 1975 |

|

SU541162A1 |

| РЕЛЕ ЧАСТОТЫ | 2002 |

|

RU2208865C1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1272507A1 |

| Устройство для автоматической проверки аналого-цифровых преобразователей | 1978 |

|

SU782144A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

Авторы

Даты

1977-05-30—Публикация

1973-12-25—Подача