ния сигнала запрета подключен к выходу D блока сравнения, а информационный вход блока формирования сигналов запрета соединен с выходом реверсивного счетчика и одним входом вычитающего блока, другой вход которого подключен к выходу суммирующего счетчика, а выход вычитающего блока соединен с входом регистра, выход которого подключен к входу корректирующего блока и второму входу сумматора, входы С регистра и корректирующего блока объединены с вторым входом блока задания режима работы и подключены к пятому выходу преобразователя код- частота, знаковый выход корректирующего блока соединен с первым входом блока задания режима работы, выход сумматора соединен с первым входом блока формирования кода управления, другими входами подключенного к соответствующим выходам блока за- дания режимов работы, выход блока формирования кода управления подключен к входу цифроаналогового преобразователя, выход которого является выходом устройства.

Блок сравнения содержит компаратор, дифференциатор, входом подключенный к прямому входу компаратора, пороговый элемент, схему ИСКЛЮЧАЮЩЕЕ ИЛИ, один из входов которой соединен с выходом компаратора, а другой через пороговый элемент подключен к выходу дифференциатора, и две схемы синхронизации, одна из которых соединена с выходом схемы ИСКЛЮЧАЮЩЕЕ ИЛИ. а другая - с выходом порогового элемента, инвертирующий вход компаратора является третьим входом блока, прямой вход компаратора - первым входом блока, объединенные входы схем синхронизации являются вторым входом блока, выходы первой схемы синхронизации - соответственно инверсным и прямым выходами блока сравнения, а выход второй схемы синхронизации - выходом D блока.

Блок формирования сигналов запрета содержит два элемента НЕ, один из которых подключен к первому входу первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, а другой - к второму входу первой схемы И-НЕ, вторую схему И-НЕ. выход которой через третий элемент НЕ соединен со входом С D-триггера, а вход - с входами второго элемента НЕ и первой схемы И. подключенной к входу R D-триггера. вторую схему ИСКЛ ЮЧАЮЩЕ Е ИЛИ, присоединенную к первому входу второй схемы И-НЕ, и вторую схему И, один из входов которой через четвертый элемент НЕ подключен к выходу первой схемы И- НЕ, а другой - к инвертирующему выходу D-триггера, при этом первый вход первой

схемы И-НЕ подключен к выходу первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, вторым входом соединенной с вторым входом второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход

второй схемы И-НЕ подключен к выходу второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, а второй вход первой схемы И соединен с выходом первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ. вход D триггера подключен к шине логиче0 ской единицы, вход первого элемента НЕ является входом блока, второй вход второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ и вход второго элемента НЕ являются информационными входами блока, а выходы первой схемы

5 И-НЕ, второй схемы И-НЕ, третьего элемента НЕ и второй схемы И являются выходами блока.

Вычитающий блок содержит N элементов НЕ, выходы которых подключены к вхо0 дам А первого сумматора, и второй сумматор, входами А соединенный с выходами первого сумматора, при этом вход В1 младшего разряда второго сумматора подключен к выходу элемента НЕ, вход которо5 го соединен с выходом старшего знакового разряда QN первого сумматора, вход BN старшего разряда второго сумматора подключен к шине логического нуля, а остальные входы В второго сумматора и вход

0 переноса первого сумматора соединены с шиной логической единицы, входы В первого сумматора являются первыми входами блока, входы элементов НЕ - вторыми входами блока, а выход второго сумматора яв5 ляется выходом блока.

Блок задания режима работы содержит элемент НЕ, через первую схему И подключенный к тактовому входу первого счетчика и непосредственно к входу сброса второго

0 счетчика, вторую схему И, один из входов которой соединен с входом элемента НЕ и входом сброса первого счетчика, а выход подключен к тактовому входу второго счетчика, первый и второй триггеры, первый и

5 второй дешифратора, входы которых соединены с выходами соответственно первого и второго счетчиков, при этом первые выходы первого и второго дешифраторов подключены к входам R сброса соответственно первого и второго триггеров, а их вторые

0 выходы соединены с входами S установки соответственно второго и первого триггеров, вход элемента НЕ является первым входом блока, вход второй схемы И является вторым входом блока, а выходы первого и

5 второго триггеров являются первым и вторым выходами блока.

Введение новых элементов в указанной взаимосвязи, а также исключение двух постоянных запоминающих устройств, двух

делителей с переменным коэффициентом деления, импульсного частотно-фазового дискриминатора и блока начальной установки кода позволяют повысить быстродействие и точность устройства для стабилизации частоты вращения электродвигателя за счет уменьшения интервала То дискретности процесса измерения угловой ошибки Л а (интервал дискретности То имеет постоянную во всем диапазоне регулирования величину); поддержания постоянной величины коэффициента К преобразования угловой ошибки Лай коэффициента Кмпреоб- разования ошибки по скорости Л о , что приводит к поддержанию постоянной во всем диапазоне регулирования величины коэффи- циента усиления устройства для стабилизации частоты вращения электродвигателя.

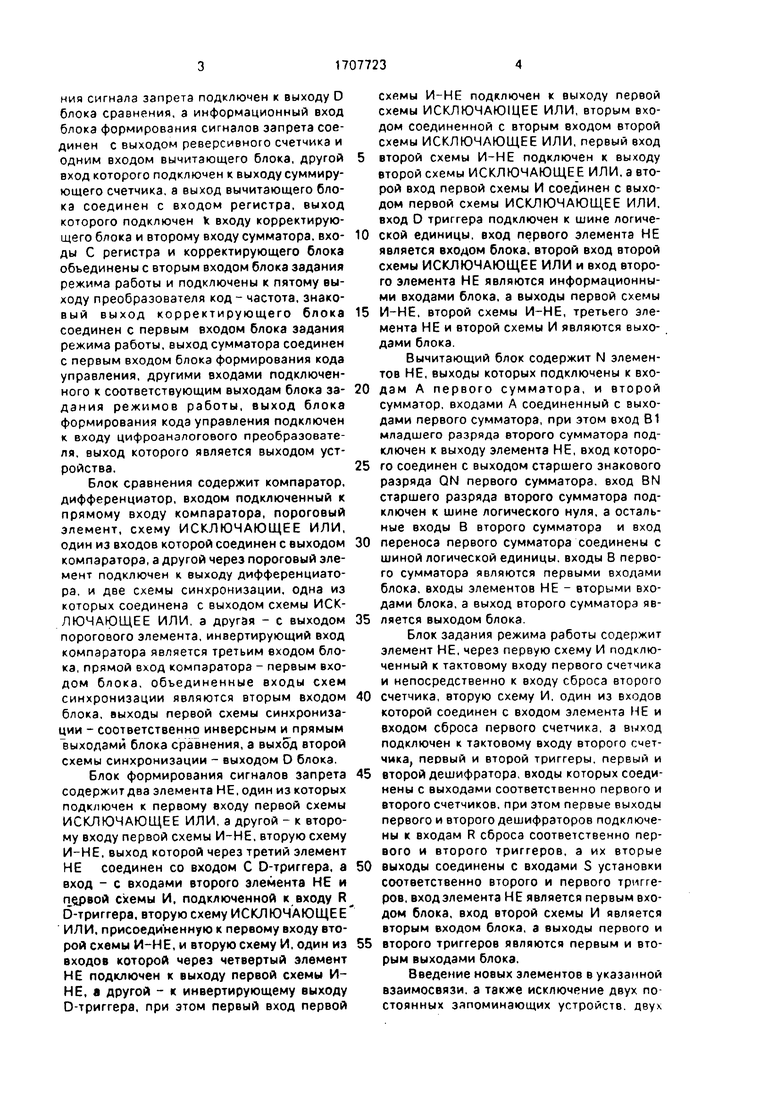

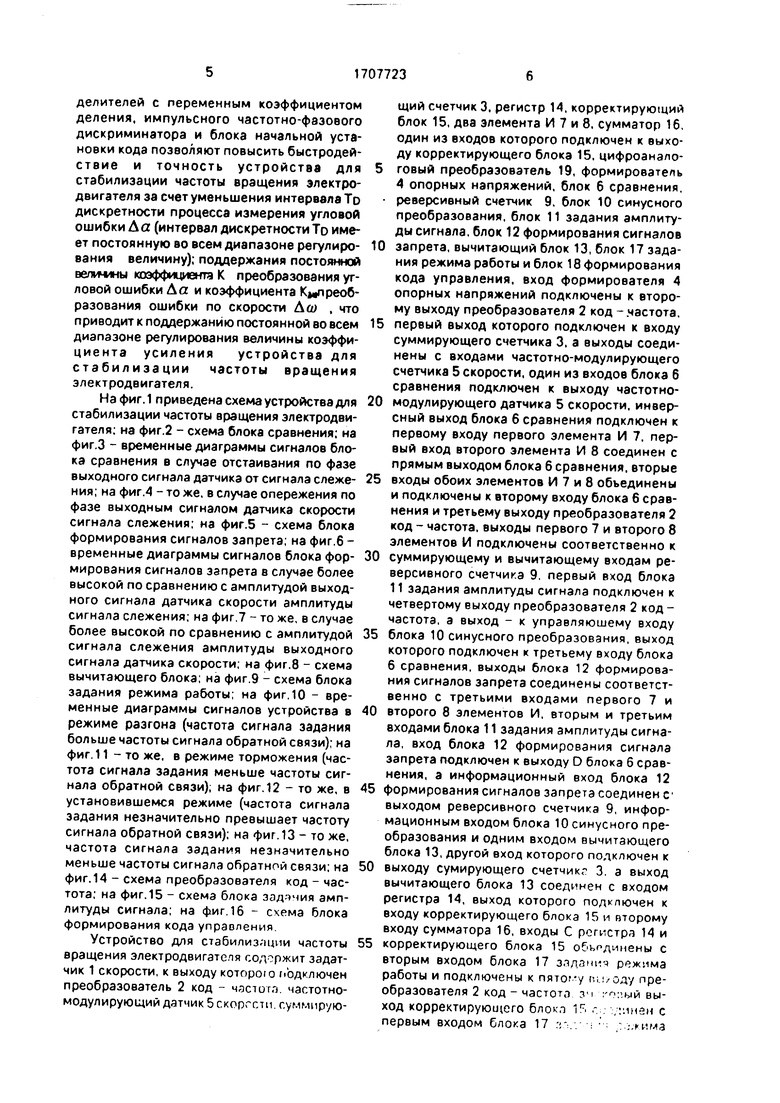

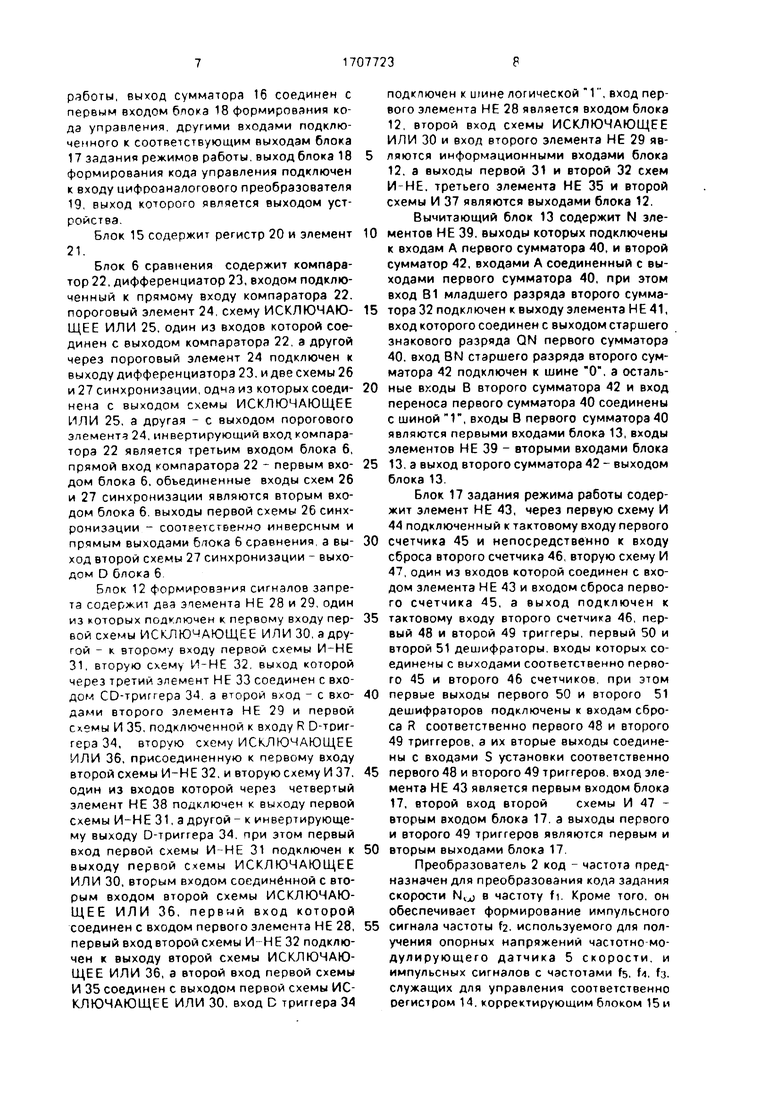

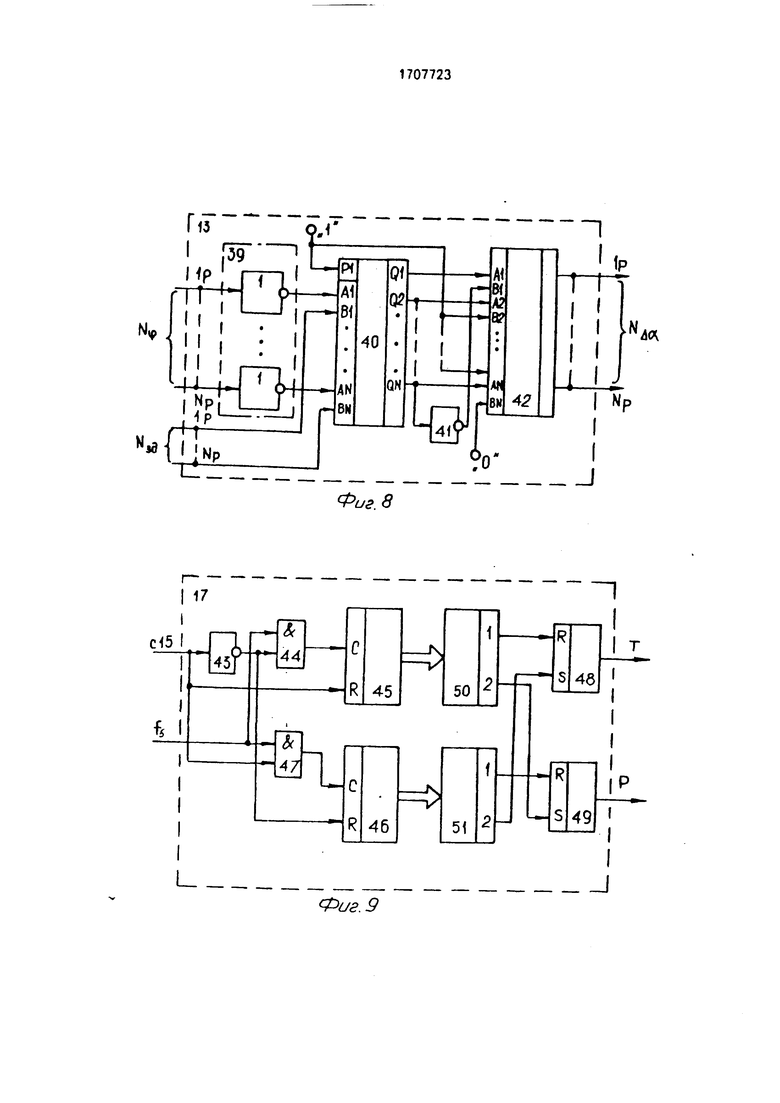

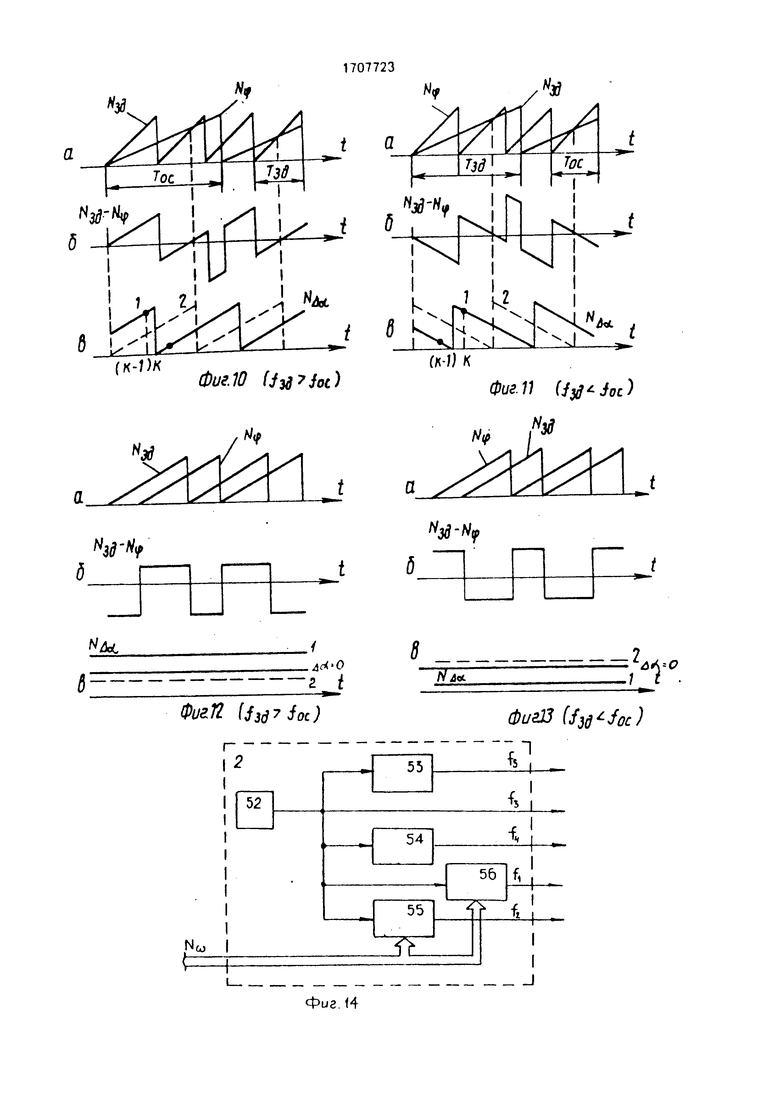

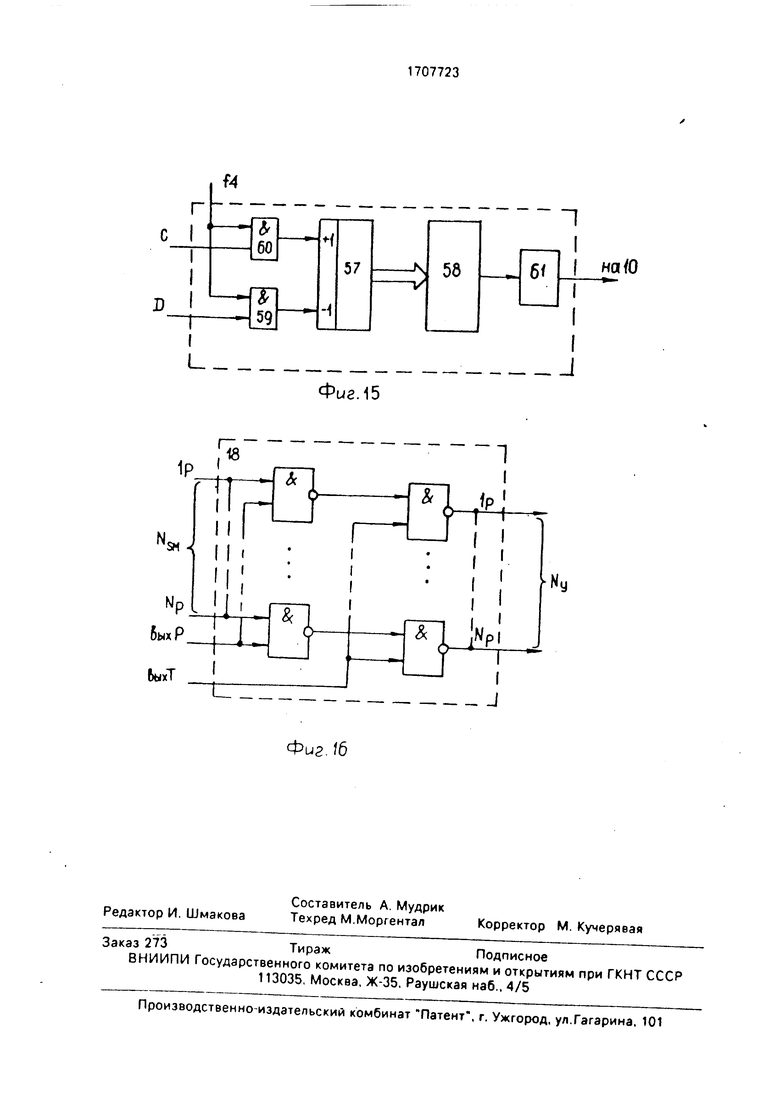

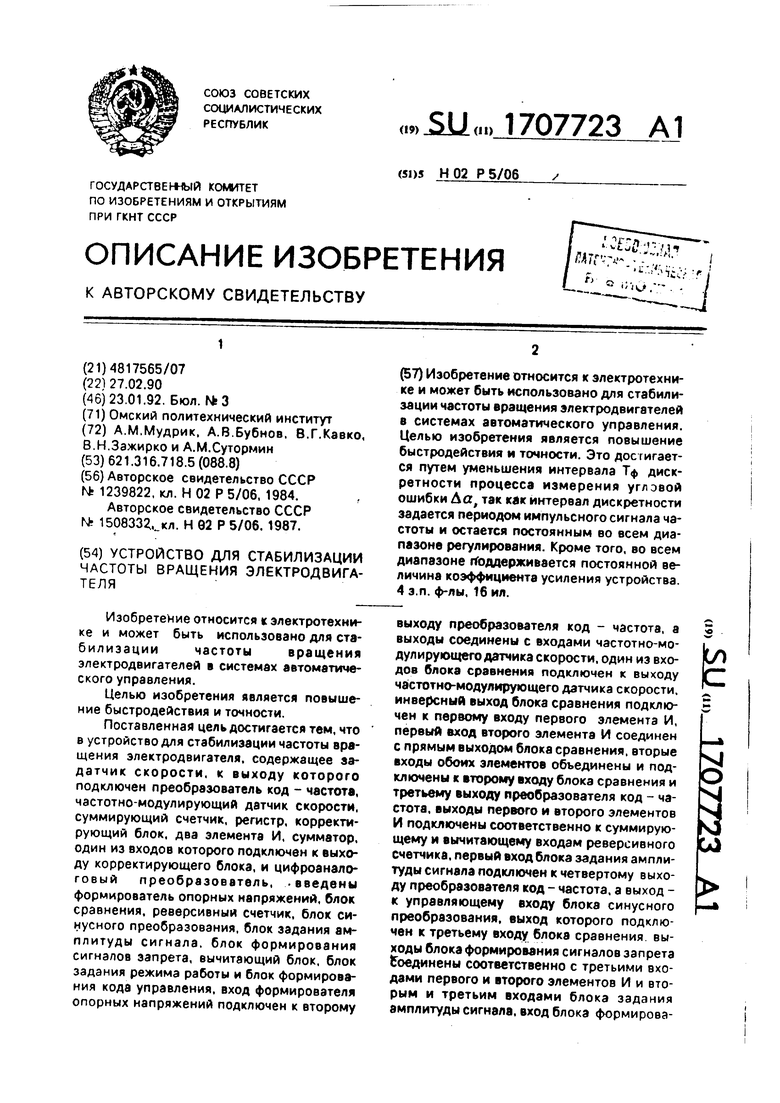

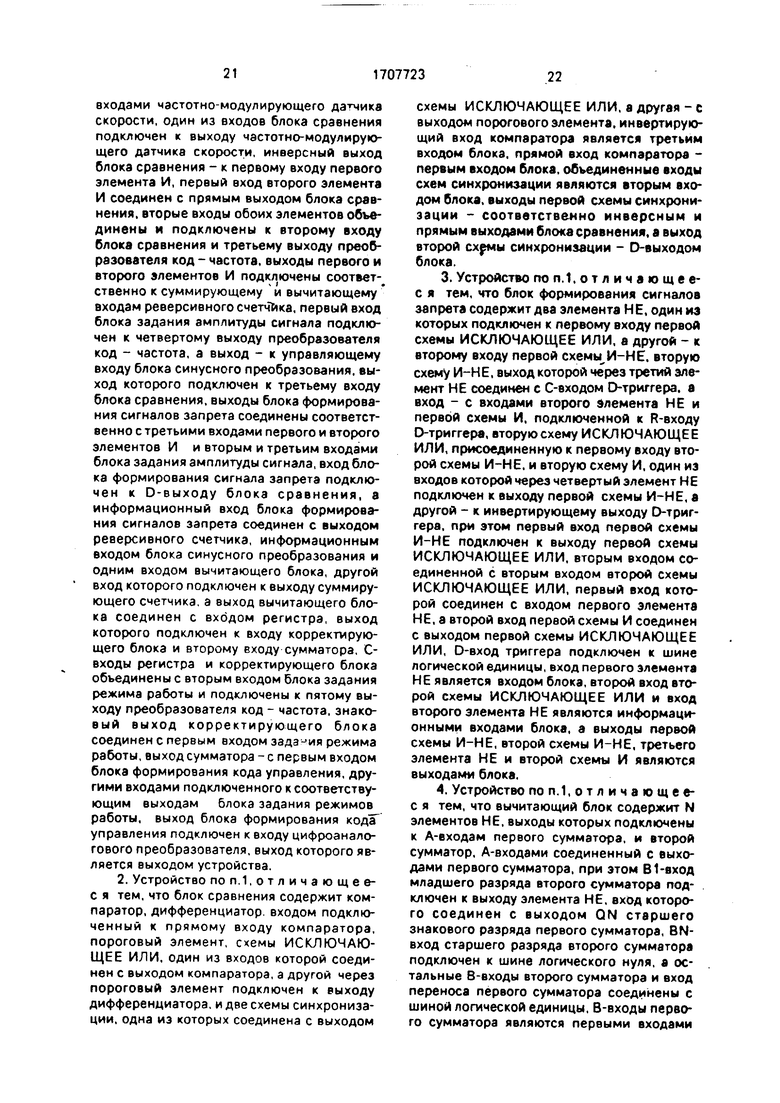

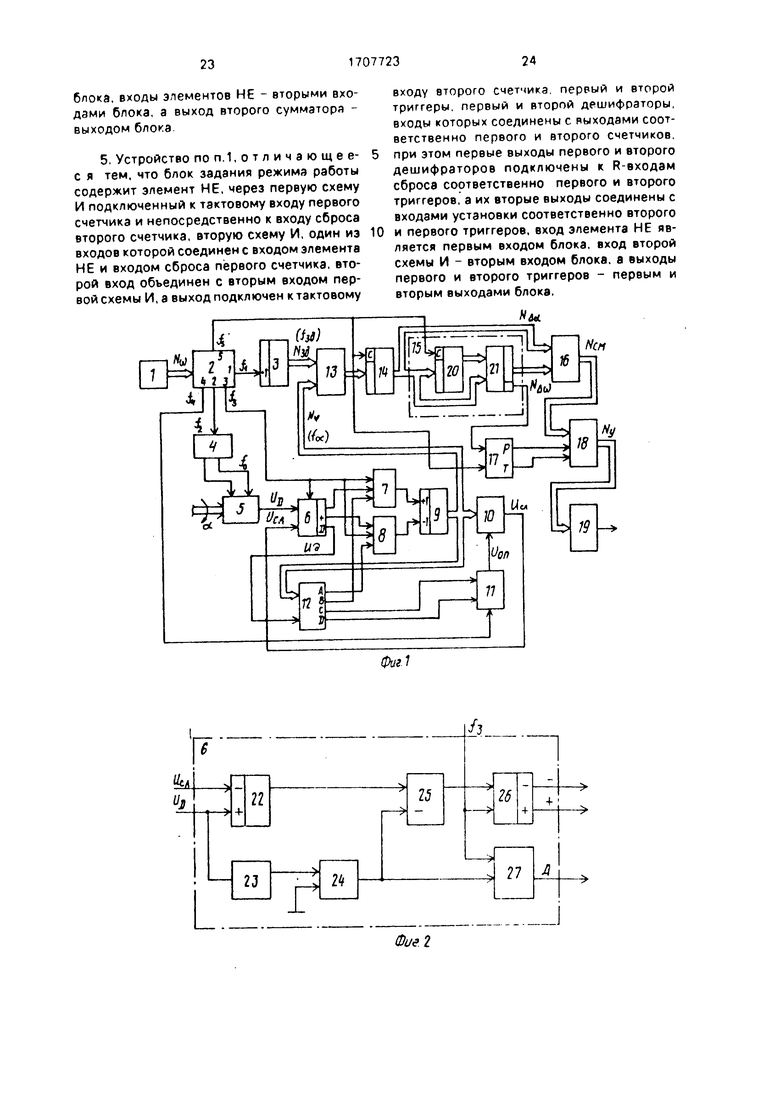

На фиг.1 приведена схема устройства для стабилизации частоты вращения электродвигателя: на фиг.2 - схема блока сравнения: на фиг.З - временные диаграммы сигналов блока сравнения в случае отстаивания по фазе выходного сигнала датчика от сигнала слежения; на фиг.4 - то же, в случае опережения по фазе выходным сигналом датчика скорости сигнала слежения; на фиг.5 - схема блока формирования сигналов запрета; на фиг.6 - временные диаграммы сигналов блока формирования сигналов запрета в случае более высокой по сравнению с амплитудой выходного сигнала датчика скорости амплитуды сигнала слежения; на фиг.7 - то же, в случае более высокой по сравнению с амплитудой сигнала слежения амплитуды выходного сигнала датчика скорости; на фиг.8 - схема вычитающего блока; на фиг.9 - схема блока задания режима работы; на фиг. 10 - временные диаграммы сигналов устройства в режиме разгона (частота сигнала задания больше частоты сигнала обратной связи); на фиг.11 - то же, в режиме торможения (частота сигнала задания меньше частоты сигнала обратной связи); на фиг. 12 - то же, в установившемся режиме (частота сигнала задания незначительно превышает частоту сигнала обратной связи); на фиг.13 - то же, частота сигнала задания незначительно меньше частоты сигнала обратной связи; на фиг. 14 - схема преобразователя код - частота; на фиг.15 - схема блока зад-тчия амплитуды сигнала; на фиг. 16 - схема блока формирования кода управления.

Устройство для стабилизации частоты вращения электродвигателя содержит задэт- чик 1 скорости, к выходу которою подключен преобразователь 2 код - частота, частотно- модулирующий датчик 5 скорости, суммирующий счетчик 3. регистр 14, корректирующий блок 15, два элемента И 7 и 8, сумматор 16, один из входов которого подключен к выходу корректирующего блока 15. цифроанало- говый преобразователь 19, формирователь 4 опорных напряжений, блок б сравнения, реверсивный счетчик 9. блок 10 синусного преобразования, блок 11 задания амплитуды сигнала, блок 12 формирования сигналов

0 запрета, вычитающий блок 13, блок 17 задания режима работы и блок 18 формирования кода управления, вход формирователя 4 опорных напряжений подключены к второму выходу преобразователя 2 код -частота,

5 первый выход которого подключен к входу суммирующего счетчика 3. а выходы соединены с входами частотно-модулирующего счетчика 5 скорости, один из входов блока б сравнения подключен к выходу частотно0 модулирующего датчика 5 скорости, инверсный выход блока 6 сравнения подключен к первому входу первого элемента И 7, первый вход второго элемента И 8 соединен с прямым выходом блока 6 сравнения, вторые

5 входы обоих элементов И 7 и 8 объединены и подключены к второму входу блока 6 сравнения и третьему выходу преобразователя 2 код - частота, выходы первого 7 и второго 8 элементов И подключены соответственно к

0 суммирующему и вычитающему входам реверсивного счетчика 9. первый вход блока 11 задания амплитуды сигнала подключен к четвертому выходу преобразователя 2 код- частота, а выход - к управляющему входу

5 блока 10 синусного преобразования, выход которого подключен к третьему входу блока 6 сравнения, выходы блока 12 формирования сигналов запрета соединены соответственно с третьими входами первого 7 и

0 второго 8 элементов И, вторым и третьим входами блока 11 задания амплитуды сигнала, вход блока 12 формирования сигнала запрета подключен к выходу D блока б сравнения, а информационный вход блока 12

5 формирования сигналов запрета соединен с1 выходом реверсивного счетчика 9, информационным входом блока 10 синусного преобразования и одним входом вычитающего блока 13, другой вход которого подключен к

0 выходу сумирующего счетчикг 3. а выход вычитающего блока 13 соединен с входом регистра 14, выход которого подключен к входу корректирующего блока 15 и второму входу сумматора 16, входы С регистра 14 и

5 корректирующего блока 15 обьодинены с вторым входом блока 17 задания режима работы и подключены к пятог-у rui/оду преобразователя 2 код - частота зч выход корректирующего блокл 1Г г . ;:ин5н с первым входом блока 17 ::v. : ; :.;,имз

работы, выход сумматора 16 соединен с первым входом блока 18 формирования кода управления, другими входами подключенного к соответствующим выходам блока 17 задания режимов работы, выход блока 18 формирования кода управления подключен к входу цифроанзлогового преобразователя 19, выход которого является выходом устройства.

Блок 15 содержит регистр 20 и элемент 21.

Блок 6 сравнения содержит компаратор 22, дифференциатор 23, входом подключенный к прямому входу компаратора 22. пороговый элемент 24, схему ИСКЛЮЧАЮЩЕЕ ИЛИ 25, один из входов которой соединен с выходом компаратора 22, а другой через пороговый элемент 24 подключен к выходу дифференциатора 23, идее схемы 26 и 27 синхронизации, одна из которых соединена с выходом схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 25, а другая - с выходом порогового элемент 24, инвертирующий вход компаратора 22 является третьим входом блока 6, прямой вход компаратора 22 - первым входом блока 6, объединенные входы схем 26 и 27 синхронизации являются вторым входом блока 6. выходы первой схемы 26 синхронизации - соответственно инверсным и прямым выходами блока 6 сравнения, а выход второй схемы 27 синхронизации - выходом D блока 6.

Блок 12 формирования сигналов запрета содержит два элемента НЕ 28 и 29, один из которых подключен к первому входу первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 30, а другой - к второму входу первой схемы И-НЕ 31. вторую схему И-НЕ 32, выход которой через третий элемент НЕ 33 соединен с входом CD-триггера 34. а второй вход - с входами второго элемента НЕ 29 и первой схемы И 35, подключенной к входу R D-триг- гера 34, вторую схему ИСКЛЮЧАЮЩЕЕ ИЛИ 36, присоединенную к первому входу второй схемы И-НЕ 32, и вторую схему И 37, один из входов которой через четвертый элемент НЕ 38 подключен к выходу первой схемы И-НЕ 31, а другой- к инвертирующему выходу D-триггера 34. при этом первый вход первой схемы И-НЕ 31 подключен к выходу первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 30, вторым входом соединённой с вторым входом второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 36, первмй вход которой соединен с входом первого элемента НЕ 28, первый вход второй схемы И-НЕ 32 подключен к выходу второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 36, а второй вход первой схемы И 35 соединен с выходом первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 30. вход D триггера 34

подключен к шине логической 1, вход первого элемента НЕ 28 является входом блока 12, второй вход схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 30 и вход второго элемента НЕ 29 являются информационными входами блока

12, а выходы первой 31 и второй 32 схем

И-НЕ. третьего элемента НЕ 35 и второй

схемы И 37 являются выходами блока 12.

Вычитающий блок 13 содержит N эле0 ментов НЕ 39. выходы которых подключены к входам А первого сумматора 40, и второй сумматор 42, входами А соединенный с выходами первого сумматора 40, при этом вход 81 младшего разряда второго сумма5 тора 32 подключен к выходу элемента НЕ 41, вход которого соединен с выходом старшего знакового разряда QN первого сумматора 40. вход BN старшего разряда второго сумматора 42 подключен к шине О, а осталь0 ные входы В второго сумматора 42 и вход переноса первого сумматора 40 соединены с шиной Г, входы В первого сумматора 40 являются первыми входами блока 13, входы элементов НЕ 39 - вторыми входами блока

5 13, а выход второго сумматора 42 - выходом блока 13.

Блок 17 задания режима работы содержит элемент НЕ 43, через первую схему И 44 подключенный к тактовому входу первого

0 счетчика 45 и непосредственно к входу сброса второго счетчика 46, вторую схему И 47, один из входов которой соединен с входом элемента НЕ 43 и входом сброса первого счетчика 45, а выход подключен к

5 тактовому входу второго счетчика 46, первый 48 и второй 49 триггеры, первый 50 и второй 51 дешифраторы, входы которых соединены с выходами соответственно первого 45 и второго 46 счетчиков, при этом

0 первые выходы первого 50 и второго 51 дешифраторов подключены к входам сброса R соответственно первого 48 и второго 49 триггеров, а их вторые выходы соединены с входами S установки соответственно

5 первого 48 и второго 49 триггеров, вход элемента НЕ 43 является первым входом блока 17, второй вход второй схемы И 47 - вторым входом блока 17. а выходы первого и второго 49 триггеров являются первым и

0 вторым выходами блока 17.

Преобразователь 2 код - частота предназначен для преобразования кода задания скорости Nij в частоту fi. Кроме того, он обеспечивает формирование импульсного

5 сигнала частоты f2. используемого для получения опорных напряжений частотно модулирующего датчика 5 скорости, и импульсных сигналов с частотами fs, л, тз. служащих для управления соответственно регистром 14. корректирующим блоком 15 и

блоком 17 задания режима работы, блоком 11 задания амплитуды сигнала, реверсивным счетчиком 9 и блоком б сравнения. Так как в электроприводах с частотно-модулирующими датчиками величина заданной час- тоты вращения

. Ьд fo f.,- --Ј--.

где Z - коэффициент электрической редукции датчика, определяется как величиной частоты (Зд задания, так и величиной частоты f0 опорного сигнала датчика, то изменение заданной частоты вращения можно производить как иэ- меняя частоту fi - f3flK3. где Кз - коэффициент пересчета (деления) суммирующего счетчика 3, так и путем изменения частоты f2 сигнала, служающего для формирования опорных напряжений частоты f датчика 5 скорости (f2 K4fo, где К - коэф- фициент деления формирования 4 опорных напряжений). При этом диапазон перестройки частоты f0, а следовательно, и диапазон перестройки частоты h должны выбираться исходя из характеристик конк- ретного датчика скорости, не приводя к ухудшению его работы. Частота fa должна выбираться из соотношения h 2 x(f0 + +2(2 л)1 оьрмакс. где N - число разрядов кода угловой ошибки; f0 - частота опорных напряжений датчика 5 скорости; спьрмакс - максимальная частота вращения; Z - коэффициент электрической редукции датчика. Значение частоты f$ определяется необходимым быстродействием контура автопод- стройки амплитуды. Частота fs задает дискретность процесса измерения угловой ошибки и ошибки по скорости. Ее величину целесообразно задать равной максимальной частоте fi импульсного сигнала, посту- лающего на вход суммирующего счетчика 3 с первого выхода преобразователя 2 код - частота и определяющего величину частоты f3A сигнала задания (f 1 СэдКз). В этом случае в верхней части диапазона регулирования интервал дискретности То в Кэ раз меньше Т3д - периода сигнала задания, а в нижней части диапазона - в ТпКз/Т3дмин раз (ТЗДМИн

- fsAMaicc 1, То fo Тздмакс ПврИОД

опорных напряжений датчика 5.

Преобразователь 2 код - частота может быть выполнен, например, следующим образом (фиг. 14); генератор 52 импульсов подключен к входам двух делителей 53 и 54 частоты и к входам двух делителей 55 и 56 с переменным коэффициентом деления. На управляющие входы делителей 55 с переменным коэффициентом деления подают код N .задания скорости.

В качестве частотно-модулирующего датчика 5 скорости может быть использован либо фазовый растровый интерполятор либо индукционный фазовращатель.

Блок 11 задания амплитуды сигнала осуществляет выравнивание амплитуды Uc« сигнала слежения и амплитуды UD выходного сигнала датчика 5 скорости. Для этого в блоке 11 формируют напряжение, являющееся опорным U0n для блока 10 синусного преобразования (в случае использования в блоке 10 цифроаналогового преобразователя это напряжение подают на опорный UREF вход ЦАП). Уменьшение или увеличение Uon происходит по внешним сигналам управления, поступающим с блока 12 формирования сигналов запрета. Приход импульсов с выхода О блока 12 (фиг,6 з) вызывает уменьшение амплитуды (Jen сигнала слежения, которое происходит за время, равное длительности приходящего импульса, а импульс с выхода С блока 12 (фиг. 7и) приводит к росту амплитуды L/сл сигнала слежения, также осуществляемому за время, равное длительности импульса. Блок 11 задания амплитуды сигнала может быть выполнен, например, на реверсивном счетчике 57 и цифроаналоговом преобразователе 58 (фиг. 16), на цифровой вход которого подан выходной код счетчика 57. В этом случае импульс с выхода D блока 12 разрешает прохождение на вход -1 счетчика 57 через элемент И 59 импульсов частоты fy, а импульс с выхода С разрешает прохождение через элемент И 60 импульсов частоты U на вход +1 счетчика 57. Цифроаналоговый преобразователь 58 выполняют по схеме двухквадрантного перемножителя, после чего его сигнал дополнительно инвертируют (например, при помощи операционного усилителя 61).

Блок 18 формирования кода управления предназначен для окончательного формирования кода Ny управления: единицы по всех разрядах кода при поступлении логической Г с выхода Р (на выходе Т О), нули во всех разрядах кода при поступлении логической 1 с выхода Т (на выходе Р О); код, равный выходному коду сумматора 16 при логической 1 на выходах Р и Т блока 17. Блок 18 формирования кода управления может быть выполнен, например, на схемах 2И-НЕ(фиг.18).

Устройство для стабилизации частоты вращения электродвигателя работает следующим образом.

На вход преобразователя 2 код - частота от задатчика 1 скорости поступает код М.„. пропорциональный заданной частоте вращения электродвигателя. Преобразователь

2 преобразует код N в два импульсных сигнала, следующих с частотой h и h. Сигнал с второго выхода преобразователя 2 код - частота (частоты f2) поступает на вход формирователя 4 (опорных напряжений, где преобразуется в синусоидальные напряжения частоты f0 (опорные сигналы), числр которых определяется числом фаз частотно- модулирующего датчика 5 скорости (при двухфазном датчике в формирователе 4 формируют два сдвинутых по фазе на 90° синусоидальных напряжений UmSln(f02 ят) и Umcos(f02 л t). С выхода частотно-модулирующего датчика 5 скорости снимают синусоидальный сигнал UD Uosjn(oAD t + Z о) частоты f0c fo + Z Шцр(2 л)1 (где омр - частота вращения), начальная фаза которого пропорциональна углу поворота вала двигателя а. Так как частота выходного сигнала датчика 5 определяется суммой двух составляющих f0 и . то даже при нулевой частоте вращения с выхода датчика снимается синусоидальный сигнал частоты fo( о)ор 0). С выхода частотно-модулирующего датчика 5 скорости сигнал Do поступает на один из входов блока б сравнения, в котором сигнал UD сравнивают по фазе с форми- руемым на входе блока 10 синусного преобразователя сигналом Уел слежения. Причем такое сравнение осуществляется на протяжении всего периода сигналов (в точках 1-1 ,2-2 ,.... л-n , фиг.4э). Если выходной сигнал UD датчика 5 скорости отстает по фазе (фиг. За) от сигнала слежения, то на неинверсном (+) выходе блока 6 сравнения устанавливается сигнал 1 (на инверсном (-) выходе сигнал О). При опережении по фазе выходным сигналом датчика 5 скорости сигнала 11Сл слежения (фиг.4а)сигнал 1 формируется на инверсном (-) выходе блока 6 сравнения (на неинверсном () выходе сигнал О). Причем импульсы на выходах блока сравнения синхронны с импульсами частоты тз, снимаемыми с третьего выхода преобразователя 2 код - частота 2. Приход импульса (1) с неинверсного (+) выхода блока 6 сравнения разрешает прохождение через элемент 8 импульсов частоты fs на вычитающий -1 вход реверсивного счетчика 9 (при условии отсутствия сигнала запрета на выходе А блока 12 формирователя сигнала запрета). Уменьшение выходного кода N реверсивного счетчика 9 приводит к соответствующему фазовому сдвигу синусоидального сигнала Уел слежения, формируемому на выходе блока 10 синусного преобразования (фаза сигнала исл слежения уменьшается), в результате чего устраняется отставание по фазе выходного сигнала датчика 5 скорости от сигнала Усл.

слежения. Аналогично происходит и в случае прихода импульса с инверсного (-) выхода блока б сравнения. Данный импульс открывает элемент 7 (при отсутствии сигнала запрета на выходе В блока 12) и разрешает прохождение импульсного сигнала частоты Ь на суммирующий +Г вход реверсивного счетчика 9. Выходной код N счетчика 9 увеличивается, вызывая изменение в

блоке 10 синусного преобразования фазы сигнала слежения УСл (фаза сигнала Уел увеличивается) и устраняя тем самым опережение по фазе выходным сигналом UD частотно-модулирующего датчика 5 скорости сигнала слежения (фиг. 4а). Таким образом осуществляется слежение сигнала Уел, формируемого на выходе блока 10 синусного преобразования, за выходным сигналом UD частотно-модулирующего датчика 5 скорости. В случае, когда амплитуда UD выходного сигнала датчика 5 не равна по величине амплитуде УСл сигнала слежения, на выходе блока 11 задания амплитуды сигнала формируют напряжение U0n. поступающее на

управляющий вход блока 10 синусного преобразования. В соответствии с выходными сигналами (выходы С, D) блока 12 формирования сигналов запрета, являющимися управляющими для блока 10 задания

амплитуды сигнала, напряжение Don либо уменьшается (исл UD). либо увеличивается (Уел Уо), вызывая аналогичные изменения амплитуды Уел сигнала УСя слежения. Такая подстройка амплитуды УСл сигнала слежения является необходимой, так как в противном случае сигнал не отслеживает изменения выходного сигнала Уо частотно- модулирующего датчика 5 скорости.

В связи с тем. что сигнал УСл слежения

полностью отслеживает изменения выходного сигнала UD датчика 5 скорости, выходной код N реверсивного счетчика 9, снятый в любой момент времени и эквивалентный фазе (р сигнала Усл. соответствует и фазе

о 0)о + Z а, где Шо - частота опорных напряжений; Z - коэффициент электрической редукции выходного сигнала UD датчика 5.

С выхода реверсивного счетчика 9 код

поступает на один из входов считающего блока 13. на другой вход которого с выхода суммирующего счетчика 3 подают код N3A, формируемый из импульсного сигнала частоты fi, снимаемого с первого выхода преобразователя 2. Выходной код МЭд счетчика 3 эквивалентен фазе р3д Wot f Za . где сгзд - заданный угол поворота вала двигателя, сигнала задания f3fl. На выходе вычитающего блока 13 в установившемся

режиме (синхронизации), когда производится отработка фазового рассогласования сигналов 13& задания и обратной связи f0c (фиг. 12 и 13) получают код 4u N3« - Ny К ((tk, t - Wo t -f Z азд - Z а) К Z Да (К - коэффициент пропорциональности), пропорциональный угловой ошибке Асг (фазовому рассогласованию сигналов задания и обратной связи). В моменты времени, соответствующие приходу импульсов частоты fs с пятого выхода преобразователя 2 код - частота, выходной код Мдх вычитающего блока 13 проходит через регистр 14 и поступает на вход корректирующего блока 15. Так как частота fs есть величина постоянная, а код выходе вычитающего блока формируется практически непрерывно (с интервалом, определяемым дискретизацией по времени, задаваемой частотой fa), то интервал дискретности процесса измерения угловой ошибки Да остается постоянным во всем диапазоне регулирования. Величина коэффициента преобразования угловой ошибки КА(, определяемого из выражения для кода угловой ошибки Zf3AK3

м - А°

Ч.-zr

Да

Z2

N

эд

Да

ZK Да

Да

2 я 1Х 2л где Д - цена единицы младшего разряда угловой ошибки; f3A - частота сигнала задания: Z - коэффициент электрической редукции датчика 5: Кз - коэффициент пересчета счетчика 3.

как КдЈ 2 , зависит только от числа разрядов N кода М угловой ошибки, соответствующего числу разрядов N счетчиков 3 и 9. и также не изменяется во всем диапазоне регулирования.

В корректирующем блоке 15 по К-му и (К-1)-му отсчетам кода М угловой ошибки формируют К-й отсчет кода М-(К) - ) - -N (К - 1) ошибки по скорости, вводя, таким образом, дифференциальную составляющую в закон управления. Так как интервал дискретности TD процесса измерения угловой ошибки Да есть величина постоянная, то вычисление ошибки по скорости Д (О также производится на постоянном интервале и коэффициент К,.ы М K.,TD (где М 1 с) преобразования ошибки по скорости остается постоянным во всем диапазоне регулирования. Следовательно и коэффициент усиления устройства для стабилизлции частоты вращения, определяемый коэффициентами преобразования К.... и К есть величина постоянная (при любых зяд;ио1цих воздействиях), что повышлет точность и быстродействие устройства.

Выходной код регистра 14 Nfj. пропорциональный угловой ошибки Да. и выходной код , корректирующего блока 15. пропорциональный ошибке по скорости, по ступают не входы сумматора 16. где в результате суммирования формируется код NcM x х( К„чДш), несущий информацию об угловой ошибке

Да. так и об ошибке по скорости Дм. С выхода сумматора 16 код МСм подают на цифровой вход блока 1Я формирования кода управления, на управляющие входы которого поступают выходные сигналы блока 17

задания режима работы. При наличии сигнала Г на выходах Р и Т (см. фиг.12 и 13) блока 17 (установившийся режим (фазового сравнения) выходной код NCM Ny сумматора через блок 18 формирования кода управления проходит на вход цифроаналогового преобразователя 19, где преобразуется в аналоговый сигнал, подаваемый в систему управления электродвигателя. Если частота сигнала задания f3R превышает частоты сигнала обратной связи f0c (foe fо + Zx х(2л)1 на выходе датчика 5) сигнал Г появляется только на выходе Р блока 17 задания режима работы, с выхода блока 18 формирования кода управления снимают

код Ny, во всех разрядах которого записаны 1, и подают его на вход цифроаналогового преобразователя 19, переводя устройство для стабилизации частоты возщечия в режим разгона. Аналогично осуществляется и

режим торможения (f3fl foe), только в дачном случае сигнал 1 появляется на выходе Т блока 17, а с выхода блока 18 снимают код. во всех разрядах которого записаны О. Блок 6 сравнения ра5отэрт

образом.

Если поступающий на один из входов блока б сравнения выходной сигнал UD частотно-модулирующего датчика 5 больше и

поступающего на другой вход сигнала исл слежения (по амплитуде напряжения, измеренной в данной точке), на выходе компаратора 22 получают сигнал, соответствующий 1 (фиг.Зв. 4в), в противном случае выходной сигнал компаратора 22 равен по уровню напряжению О. В дифференциаторе 23 определяют производную выходного сигнала UD датчика 5 скорости, а пороговый элемент 24 преобразует полученный таким образом

аналоговый сигнал в импульсный (фиг 36, 46), поступающий на один из vrriorj схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 25. На г.;г:н.й пход схемы 25 приходит выходно,; г/.ч н ..i омпа- ратора 22.

Нэ участке а-в (фиг.З и 4) возрастания выходного сигнала UD частотно-модулирующего датчика 5 скорости (производная имеет положительный знак и, следовательно, выходной сигнал порогового элемента 24 равен Г. фиг. 36. 46) нулевой уровень сигнала на выходе компаратора 22 (фиг, 4в) показывает, что выходной сигнал UD датчика 5 скорости отстает по фазе от сигнала Усл слежения (фиг. За)., а уровень, равный уровню 1 (фиг. 4в), соответствует опережению по фазе сигналом UD сигнала Уся (фиг. 4а). На участке в-с (фиг. За, 4а) убывания выходного сигнала UD датчика 5 скорости (выходной сигнал порогового элемента 24 равен О, фиг. 36, 46) нулевой уровень сигнала на выходе компаратора 22 (фиг 4в) соответствует опережению по фазе выходным сигналом UD датчика 5 скорости сигнала Uc слежения (фиг. 4а). а уровень, равный уровню 1 (фиг. Зв), эквивалентен отставанию по фазе сигнала UD от сигнала Усл. Соответственно и выходной сигнал схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 25 равен Г (фиг. Зг) при отставании по фазе сигнала UD от сигнала Уел слежения (фиг. За) и О (фиг. 4г) при опережении по фазе сигналом UD сигнала Уел (фиг. 4а). С выхода схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 25 сигнал поступает на вход схемы 26 синхронизации, а с выхода порогового элемента 24 - на вход схемы 27 синхронизации, где осуществляется синхронизация сигналов с импульсамы частоты f3.

Блок 12 формирования сигналов запрета работает следующим образом.

В случае превышения амплитудой Uc сигнала слежения (фиг,6) амплитуды UD выходного сигнала датчика 5 скорости на выходе А блока 12 формируют импульсы (фиг. бж). которые запрещают прохождение через элемент И 8 сигнала частоты fa на вычитающий вход -1 реверсивного счетчика 9. Счетчик 9 не производит счет в - и в сигнале Уся слежения отсутствуют соответствующие выбросы (фиг. 6в). При амплитуде Уся сигнала слежения, меньшей амплитуды UD выходного сигнала датчика 5 скорости (фиг.7), импульсы запрета формируют сначала на выходе В (фиг. 7ж), а затем на выходе А блока 12(фиг. 7з). Импульсы с выхода В запирают схему И 7, запрещая работу счетчика 9 в режиме слежения, а импульсы с выхода А запирают схему И 8, и реверсивный счетчик 9 не работает в режиме вычитания. Блогодаря этому в сигнале слежения (фиг. 7в) отсутствуют ложные выбросы.

Импульсы запрета счета в - (выход В) формируют по алгоритму

(Пдф (N))(FM).

где Уд - импульсный сигнал, инверсный выходному сигналу блока сравнения (выход D, выход порогового элемента 24):

(N) - старший разряд выходного кода

реверсивного счетчика 9;

(N-1) - проинвертированный предпоследний разряд выходного кода счетчика 9, а импульсы запрета счета в + (выход А) - в соответствии с логическим выражением

(UA®(N))(N-1),

где Уд - сигнал с выхода О блока 6 сравнения;

(N-1) - предпоследний разряд кода реверсивного счетчика 9.

5 Для этого сигнал инвертируют в инверторе 28 (фиг. 66,76), а затем подают на один из входов первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 30. На второй вход схемы 30 приходит сигнал N (фиг. 6г, 7г), старшего разряда вы0 ходного кода N реверсивного счетчика 9. В первой схеме И-НЕ 31 производят логическое умножение выходного сигнала схемы ИСКЛЮЧАЮЩЕЕ ИЛИЗООд0Й(фиг.6е)на предварительно проинвертированный (эле5 мент НЕ 29) сигнал предпоследнего разряда (N-1) выходного кода реверсивного счетчика 9 (фиг. 6д). В результате на выходе А блока 12 формирования сигналов запрета формируются импульсы запрета счета в 0 (фиг. 6ж). .

Импульсы запрета счета в + (фиг. 7ж) получают на выходе В блока 12 в результате выполнения операции логического умножения (И-Н Е 32) сигнала (N-1) предпоследнего

5. разряда выходного кода реверсивного счетчика 9 (фиг. 7д) на выходной сигнал второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 36 (U.njЈ(N)). Сигналы, управляющие работой блока 11 задания амплитуды сигнала, формируют

0 из импульсов запрета, для чего импульс запрета счета в + (выход В) инвертируют в элементе 33 и подают на выход С блока 12 (фиг. 7и). Сигнал, задающий уменьшение напряжения (выход D, фиг. 6з) формируют

5 из импульса запрета счета в - (выход А). Для обеспечения удовлетворительной работы блока 11 задания амплитуды сигнала исключают прохождение импульсов запрета счета в - на выход D в случае меньшей по

0 сравнению с амплитудой Уо выходного сигнала датчика 5 скорости амплитуды Усл сигнала слежения. Это обеспечивают путем включения в блок 12 D-триггера 34, который переключается по переднему фронту им5 пульсов, формируемых на выходе С (фиг.7и). Обнуление триггера 34 происходит по сигналу, полученному в результате логического умножения (схема И 35) сигнала предпоследнего (N-1) разряда выходного кода реверсивного счетчика 9 (фиг 7д) и выходного

сигнала схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 30 (Цд©(М)) (фиг. 8е). Таким образом, на выход D блока 1 формирования сигналов запрета через схему И 37 предварительно проинвер- тированные (НЕ 37) импульсы запрета счета в - поступают только при амплитуде Uc сигнала слежения, большей амплитуды UD выходного сигнала датчика 5 скорости. Данные импульсы вызывают уменьшение напряжения Don в блоке 11 задания амплитуды сигнала. За счет синхронизации сигнала U с импульсами частоты fa выходные сигналы блока 12, получаемые путем логической обработки кода N и сигнала U , оказываются синхронными с импульсами частоты fa, благодаря чему отсутствует возможность укорачивания входных импульсов счетчика 9.

Вычитающий блок 13 работает следующим образом.

На вхрды элементов НЕ 39 поступает ступенчато нарастающий сигнал {код Nf, пропорциональный фазе выходного сигнала UD датчика 5 скорости) с выхода реверсивного счетчика 9. Второй ступенчато нарастающий сигнал (код М3д. эквивалентный фазе сигнала задания) подают на входы В первого сумматора 40. За счет инверсии в элементах НЕ 39 и подачи Г на вход переноса первого сумматора 40 код Nf преобразуется в дополнительный код, который в сумматоре 40 суммируют с кодом N3fl. что эквивалентно выполнению операции вычитания выходного кода М реверсивного счетчика9 из кода М3д, снимаемого с выхода суммирующего счетчика 3 (МЭд - NJ-). Получаемый в результате на выходе сумматора 40 кодовый сигнал имеет как положительные, так и отрицательные значения (фиг. 126. 11 б, 136) Причем отрицательные значения выходного кода сумматора 40 не соответствуют действительному значению угловой ошибки Да (так, при постоянном фазовом сдвиге между ступенчато нарастающими сигналами N3a и г . фиг. 12а, 13а, выходной код сумматора 39 имеет два значения, фиг. 126,136, одно из которых (отрицательное) является смещенным). Чтобы получить код, соответствующий угловой ошибке Да, отрицательные значения выходного кода сумматора 40 (снимаемый с выхода старшего разряда сумматора 40 знаковый разряд равен 1) дополнительно смещают, суммируя их с кодом, равным по величине максимальному коду N угловой ошибки, во всех разрядах которого записаны Г(111...1). Полученный в результате кодовый сигнал(диэграммы 2, фиг.12в, 13в) изменяется от нулевого 000...00 (при угловой ошибке Да, равной нулю) до максимального 111...11 (при Да Z 2я ) значения, что не позволяет определить знак фазового рассогласования (угловой ошибки). Следовательно, при любом отклонении частот сигналов задания и обратной связи (fsfl foe и 1Э& foe) независимо от того, какая частота выше, код угловой ошибки превышает код, соответствующий угловой ошибке. равной нулю (Да- 0). Для того, чтобы в установившемся режиме код угловой ошибки NAJ, превышал код нулевой ошибки в случае, когда частота сигнала задания тэд больше частоты f0c сигнала обратной связи,

и становился меньше кода отклонении в большую сторону частоты foe сигнала обратной связи ( foe), выходной код первого сумматора 40 дополнительно смещают на величину, эквивалентную угловой

ошибке Да Z л (код 011...11). Таким образом, к выходному коду сумматора 40 необходимо прибавить код О11...110(0 в старшем и младшем разряде) в случае отрицательного значения кода (Г на знаковом

выходе сумматора 40) или код 0111... 11 (О и в старшем разряде) при положительном значении кода (0й на знаковом выходе сумматора 40). Для этого выходной код первого сумматора 40 подают на входы А второго

сумматора 42. На вход В1 младшего разряда сумматора 42 через элемент НЕ 41 поступает сигнал с выхода старшего знакового разряда QN первого сумматора 40, на вход BN старшего разряда сумматора 42 - сигнал

О, а на остальные входы В (B2...B(N-1) - сигнал, равный по уровню 1. В результате в уста но вив шее я режиме код Ыд угловой ошибки, снимаемый с выхода второго сумматора 42, изменяется относительно кода

нулевой угловой ошибки (0111...111) в большую сторону (диаграмма 1,фиг.12в)при fafl foe и в меньшую (диаграмма 1. фиг. 13 в) при f3A foe. В режиме разгона, когда частота сигнада задания 3д значительно

превышает частоту сигнала обратной связи foe. выходной код сумматора 42 представляет собой ступенчато нарастающий сигнал (диаграмма 1, фиг.Юв). В режиме торможения (f3A значительно меньше foe) выходной

код сумматора 42 ступенчато убывает (диаграмма 1. фиг. 12в).

Блок 17 задания режима работы работает следующим образом.

На вход элемента НЕ 43 и второй вход

схемы И 47 поступает сигнал со знакового выхода корректирующего блока 15 (при ре- ализации корректирующего блока 15 на регистре 20 и вычитателе 21 знаковым выходом служит выход старшего разряда

вычитателя 21). В случае превышения частотой сигнала задания Эд частоты сигнала обратной связи foe на выходе вычитающего блока 13 формируется ступенчато нарастающий сигнал, в результате чего на знаковом выходе корректирующего блока 15 устанавливается О (так как код угловой ошибки N, .(К), взятый в К-й момент времени, больше кода (K-1). взятого в(К-1)-й момент времени). Сигнал О сбрасывает в ноль второй счетчик 46 и после инверсии в элементе НЕ 43 разрешает прохождение через схему И 44 импульсов частоты fs на вход первого счетчика 45, Частоту fs выбирают равной макси- мальной частоте fi - faflKo сигнала, снимаемого с первого выхода преобразователя 2 код-частота, а коэффициент пересчета Ms счетчика 45 не должен превышать коэффициент пересчета Кз счетчика 3 (например. «45 Кз)- При заполнении счетчика 45до значения щ

.JojtilЈ). (,П1

f0(fiK45r1) на первом выходе дешифратора 50 появляется Г, которая устанавливает О на выходе первого триггера 48 (выход Т). П ричем в момент заполнения счетчика 45 до значения пз tpfs (Мб) (гДе tp время разгона привода до максимальной скорости) Г устанавливается на втором выходе дешифратора 50. В результате выход второго триггера 49 переходит в 1. Такое состояние выходов блока 17 (Р - 1, Т - О) соответствует заданию в приводе режима сззгонэ.

Когда частота сигнала задания fjfl становится меньше частоты сигнала обратной связи foe (фиг. 11). на выходе вычитающего блока 13 формируется ступенчато убывающий сигнал, и на знаковом выходе корректирующего блока 15 устанавливается 1 (так как код N/ (К) меньше кода МдЦК-)). Счетчик 45 сбрасывается в ноль. Открывается схема И 47, и на тактовый вход второго счетчика 46 поступают импульсы частоты fs. Второй дешифратор 51 работает аналогично первому дешифратору 50. т.е. при заполнении счетчика 46 до значения П2 tpfs(K46) (К46 - коэффициент пересчета счетчика 46, К4б° K4s) на втором выходе дешифратора 51 появляется Г, которая устанавливает в Г первый триггер 48 (на выходе второго триггера 49 1). Когда счетчик 46 заполнится до

значения щ - (Ъ+(2л) 1 гурмане )(fs)1 1 появляется на первом выходе второго дешифратора 49, в результате чего на выходе второго триггера 49 устанавливается О (Р - О, Т - Г). Устройство для стабилизации частоты вращения электродвигателя переходит в режим торможения.

Наличие 1 на обоих выходах блока 17 соответствует режиму синхронизации (фазового сравнения) устройства. Данная комбинация появляется на выходах блока задания режима работы при малых отклонениях одна относительно другой частот задания тэд и обратной связи f0c, когда счетчики 45 и 46 не успевают заполниться до значения ГЦ.

Таким образом, блок 17 задания режима работы переводит выход Р в состояние 1 (О на выходе Т) при f0c faA, выход Т в 1 (О на выходе Р) при foc тэд. две Г на выходах Р и Т при f0c fsfl.

Использование устройства для стабилизации частоты вращения обеспечивает повышение быстродействия и точности за счет уменьшения интервала TD дискретности процесса измерения угловой ошибки Да (интервал дискретности задается периодом импульсного сигнала частоты fs и остается постоянным во всем диапазоне регулирования, а его величина меньше величины интервала дискретности прототипа); поддержания постоянной во всем диапазоне регулирования величины коэффициента усиления устройства; независимо от задающего воздействия поддерживается постоянная величина коэффициента преобразования Кд угловой ошибки Лай коэффициента преобразования ошибки по скорости Дса

Формула изобретения 1. Устройство для стабилизации частоты вращения электродвигателя, содержащее задатчик скорости, к выходу которого подключен преобразователь код - частота, частотно-модулирующий датчик скорости, суммирующий счетчик, регистр, корректирующий блок, два элемента И, сумматор, один из входов которого подключен к выходу корректирующего блока, и цифроанало- говый преобразователь, отличающее- с я тем, что, с целью повышения быстродействия и точности, в него введены формирователь опорных напряжений, блок сравнения, реверсивный счетчик, блок синусного преобразования, блок задания амплитуды сигнала, блок формирования сигналов запрета, вычитающий блок, блок задания режима работы и блок формирования кода управления, вход формирователя опорных напряжений подключен к второму выходу преобразователя код - частота, первый выход которого подключен к входу суммирующего счетчика, а выходы соединены с

входами частотно-модулирующего датчика скорости, один из входов блока сравнения подключен к выходу частотно-модулирующего датчика скорости, инверсный выход блока сравнения - к первому входу первого элемента И, первый вход второго элемента И соединен с прямым выходом блока сравнения, вторые входы обоих элементов объединены и подключены к второму входу блока сравнения и третьему выходу преобразователя код - частота, выходы первого и второго элементов И подключены соответ- ственно к суммирующему и вычитающему входам реверсивного счетчика, первый вход блока задания амплитуды сигнала подключен к четвертому выходу преобразователя код - частота, а выход - к управляющему входу блока синусного преобразования, выход которого подключен к третьему входу блока сравнения, выходы блока формирования сигналов запрета соединены соответственно с третьими входами первого и второго элементов И и вторым и третьим входами блока задания амплитуды сигнала, вход блока формирования сигнала запрета подключен к D-выходу блока сравнения, а информационный вход блока формирования сигналов запрета соединен с выходом реверсивного счетчика, информационным входом блока синусного преобразования и одним входом вычитающего блока, другой вход которого подключен к выходу суммирующего счетчика, а выход вычитающего блока соединен с входом регистра, выход которого подключен к входу корректирующего блока и второму входу сумматора, С- входы регистра и корректирующего блока объединены с вторым входом блока задания режима работы и подключены к пятому выходу преобразователя код - частота, знако- вый выход корректирующего блока соединен с первым входом задания режима работы, выход сумматора - с первым входом блока формирования кода управления, другими входами подключенного к соответствующим выходам блока задания режимов работы, выход блока формирования кода управления подключен к входу цифроанало- гового преобразователя, выход которого является выходом устройства.

2. Устройство поп.1,отличающее- с я тем, что блок сравнения содержит компаратор, дифференциатор, входом подключенный к прямому входу компаратора, пороговый элемент, схемы ИСКЛЮЧАЮЩЕЕ ИЛИ. один из входов которой соединен с выходом компаратора, а другой через пороговый элемент подключен к выходу дифференциатора, и две схемы синхронизации, одна из которых соединена с выходом

схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, а другая - с выходом порогового элемента, инвертирующий вход компаратора является третьим входом блока, прямой вход компаратора - первым входом блока, объединенные входы схем синхронизации являются вторым входом блока, выходы первой схемы синхронизации - соответственно инверсным и прямым выходами блока сравнения, а выход второй схемы синхронизации - D-выходом блока.

3. Устройство поп.1.отличающее- с я тем, что блок формирования сигналов запрета содержит два элемента НЕ, один из которых подключен к первому входу первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ. а другой - к второму входу первой схемы И-НЕ. вторую схему И-НЕ, выход которой через третий элемент НЕ соединен с С-входом D-триггера. в вход - с входами второго элемента НЕ и первой схемы И. подключенной к R-входу D-триггера, вторую схему ИСКЛЮЧАЮЩЕЕ ИЛИ, присоединенную к первому входу второй схемы И-НЕ. и вторую схему И, один из входов которой через четвертый элемент НЕ подключен к выходу первой схемы И-НЕ, а другой - к инвертирующему выходу D-триггера, при этом первый вход первой схемы И-НЕ подключен к выходу первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ. вторым входом соединенной с вторым входом второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которой соединен с входом первого элемента НЕ, а второй вход первой схемы И соединен с выходом первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, D-вход триггера подключен к шине логической единицы, вход первого элемента НЕ является входом блока, второй вход второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ и вход второго элемента НЕ являются информационными входами блока, а выходы первой схемы И-НЕ, второй схемы И-НЕ, третьего элемента НЕ и второй схемы И являются выходами блока.

4. Устройство поп.1,отличающее- с я тем, что вычитающий блок содержит N элементов НЕ, выходы которых подключены к А-еходам первого сумматора, и второй сумматор, А-входами соединенный с выходами первого сумматора, при этом В1-вход младшего разряда второго сумматора подключен к выходу элемента НЕ, вход которого соединен с выходом QN старшего знакового разряда первого сумматора, BN- вход старшего разряда второго сумматора подключен к шине логического нуля, а остальные В-входы второго сумматора и вход переноса первого сумматора соединены с шиной логической единицы, В-входы первого сумматора являются первыми входами

блока, входы элементов НЕ - вторыми входами блока, а выход второго сумматора - выходом блока.

5, Устройство поп.1,отличэющее- с я тем, что блок задания режима работы содержит элемент НЕ, через первую схему И подключенный к тактовому входу первого счетчика и непосредственно к входу сброса второго счетчика, вторую схему И, один из входов которой соединен с входом элемента НЕ и входом сброса первого счетчика, второй вход объединен с вторым входом первой схемы И, а выход подключен к тактовому

0

входу второго счетчика, первый и второй триггеры, первый и второй дешифраторы, входы которых соединены с выходами соответственно первого и второго счетчиков, при этом первые выходы первого и второго дешифраторов подключены к R-входам сброса соответственно первого и второго триггеров, а их вторые выходы соединены с входами установки соответственно второго и первого триггеров, вход элемента НЕ является первым входом блока, вход второй схемы И - вторым входом блока, а выходы первого и второго триггеров - первым и вторым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1988 |

|

SU1594689A1 |

| Цифровой следящий привод | 1983 |

|

SU1151925A1 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| Способ управления положением сварочной горелки и устройство для его осуществления | 1987 |

|

SU1544534A1 |

| Устройство для позиционного управления | 1983 |

|

SU1104466A1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| Устройство для управления электродвигателем переменного тока | 1983 |

|

SU1336188A1 |

| Устройство для управления электродвигателем переменного тока | 1984 |

|

SU1457141A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

Изобретение относится к электротехнике и может быть использовано для стабилизации частоты вращения электродвигателей в системах автоматического управления. Целью изобретения является повышение быстродействия и точности. Это достигается путем уменьшения интервала Тф дискретности процесса измерения углэвой ошибки Да, так как интервал дискретности задается периодом импульсного сигнала частоты и остается постоянным во всем диапазоне регулирования. Кроме того, во всем диапазоне поддерживается постоянной величина коэффициента усиления устройства. 4 э.п. ф-лы, 16 ил. выходу преобразователя код - частота, а выходы соединены с входами частотно-модулирующего датчика скорости, один из входов блока сравнения подключен к выходу частотно-модулирующего датчика скорости. инверсный выход блока сравнения подключен к первому входу первого элемента И, первый вход второго элемента И соединен с прямым выходом блока сравнения, вторые входы обоих элементов объединены и подключены к второму входу блока сравнения и третьему выходу преобразователя код - частота, выходы первого и второго элементов И подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, первый вход блока задания амплитуды сигнала подключен к четвертому выходу преобразователя код - частота, а выход - к управляющему входу блока синусного преобразования, выход которого подключен к третьему входу блока сравнения выходы блока формирования сигналов запрета Соединены соответственно с третьими входами первого и второго элементов И и вторым и третьим входами блока задания амплитуды сигнала, вход блока формироваЁ

l/ft/x.

$tf.J

Фиг.

т

Фи&5

Ж

дьнЯП LJ 3 ----П

фуг б

Фие.7

Фиг. 8

Фиг. 9

to

t fl

фиг. Н

t a

) к

tft/гН ) ,%

%-Wf

L

Фиг. /6

| Устройство для стабилизации скорости электропривода | 1984 |

|

SU1239822A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1987 |

|

SU1508332A1 |

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1992-01-23—Публикация

1990-02-27—Подача