1

Изобретение относится к вычислительной технике, в частности к устройствам тестового контроля цифровых схем.

Известно устройство для проверки функционирования схем, содержащее блок ввог да, блок входных и выходных эталонных сигналов, коммутатор, контрольный регистр, блок сравнения и блок индикации 1.

Наиболее близким к изобретению по технической сущности и функциональным возможностям является устройство для контроля схем цифровых вычислительных машин, содержащее анализируемую схему, блок ввода, регистр аадания, блок управления, блок сравнения, блок управления, блок индикации блок эталонов, компаратор-преобразователь, при этом выход блока выарда соединен со входом регистра задания и блока управления, второй вход которого соединен с выходом блока сравнения, второй выход блока сравнения соединен со входом блока индикации, выходы блока управления соединены соответственно со входами регистра задания, блока ввода и блока индикации, выход регистра задания соединен со вторым входом блока сравнения, второй выход регистра задания соединен со входом компаратора-преобразователя, выход которого соединен со входом блока сравнения, второй вход преобразователя и третий вход компаратора-преобразователя соединен с соответствующими выходами блока управленияИ. 5Недостаток известного устройства состоит в том, что оно не может контролировать амплитудно-временные параметры и фор. мулу анализируемых сигналов.

Цель изобретения - расщирение функциональных возможностей за счет контроля

10 амплитудно-временных параметров и формы сигналов.

С этой целью в устройство для контроля схем цифровых вычислительных мащин, содержащее регистр тестовых сигналов, блок сравнения, блок управления, блок индикации,

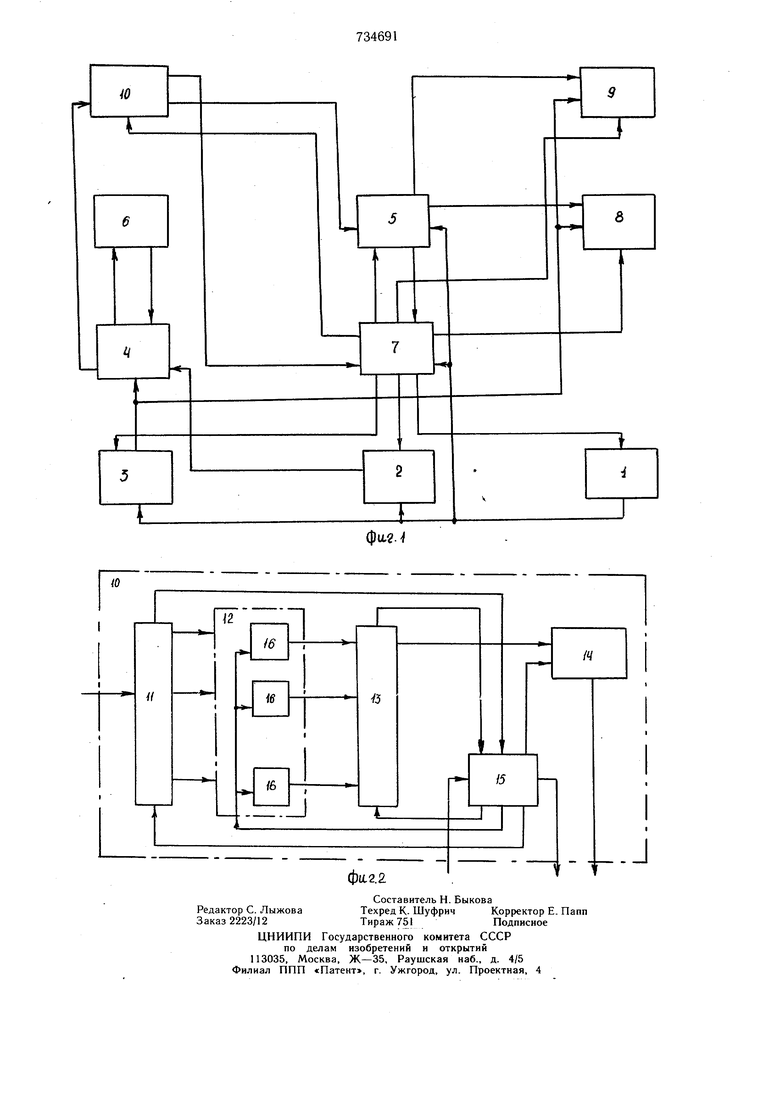

IS блок ввода, блок вывода, причем вход блока ввода подключен к первому выходу блока управления, второй выход которого соединен с первым входом регистра тестовых сигналов, второй вход которого соединен с выходом блока ввода, с первым входом блока управления и с первым входом блока сравнения, второй вход блока сравнения подключен к третьему выходу блока управления, второй вход которого соединен с четвертым выходом блока сравнения, второй выход которого подключен к первому входу блока вывода, второй вход блока вывода соединен с пятым выходом блока управления, третий вход блока вывода соединен с первым входом блока индикации, второй вход которого подключен к третьему выходу блока сравнения, третий вход блока индикации подключен к четвертому выходу блока управления, введены блок кодирования, многоканальный коммутатор и регистр адреса, причем первый вход регистра адреса соединен со вторым входом регистра тестовых сигналов, выход которого подключен к первому входу многоканального коммутатора, второй вход которого соединен с выходом контролируемой схемы, вход которой подключен к первому выходу многоканального коммутатора, третий вход многоканального коммутатора подключен к выходу регистра адреса и к первому входу блока индикации, второй вход регистра адреса соединен с шестым выходом блока управления, седьмой выход которого соединен с первым входом блока кодирования, второй вход которого соединен со вторым выходом многоканального коммутатора, первый выход блока кодирования подключен к третьему входу блока управления, второй выход блока кодирования соединен со вторым входом блока сравнения. Блок кодирования содержит квантователь-распределитель, первый блок памяти, мультиплексор, второй блок памяти и аналого-цифровой преобразователь, причем первый вход квантователя-распределителя является вторым входом блока кодирования, второй вход квантователя-распределителя подключен к первому выходу второго блока памяти, второй выход которого является первым выходом блока кодирования, третий выход второго блока памяти соединен с первым входом первого блока памяти, второй, третий и четвертый входы которого подключены соответственно к первому, второму и третьему выходам квантователя-распределителя, четвертый выход которого соединен с первым входом второго блока памяти, второй вход которого является первым входом блока кодирования, третий вход второго блока памяти соединен с первым выходом мультиплексора, второй выход которого соединен с первым входом аналого-цифрового преобразователя, второй вход которого подключен к четвертому выходу второго блока памяти, пятый выход которого соединен с первым входом мультиплексора, второй, третий и четвертый входы которого соединены соответственно с первым, вторым и третьим входами первого блока памяти, выход аналого-цифрового преобразователя является вторым выходом блока кодирования. На фиг. 1 представлена блок-схема предложенного устройства; на фиг. 2 - блок-схема кодировщика контролируемых сигналов. Устройство для контроля цифровых схем цифровых вычислительных машин содержит блок 1 ввода, регистр 2 тестовых сигналов, регистр 3 адреса, многоканальный коммутатор 4, блок 5 сравнения, анализируемую схему 6, блок 7 управления, блок 8 индикации, блок 9 вывода и блок 10 кодирования контро лируемых сигналов. Блок 10 кодирования контролируемых сигналов состоит из квантователя-распределителя 11 на m выходов, блока 12 памяти, мультиплексора 13 m аналоговых сигналов, аналого-цифрового преобразователя 14 и схемы 15 управления. Блок 12 памяти содержит m аналоговых запоминающих элементов 16. Блок 1 ввода предназначен для ввода информации, необходимой для анализа схем;. регистр 2 тестовых сигналов - для генерации тестовых сигналов в соответствии с программой испытаний; регистр 3 адреса - для хранения и выдачи на много-канальный коммутатор 4 адресов входных и выходного контактов анализируемой схемы 6 при очередном цикле контроля; многоканальный коммутатор 4 - для коммутации выходов ре- . гистра 2 тестовых сигналов на соответствующие входные контакты анализируемой схемы 6, а также контролируемого выходного контакта анализируемой схемы 6 на блок 10 кодирования контролируемых сигналов в каждом цикле контроля; блок 5 сравнения - для сравнения кодов контролируемого сигнала анализируемой схемы 6 с эталонными кодами, поступающими из блока 1 ввода. Блок 7 управления вырабатывает управляющие сигналы и синхронизирует работу всего устройства в зависимости от сигналов, поступающих на него из блока 1 ввода, блока 5 сравнения и блока 10 кодирования контролируемых сигналов. Блок 8 индикации предназначен для индикации результатов контроля, а блок 9 вывода - для вывода номеров выходных контактов анализируемой схемы 6 в случае несовпадения кодов контролируемого сигнала с эталонными кодами, а также для получения и вывода эталонных кодов при подключении к устройству эталонной схемы. Квантователь-распределитель 11 предназначен для квантования контролируемого сигнала по времени на m уровней и распределения квантованных уровней в m аналоговых запоминающих элементов 16 блока 12 памяти. Блок 12 памяти состоит из ш аналоговых запоминающих элементов 16, предназначенных для хранения квантованных по времени уровней контролируемого сигнала. Мультиплексор 13 m аналоговых сигналов предназначен для поочередной передачи m квантованных по времени уровней контролируемого сигнала на аналого-цифровой преобразователь 14, который предназначен для кодирования квантованных по времени уровней контролируемого сигнала.

Схема 15 управления предназначена для управления и синхронизации блока 10 кодирования контролируемых сигналов в соответствии с командами блока 7 управления.

Устройство работает следующим образом.

Тестовая и эталонная информация записываются на перфоленту. Вся программа состоит из п подпрограмм (циклов), п выби рается из условия полного контроля анализируемой схемы 6. Каждая подпрограмма разбита на два массива. Первый массив состоит из тестовой информации, в которой задаются номера входных контактов анализируемой схемы 6, адреса формирователей тестовых сигналов из регистра 2 тестовых сигналов, которые необходимо подключить ко входным контактам анализируемой схемы 6, а также номер ее выходного контакта, который подключается к блоку 10 кодирования контролируемых сигналов, т. е. первый массив содержит информацию о необходимых коммутациях. Второй массив состоит из эталонной информации и содержит ш кодов контролируемого сигнала.

Программа проверки схемы начинается с кода «Начало программы. По этому коду блок 7 управления устанавливает устройство в исходное состояние. Затем вводится тестовая информация, которая в зависимости от признака, записанного на носителе, поступает в регистр 2 тестовых сигналов и в регистр 3 адреса соответственно. В соответствии с поступающей информацией в регистре 2 тестовых сигналов происходит подготовка выбранных формирователей тестовых сигналов. Многоканальный коммутатор 4 обеспечивает необходимые коммутации в соответствии с информацией, записанной в регистр 3 адреса. По окончании ввода тестовой информации из блока 1 ввода поступает код «Конец коммутации. По этому коду блок 7 управления вырабатывает команду, разрещающую выдачу тестовых сигналов из регистра 2 тестовых сигналов через многоканальный коммутатор 4 на входные контакты анализируемой схемы 6, запускают схему 15 управления блока 10 кодирования контролируемых сигналов и дает команду на блок 1 ввода для ввода на первый вход блока 5 сравнения первого из m эталонных кодов контролируемого сигнала. Выходной сигнал с контролируемого контакта анализируемой схемы 6 через многоканальный коммутатор 4 поступает на квантователь-распределитель 11 блока 10 кодирования контролируемых сигналов. Квантователь-распределитель И, управляемый схемой 15 управления, производит квантование по времени контролируемого сигнала на m уровней и распределяет и записывает m полученных квантованных уровней в m аналоговых запоминающих элементах 16 блока 12 памяти. Затем квантователь-распределитель 11 через схему 15 управления подает сигнал на мультиплексор

13 m аналоговых сигналов, который подключает вход аналого-цифрового преобразователя 14 к выходу первого аналогового запоминающего элемента 16. Аналого-цифровой преобразователь 14 выдает на второй вход блока 5 сравнения код первого квантованного уровня контролируемого сигнала. При сравнении эталонного и контролируемого кодов блок 5 сравнения выдает сигнал, по которому блок 7 управления разрещает ввод на блок 5 сравнения следующего эталонного кода и через схему 15 управления и

10 мультиплексор 13 m аналоговых сигналов подключает на вход аналого-цифрового преобразователя 14 выход следующего аналогового запоминающего элемента 16 и так далее гп раз.

Если контролируемая схема по данной

5 подпрограмме работает правильно, блок 7 управления вырабатывает команду для считывания следующей подпрограммы и цикл работы устройства повторяется.

По окончании всей программы провер0ки блок 7 управления вырабатывает сигнал годности анализируемой схемы 6, который поступает в блок 8 индикации и высвечивает табло «Годен.

В случае несоответствия логического функционирования либо заданных параметров

S анализируемой схемы 6 в соответствии с программой блок 7 управления вырабатываем сигнал, останавливающий дальнейшую проверку схемы. Этот сигнал поступает в блок 8 индикации, который высвечивает табло

0 «Брак и номер контакта анализируемой схемы 6, по которому произощел сбой. По этому же сигналу блок 9 вывода производит вывод на печать адреса выходного контакта анализируемой схемы 6, по которому произощел сбой. По окончании вывода блок 7 уп5равления вырабатывает команду, по которой устройство переходит к контролю анализируемой схемы 6 по следующей подпрограмме.

Устройство позволяет получать эталон0ные коды контролируемых сигналов. Для это го к устройству подключается эталонная анализируемая схема 6, а к блоку 9 вывода - перфоратор.

Введение кодировщика контролируемых

5 сигналов, состоящего из квантователя-распределителя на гп выходов, блока памяти, содержащего m аналоговых запоминающих элементов, мультиплексора m аналоговых сигналов, аналого-цифрового преобразова0теля и схемы управления, выгодно отличает предлагаемое устройство от известных, которые проверяют анализируемые схемы на наличие или отсутствие сигнала или контролируют величину амплитуды сигналов в заданных допусках. Предлагаемое устройство производит квантование по времени контролируемого сигнала на m дискретных уровней и кодирует каждый уровень цифровым кодом. Таким образом, по каждому контролируемому сигналу предлагаемое устройство выдает m цифровых-кодов,,которые содержат полную информацию об амплитудновременных характеристиках и форме данного сигнала.. В итоге значительно увеличивается объем контроля и повышается его качество. Формула изобретения /.Устройство для контроля схем цифровых вычислительных машин, содержаш,ее регистр тестовых сигналов, блок сравнения, блок управления, блок индикации, блок ввода, блок вывода, причем вход блока ввода подключен к первому выходу блока управления, второй выход которого соединен с первым входом регистра тестовых сигналов, второй вход которого соединен с выходом блока ввода, с первым входом блока управления и с первым входом блока сравнения, второй вход блока сравнения подключен к третьему выходу блока управлени51, второй вход которого соединен с первым выходом блока сравнения, второй выход которого подключен к первому входу блока вывода, второй вход блока вывода соединен с пятым выходом блока управления, третий вход блока вывода соединенс первым входом блока индикации, второй вход которого подключен к третьему выходу блока сравнения, третий вход блока индикации подключен к четвертому выходу блока управления, отличающееся тем, что, с целью расширения функциональных возможностей за счет контроля амплитудно-временных параметров и формы сигналов, в устройство введены блок кодирования, многоканальный коммутатор и регистр адреса, причем первый вход регистра ад реса соединен со вторым входом регистра тестовых сигналов, выход которого подключен к первому входу многоканального коммутатора, второй вход которого соединен с выходом контролируемой схемы, вход которой подключен к первому выходу многоканального коммутатора, третий вход многоканального коммутатора подключен к выходу регистра адреса и к первому входу блока индикации, второй вход регистра адреса соединен с шестым выходом блока управления, седьмой выход которого соединен с первым входом блока кодирования, второй вход которого соединен со вторым выходом многоканального коммутатора, первый выход блока кодирования подключен к третьему входу блока управления, второй выход блока кодирования соединен со вторым входом блока сравнения. 2. Устройство по п. 1, отличающееся тем, что блок кодирования содержит квантователь-.распределитель, первый блок памяти, мультиплексор, второй блок памяти и аналого-цифровой преобразователь, причем первый вход квантователя-распределителя является вторым входом блока кодирования, второй вход квантователя-распределителя подключен к первому выходу второго блока памяти, второй выход которого является первым выходом блока кодирования, третий выход второго блока памяти соединен с первым входом первого блока памяти, второй, третий и четвертый входы которого подключены соответственно к первому, второму и третьему выходам квантователя-распределителя, четвертый выход которого соединен с первым входом второго блока памяти, второй вход которого является первым входом блока кодирования, третий вход второго блока -памяти соединен с первым выходом мультиплексора, второй выход которого соединен с первым входом аналого-цифрового преобразователя, второй вход которого подключен к четвертому вь1ходу второго блока памяти, пятый выход которого соединен с первым входом мультиплексора, второй, третий и четвертый входь которого соединены соответственно с первым, вторым и третьим выходами первого блока памяти, выход аналого-цифрового преобразователя является вторым выходом блока кодирования. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 354416, кл. G 06 F 11/00. 2. Авторское свидетельство СССР № 378852, кл. G 06 F 11/00.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Электронно-кодовый замок | 1988 |

|

SU1606642A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для контроля цифровыхСХЕМ | 1979 |

|

SU849217A1 |

| Устройство для контроля цифровых блоков | 1978 |

|

SU746553A1 |

| Устройство для диагностики неисправностей технических объектов | 1987 |

|

SU1515175A2 |

Авторы

Даты

1980-05-15—Публикация

1978-01-13—Подача