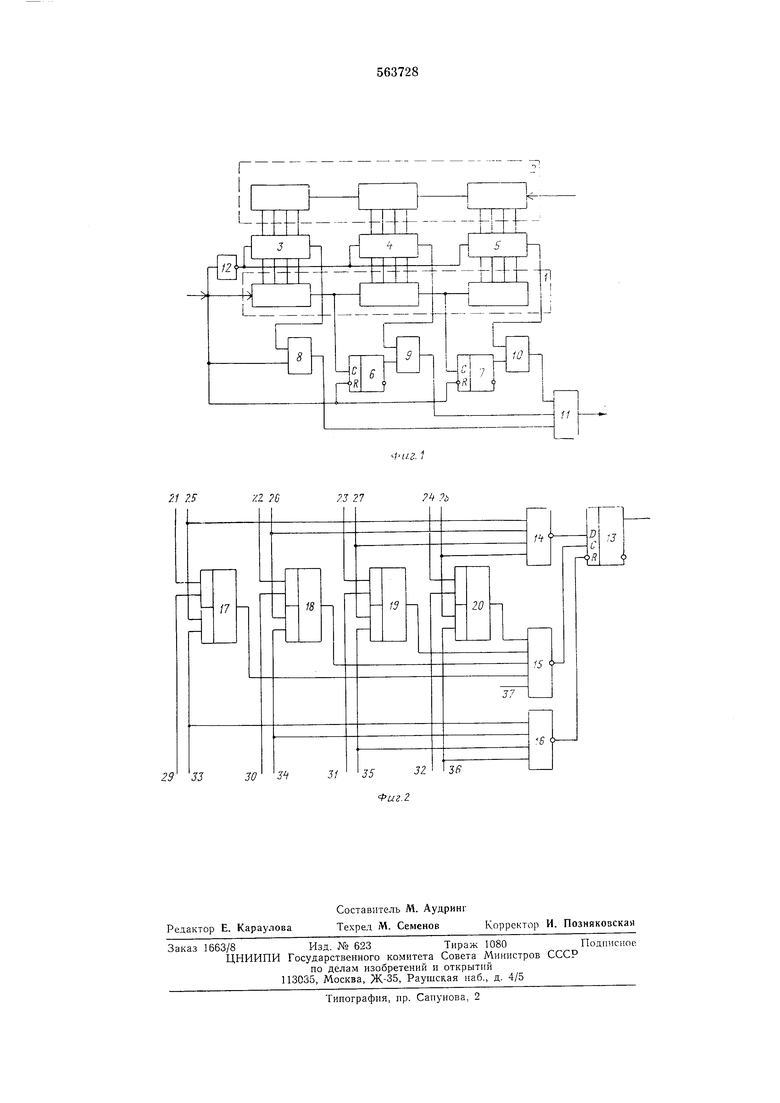

обозначены управляющие входы одного из блоков сравнения, подключенные к единичным входам декад счетчика 2, индексами 25- 28 - управляющие входы, подключенные к нулевым входам декад счетчика 2, индексами 29-32 - управляющие входы, подключенные к единичным входам декад делителя частоты 1, индексами 33-36 - управляющие входы, подключенные к нулевым входам декад делителя частоты 1, индексом 37 - тактирующий вход блока сравнения. Тактирующие входы блоков сравнения объединены и подключены через инвертор 12 к входу первой декады делителя частоты 1, выходы элементов И-НЕ 14, 15, 16 связаны в каждом блоке сравнения соответственно с D-, С-, 7 -входами управляющих триггеров 13, единичные выходы которых связаны с управляющими входами элементов И 8, 9, 10, информационные входы которых подключены: для первой декады - к входу первой декады делителя частоты 1, для последующих - к единичному выходу триггеров 6, 7, тактирующие С-входы последних подключены к входам своих декад делителя частоты 1, а установочные инверсные / -входы объединены и связаны с входом первой декады этого делителя. Выходы элементов И 8, 9, 10 подключены к входам трехвходового элемента ИЛИ 11.

Работа управляемого делителя частоты заключается в формированни на выходе элемента ИЛИ 11 выходной импульсной последовательности, среднее число импульсов в которой за каждый цикл заполнения делителя частоты 1 определяет выходную частоту устройства /вых. Установка по коэффициенту деления вводится в счетчик 2 в виде числа управляющих импульсов Лу, равного количеству импульсов на выходе устройства на каждые 10 импульсов входной частоты (я - число декад управляемого делителя частоты).

Управление сводится к тому, что управляющий триггер 13 каждого блока сравнения открывает элемент И 8 (9, 10) для прохождения входной частоты /вх на один из входов элемента ИЛИ 11 на переднем фронте первого импульса, поступающего на декаду делителя частоты 1 после каждого ее переполнения (появление сигнала на выходе элемента И-НЕ 16) и закрывает элемент И 8 (9, 10) после поступления на вход указанной декады числа импульсов, равного числу, записанному в соответствующую декаду счетчика 2 (исчезновение сигнала на выходе элемента И-НЕ 15). Во избежание сбоев в схеме, связанных с задержкой на прохождение сигналов в декадах делителя частоты, сброс управляющего триггера 13 производится на заднем фронте импульса входной частоты /вх благодаря наличию инвертора 12 и тактированию блоков сравнения по входам 37. С целью избежания

сбоев при нулевом значении числа уставки в одной или нескольких декадах счетчика 2 введена блокировка, запрещающая срабатывание управляющего триггера 13 в этом случае (отсутствие сигнала на выходе элемента И-НЕ И).

Таким образом, элемент И 8 (9, 10) для

каждой декады в момент прохождения через

эту декаду десятого импульса всегда закрыт,

что исключает совпадение импульсов разных

декад на входах элемента ИЛИ 11.

Таким образом, на выходе устройства образуется выходная импульсная последовательность, которая характеризуется частотой.

/вых /вх + TTiT + + Г

10

102

где Ni,Nz,...,Nn - составляющие числа уставки Лу, записанного в десятичном коде в л-декадном счетчике 2.

Формула изобретения

1.Управляемый делитель частоты, содержапщй блоки сравнения, управляющие входы

каждо1-о из которых соединены с выходами декад делителя частоты и счетчика, триперы и элементы И, отличающийся тем, что, с целью уменьшения неравномерности следоианим выходных импульсов, Б него введен элемент Р1ЛИ, входы которого подключены к выходам элементов И, уи)авляющий вход каждого из которых соединен с выходом соответствующего блока сравнения, информационный

вход первого элемента И соединен с входом первой декады делителя частоты, а информационные входы других элементов И - с единнчными выходами триггеров, тактирующие входы которых подключены к входам соответствующих декад делителя частоты, а установочные входы объединены и подключены к входу первой декады делителя частоты.

2.Делитель частоты по п. 1, отличающийся тем, что каждый блок сравнения содержит управляемый триггер, логические элементы И-НЕ и 2И-ИЛИ, управляющие входы которых подключены поразрядно к единичным и нулевым выходам декады делителя частоты и счетчика, а выходы через один из логических элементов PI-НЕ - к С-входу управляемого триггера, D- и .R-входы которого подключены к выходам других логических элементов И-НЕ, входы которых подключены к управляемым входам логических элементов 2И-ИЛИ.

Источники информации, принятые во вннмание при экспертизе

1. Натент Япоиии Л 47-51535, кл. 98 (5) С 32, 1972.

2. Патент ФРГ № 1231300, кл. 21а 36/22, 1966.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1390595A1 |

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1322223A1 |

| Цифровое фазосдвигающее устройство | 1984 |

|

SU1241148A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU957404A2 |

| Цифровой термометр | 1984 |

|

SU1190209A1 |

| Преобразователь кодов | 1987 |

|

SU1444957A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU993428A1 |

| Управляемый делитель частоты следования импульсов | 1981 |

|

SU1008911A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство для определения среднего | 1980 |

|

SU877563A1 |

PJ S

a. c

ЛТ 27

29 3330

fi b

Авторы

Даты

1977-06-30—Публикация

1975-06-09—Подача