Изобретение относится к устройствам импульсной и цифровой. те,хники и может быть использовано в цифровых измерительных приборах и программных задающих устройствах для получения интервалов времени.

Известен утфавляемый делитель частоты следования импульсов, содержащий счетчик импульсов, элементы И и управляющий триггер .l .

Недостаток данного устройства - н высокая точность деления.

Наиболее близким к предлагаемому является управляемый делитель частоты следования импульсов, содержащий блоки сравнения, управляющие входы каждого из которых соединены с. выходами декад делителя частоты и счетчи, ки, триггеры и элементы И, элемент ИЛ входы которого подключены к выходам элементов И, управляющий вход каждого из которых соединен с выходом соответствующего блока сравнения, информационный вход первого элемента И соединен с входом первого делителя частоты, а информационные входы других элементов И - с единичными выходами триггеров, тактирующие входы которых подключены к входам соот ветствующях декад делителя частоты, а установочные входы объединены и подклрчены к входу первой декады делителя частоты 2 .

Недостатком известного устройства 5голяется низкая точность из-за неравномерности следования импульсов в выходной последовательности.

Цель изобретения - повыщение точности деления.

Поставленная цель достигается тем, что в управляемый делитель частоты следования импульсов, содержащий делитель частоты, N -разрядный счетный блок, выходы которого соединены с соответствующими входами N -разрядного блока сравнения, выходы (N-1 разрядов которого соединены с первым

; уходами соответствующих (N -1) триггеров, выходы котчзрых соедийены с первыми входами соответствующих элементов И, введен формирователь импульсов, вход которого соединен с выходом последнего разряда N -разрядного блока сравнения, а выход - с вторыми входами (М-1) триггеров и установочными входами М -разрядного счетного блока, при этом вход делителя частоты 1соединен со счетным входом первого

разряда N -разрядного счетного блока, счетные входы остальных разрядов которого соединены с выходами соответствующих элементов И, вторые входы

которого соединены с соответствующими выходами делителя частоты.

При этом каждый разряд N -раэрадного блока сравнения содержит демультиплексор, первая группа входов

которого ясвляется входами данного разряда, вторая группа входов соедирена с выходами переключателя, а выход 5гвляется выходом данного разряда W -разрядного блока сравнения.

{

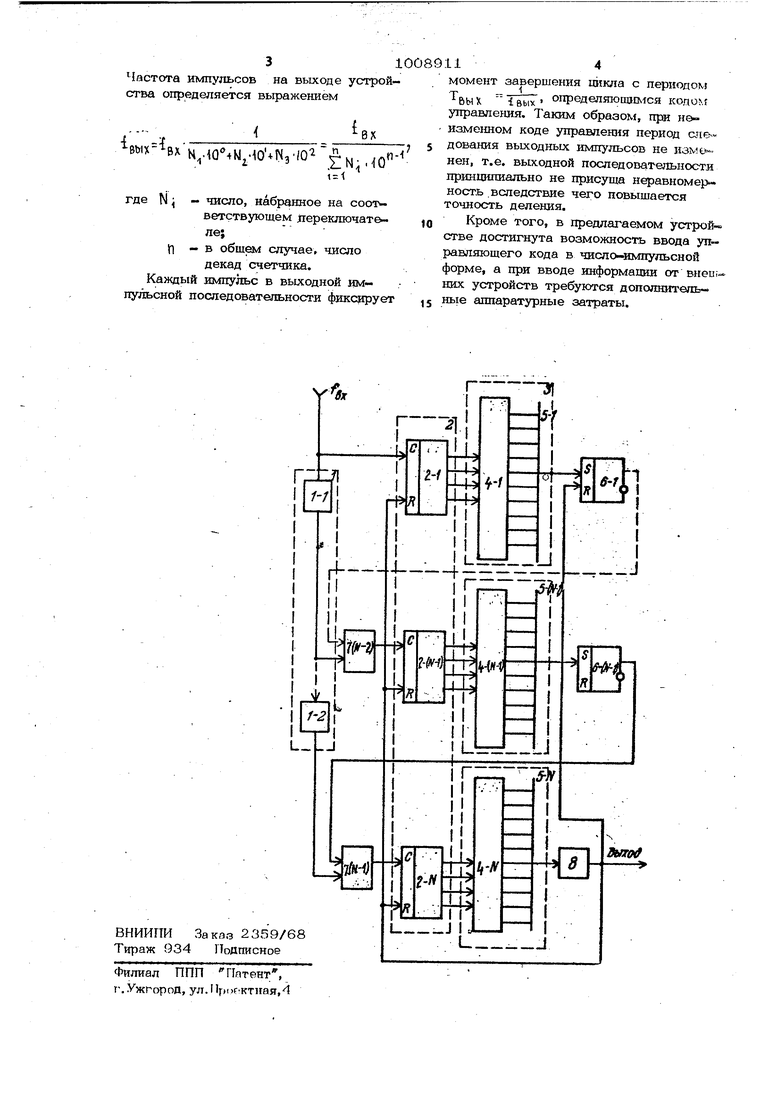

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит делитель 1 частоты, включающий в себя декады (1-1) - 1 -(N-1), N -разрядный счетный блор 2, включающий в себя счетчики (2-1) - (2-М ), N -разрядный блок 3 сравнения, включающий в себя демуяьтиплексоры (4-1) - (4-Л1) и зтереключатели (5-1) - ( 5 - W ), триггеры (6-1 - 6-(N-l), элементы И :7 -(N-2) -..7 - ( fj -1) и фор мирователь 8 импульсов.

Устройство работает следующим образом.

Делитель 1 обеспечивает на BbLxo- 4§

дах декад частоты

счет-

чик (2-1) заполняется импульсами частоты i gx до тех пор, пока их количество не совпадет со значением десятичной цифры, набранной на переключателе соответствующего блока 3. В этот момент выходной импульс блока 3 устанавливает триггер (6-1) в единичное состояние, после чего импульсы с частотой „j. /10 через открытый элемент И поступают в счетчик (2-2). Аналогично выщеолисанному после поступления в счетчик 2-(N -1) числа импульсов, равного набранному на переключателе 5 - ( и -1), в единичное состояние устанавливается триггер 6(К-1). Процесс продолжается до появления выходного сигнала на последнем разряг е блока 3, поступающего на формирователь 8. Последний формирует короткий выходной импульс, который устанавливает счеттаки блока 2 и триг. геры (6-1) - 6 (К -1) в нулевое

состояние. На этом цикл работы устройства заканчивается. Далее выщеописанJU ie процессы циклически повторяются. Частота импульсов на выходе устрой ства определяется выражением ( .iQ%M.(o4N3/0 |..,Qn - число, набранное на соо-гветствующем лереключат&ле;- в обшем случае, число декад счетчика. Каждый импульс в выходной импульсной последовательности фиксируе момент завершения шгкла с периодом ТВЫХ ВЫК Твых определяющимся кодом управления. Таким образом, при и©изме1шом коде управленз1Я период дования выходных импульсов не , т.е. выходной последовательности принципиально не присуща неравномер ность .вследствие чего повышается точность деления. Кроме того, в предлагаемом устрой- стве достигнута возможность ввода управляющего кода в число-импульсной форме, а при вводе информации от внеи;них устройств требуются дополни1 ель-Hbie аппаратурные затраты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Устройство для измерения отношения частот | 1988 |

|

SU1661664A1 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU843245A1 |

| Реле времени | 1984 |

|

SU1190358A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| Цифровое фазосдвигающее устройство | 1984 |

|

SU1241148A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий делитель частоты, N -разрадный счетный блок, вьгходы которого соединены с соответствующими вхо- дами N -разрядного блока сравнения, выходы ( N -1) разрядов которого со&|динены с первыми входами соответствуюпдах ( N -1). триггеров, которых соединены с первыми Тзходамза соответствующих элементов И, отличающийся тем, что, с цепью повышения точности, в него введен формирователь импульсов, вход которого соединен с выходом последнего разряда N -li разрядного блока сравнения, а выход - с вторыми входами ( N -1) трш геров и установочными входа1«(И N -раэ Р5здного счетного блока, при этом вход делителя соединен со счетипым входом первого разряда N - разрядно-1 1Х)счетного блока, счетные входы ооггальных разрядов которого соедицены с вь содами соотвег ггвуюпщх элемеотов И вторые входы которых соединены с соответствуюпшмн выходами делителя частоты. 2. Депхггель по п. 1, отличающий с я тем, что каждый разряд разрядного блока сравнення содержит демультиплексор, первая rpyntib входов которого является входами да1 кого разряда, вторая группа входов соединена с вЫхода ф переклю теля, а-выход является выходом данного раэ р5ща N -ра:фядного блока сравнения.. 00 со

р.

31

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для удаления штопок из сахарных голов | 1928 |

|

SU12313A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР , № 563728, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-03-30—Публикация

1981-12-25—Подача