(54) МНОГОКАНАЛЬНАЯ СИСТЕМА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсная система передачи двоичных сигналов | 1978 |

|

SU758533A1 |

| Многоканальная система передачи двоичной информации с временным уплотнением | 1975 |

|

SU559409A1 |

| Многоканальная система передачи двоичной информации с временным уплотнением | 1976 |

|

SU661829A2 |

| Система передачи дискретной информации | 1987 |

|

SU1518886A1 |

| Кодирующее устройство | 1985 |

|

SU1329572A1 |

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДВОИЧНЫХСИГНАЛОВ | 1971 |

|

SU313302A1 |

| ПРИЕМОПЕРЕДАТЧИК ВОЛОКОННО-ОПТИЧЕСКОЙ ЛИНИИ СВЯЗИ | 1989 |

|

RU2221342C2 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛАМ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1994 |

|

RU2079855C1 |

| СИСТЕМА ЦИФРОВОГО ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1993 |

|

RU2103839C1 |

I

Изобретение относится к технике связи, может использоваться в системах передачи дискретной информации.

Известна многоканальная система передачи дискретной информации, содержащая на передающей стороне в каждом из кана-лов кодирующий преобразователь, состоящий из поспедоватепьно соединенных формирователя сигнала значащего момента модуляции (ЗММ); шифратора и регистра, другой вход которого соединен с выходом формирователя сигнала значащего момента модуляции, соответствующий вход регистра соединен с дополнительным выходом формирователя сигнала значащего момента модуляции, причем выход регистра кодирующего преобразователя канала Соединен со входом блока , объединения каналов, управляющие входы которого и управлякнцие входы каждого кодирующего преобразователя соединены с соответст вующими выходами распределителя, вход которого соединен с выходом генератора импульсов, а на приемной стороне в из каналов - декодирующий преобразоватепь, состоящий из последовательно соединенных регистра и дешифратора, другой вход которого соединен с выходом блока выделения сигнала старта , один вход которого соеданен с выходом знакового разряда регистра, а другой - с выходом триггера; при этом вход регистра декодирующего преобразователи первого ка- нала соединен с выходом блока разделения каналов, управляющие входы которого и управляющие входы каждого декодирующего преобразователя соединены с соответствующим Выходом распределитепя 13

Однако известная многоканальная система передает информацию с небольщой скор остью.

Цель изобретения - повыщение скорости передачи информации. .

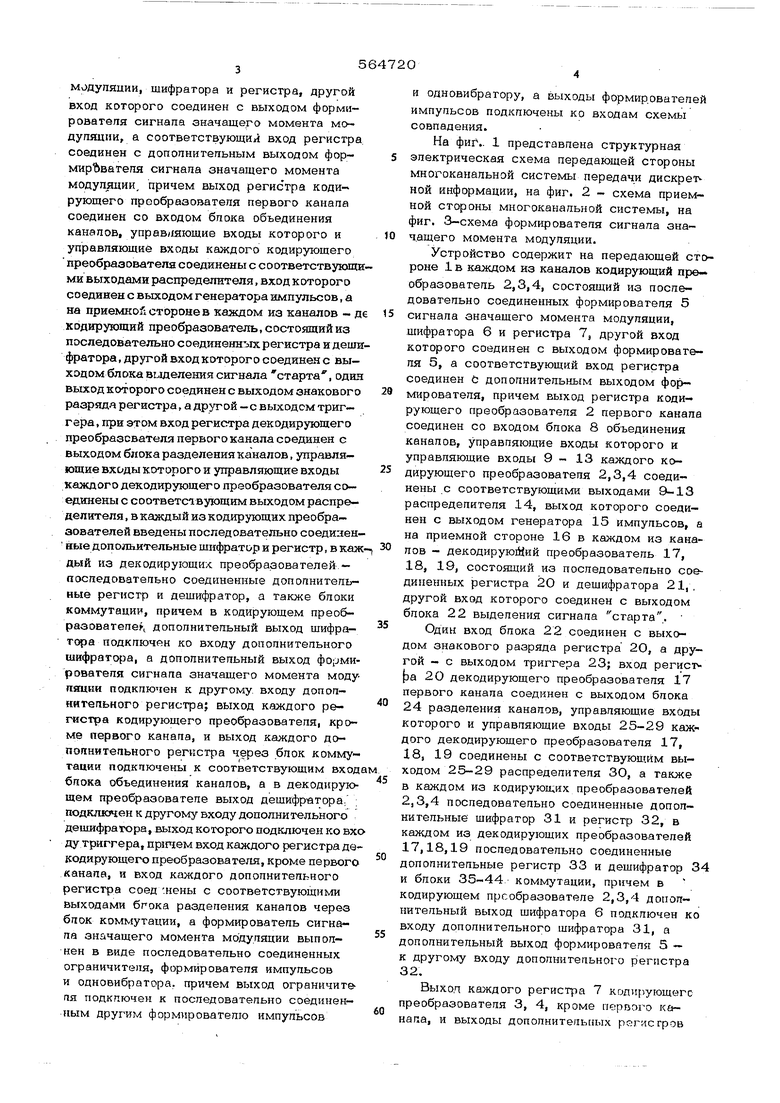

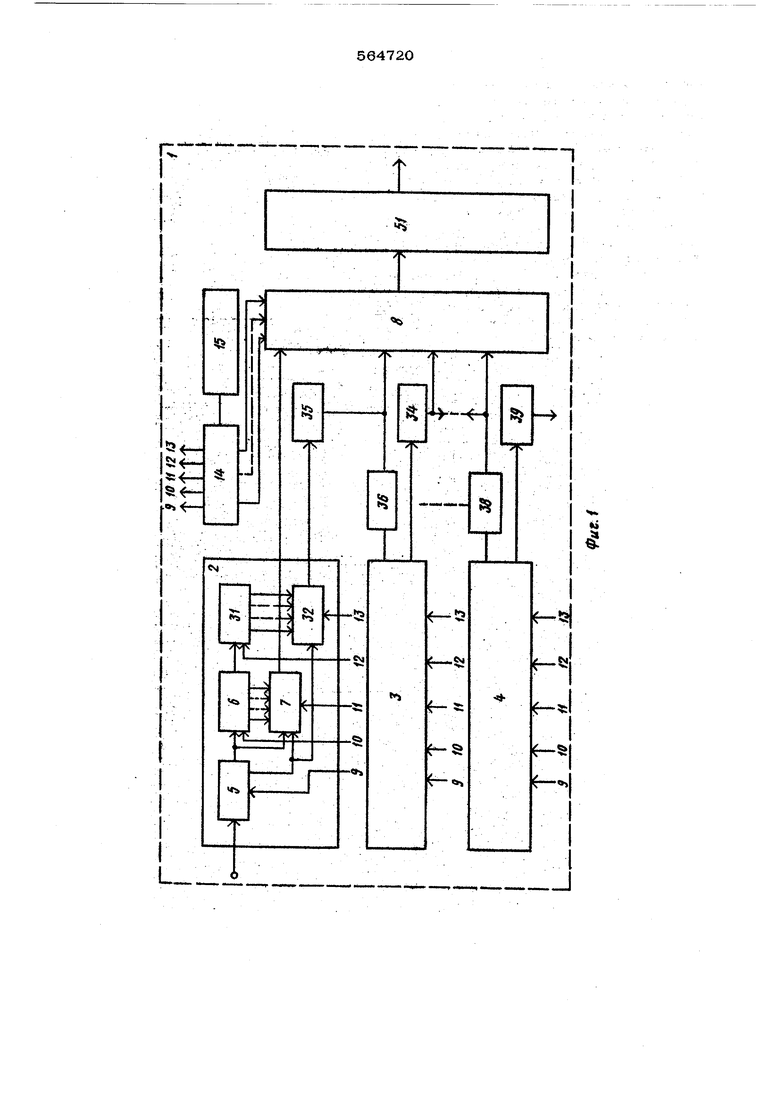

Для этого в многоканальную систему передачи дискретной информации содержащую на передающей стороне в каждом из каналов кодирующий преобразователь, состоящий из последовательно соединенных формирователя сигнала значащего момента модуляции, шифратора и регистра, другой вход которого соединен с выходом формирователя сигнапа значащего момента мо дупящпи, а соответствующий вход регистра соединен с допоянитепьным выходом формирйватепя сигнапа значащего момента модуляции, причем выход регистра коди рующего прообрааоватепя первого канапа соединен со входом блока объединения каналов, управ/гаюшие входы которого и управляющие входы каждого кодирующего преобразователя соединены с соответствующи ми выходами распределителя, вход которого соединен с выходом генератора импульсов, а на приемно/г стороне в каждом из каналов - д кодирующий преобразователь, состоящий из последовательно соединеннглх регистра и деши фратора , другой вход которого соединен с выходом блока виделения сигнала старта, один выход которого соединен с выходом знакового разряда регистра, а другой -с выход см триггера , при этом вход регистра декодирующего преобразователя первого канала соединен с выходом блока разделения каналов, управляющие входы которого и управляющие входы каждого декодирующего преобразователя соединены с соответсавующим выходом распределителя , в каждый из кодирующих преобразователей введены последовательно соедилен ные дополнительные шифратор и регистр, в каж дый из декодирующих преобразователей - последовательно соединенные дополнительные регистр и дешифратор, а также блоки коммутации, причем в кодирующем преобрааователе 1 дополнительный выход шифратора подключен ко входу дополнительного шифратора, а дополнительный выход форми рователя сигнала значащего момента моду ляции подключен к другому входу дополнительного регистра; выход каждого регистра кодирующего преобразователя, кроме первого канала, и выход каждого дополнительного регистра через блок комму тации подключены к соответствующим вхо блока объединения каналов, а в декодирук щем преобразователе выход дешифратора. подключен к другому входу дополнительного дешифратора, выход которого подключен ко вх ду триггера, пршхем вход каждого регистра де кодирующего преобразователя, кроме первог канала, и вход каждого дополнительного регистра соед .нены с соответствующими выходами бгока разделения каналов через блок коммутации, а формирователь сигнала значащего момента модуляции выполнен в виде последовательно соединенных ограничителя, формирователя импульсов и одновибратора. причем выход ограничите ля подключен к последовательно соединенным другим формирователю импульсов И одноаибратору, а выходы формирователей импульсов подключены ко входам схемы совпадения. На фиг.. 1 представлена структурная электрическая схема передающей стороны многоканальной системы передачи дискрет ной информации, на фиг. 2 - схема приемной стороны многоканальной системы, на фиг. 3-схема формирователя сигнала значащего момента модуляции. Устройство содержит на передающей стороне 1 в каждом из каналов кодирующий преобразователь 2,3,4, состоящий из последовательно соединенных формирователя 5 сигнала значащего момента модуляции, .шифратора 6 и регистра 7, другой вход которого соединен с выходом формирователя 5, а соответствующий вход регистра соединен С дополнительным выходом формирователя, причем выход регистра кодирующего преобразователя 2 первого канала соединен со входом блока 8 объединения каналов, управляющие входы которого и управляющие входы 9 - 13 каждого кодирующего преобразователя 2,3,4 соединены ,с соответствующими выходами 9-13 распределителя 14, выход которого соединен с выходом генератора 15 импульсов, а на приемной стороне 16 в каждом из каналов - декодируюйий преобразователь 17, 18, 19, состоящий из последовательно соединенных регистра 20 и дешифратора 21, , другой вход которого соединен с выходом блока 22 выделения сигнала старта, Один вход блока 22 соединен с выходом знакового разряда регистра 20, а другой - с выходом триггера 23; вход региср а 20 декодирующего преобразователя 17 первого канала соединен с выходом блока 24 разделения каналов, управляющие входы которого и управляющие входы 25-29 каждого декодирующего преобразователя 17, 18, 19 соединены с соответствующим выходом 25-29 распределителя 30, а также в каждом из кодирующих преобразователей 2,3,4 последовательно соединенные дополнительные шифратор 31 и регистр 32, в каждом из декодирующих преобразователей 17,18,19 последовательно соединенные дополнительные регистр 33 и дешифратор 34 и блоки 35-44 коммутации, причем в кодирующем преобразователе 2,3,4 дополнительный выход шифратора 6 подключен ко входу дополнительного шифратора 31, а дополнительный выход формирователя 5 - к другому входу дополнительного регистра 32. ВыХ.ол каждого регистра 7 копирующего преобразователя 3, 4, кроме первого канала, и выходы дополнительных регистров 32 через баоки 35-39 подкяючены к coco ответе гвующим входам бпока 8, а в дек дирующем преобразователе 17,18,19 выход дешифоатора 21 подключен к другому входу дополнительного дешифратора 34 выход которого подключен ко входу тригге ра 23, причем вход каждого регистра 20 декодирующего преофазователя 18, 19, кроме первого канала, и вход каждого дополнительного регистра 33 соединены с соответствующими выходами блока 24 через блоки 4О-44, а формирователь 5 выпопнен в виде последовательно соединенных ограничителя 45, формировагепя 46 импульсов и однорибратора 47, причем выход ограничителя подключен к последовательно соединенным другим формировате лю 48 импульсов и одновибратору 49, а выходы формирователей 46,48 подключены к входам схемы 50-совпадения, и двоичный синхроканал 51. Работа устройства поясняется для мето да передачи дискретной информации скольг зящий индекс с подтверждением (СИП). При статическом состоянии ДС на входе кодирукэшего преобразователя 2,3,4 до момента времени.на формирователь 5 nt ступает отрицательный потенциал биполяр ного ДС. Полярность сигнала соответству-/ ет значению передаваемого ДС. Так, например, при ix tjf на вход поступает посылка отрицательной попярности, соответствующей логич-ескому нулю. На выходе формирователя 5 при этом формируется однополярный ДС. На распределитепь 14 с генератора 15 поступает последователь ность тактовых импульсов (ТИ). На последовательные входы регистров 7 и 32 до момента i - i подается сигнаг О, который продвигается по регистрам 7 и 32, и на выходах их формируется последовател ность подтверждения состояния ДС, До йомента BpeiOieHH передаются нули, т. е. импульсы отсутствуют. При изменении знака на входе канапа на выходе формирователя 5 формируется импульс ЗММ, который служит управляющим сигналом для работы шифраторов 6 и 31 и для записи стартового импульса кодовой комбинации в регистр На выходах шифраторов 6, 31 формируе .ся кодовая комбинация, первый символ KOJ- торой несет информацию о знаке ЗММ, а совокупность Остальных символов представляет собой двоичный код числа, соответствующего временному попожению ЗММ или номеру зоны, в которой формируется ЗММ. Временные зоны привязаны, т. е. Сфазированы с началом периодов импупьсов считывания, которые считывают информацию с регистров 7,32 в синхронные кан лы. Шифраторы 6,31 построены так, что шифратор 6 выдает в регистр 7 число, соответствущее номеру зоны по грубой шкале, например, для трехразрядного шифратора от первой зоны до восьмой. Шифратор 31, например, на три разряда, формирует код числа точной щкапы от первой до восьмой части каждой зоны грубой шкалы. Кодовые комбинации, записанные в момент появления ЗММ в регистр 7 и дополнительный регистр 32, несут, таким образом, информацию о положении во времени ЗММ относительно периода синхронного канала связи, так как скорость в канале равна скорости продвижения, и считыванияинформации с регистра 7, и при организации канала передачи данных с по вышенной скоростью (или с повышенной точностью) i можно использовать информацию дополнительного регистра 32, передавая ее в аналогичный синхронный канал. Когда по всем каналам устройства необходимо передавать сигргапы с одинаковой скоростью (не выше предельной для каждого канала), блоки 35,38, включенные в основные выходы кодирующих преобразователей 2,3,4 и блоки 41,43, вклк ченные в основные входы декодирующих преобразователей (32 и 36), замкнуты, а блоки 35,37, 39, включенные в дополнительные выходы кодирующих преобразовате- лей 2,3,4 и блоки 40,42,44, включенныев дополнительные входы декодирующих преобразователей 17,18,19, paзo ucнyты. При этом сигнал с основного выхода кодирующего преобразователя 2,3,4.через блок 8, двоичный синхроканал 51 и блок 24 проходит на основной вход соответствующего декодирующего преобразователя 17,18,19. Синхронность и синфазность работы рас пределителей 14,30 обеспечивается системой синхронизации (не показанной на чертеже) известными методами. При организации канала для передачи двоичного сигнала с повышенной скоростью, например по первому канапу, -образованноAiy кодирующим и декодирующим преобразоватепями 2,17, выключают блоки 36 и 41 и включаю,т блоки 35 и 4О. При этом информация с дополнительного кодирующего преобразователя 2 попадает через блок 35 на вход второго канала блоков 8,24 и с выхода последнего через бпок 40 - на допопннтепьный вход декодирующего преобразоватедя 17. Таким образом, повысив качество информации о времени возникновё- ния ЗММ,МОЖНО передавать двоичные сипкапы с повышенной скоростью. Индивидуальные синхронные сигналы от каждого коналоч блока 24 поступают на ооновнрй и допопнйгепьный входы индивидуапьного дшсодирующего j преобразователя, т.е. на поспедоБагельныё ; входы регистра 20 и дрпблнитепьногр регистра 32 и записываюгсй в эти регистры импульсами продвижения, которые синхронны и синфааны с ймпуп сами считывания на передаче. Работой распредепитепя 30 приемной стороны 1 кёгок даальной 1 системы передачи янскрвт Нрййнформа11ии управляют тактовые ймпульсы от генераторного оборудования (на Hsp-ft не показано).

В исходном режиме (до момента е . мёШи i) состояние триггера 23 совпадает со аначением знакового разряда регистра . 20. На выходе бпгока 22 сигнал отсутствует. Двоичный сигнал на выходе триггера 23 -сохраняетг статическое состояние (например нулевое). При появлении в зна.ковом разряде регистра 2О стартового импульса (в данном случае единицы) на выходе гблока.;22 оказывается импульс, запускающий дешифраторы 21 и 3.4. В дешифраторе 21 восст навпивается номер абны кодирования по грубой шкапе, в допоанительном дешифраторе 34 - номер соответствующей части (в данном случае одной из восьми частей), каждой зоны грубой шкаты. По окончании дешифрации управляю,щий сигнал поступает на вход триггера

23, на выходе которого формируется двоичный -сигнал.

Формирователь работает следующим обра зом. На вход ограничителя 45 подается

биполярный двоичный сигнал с кодировкой погических единиц положительной полярностью и логических нулей отрицательн полярностью. На выходе ограничителя ,45 этот.сигнал ограничивается до величин, не превышающих допустимых значений для входов формирователей 46,48. Формироваtema 46,48 работают таким образом, что при отсутствии информационного сигнала на входах и выходах формируется потенциал нуля

Если на входе ограничителя 45 сигнал отсутствует, например, | в случае обрыва линии или не передается, то на выходах формирователей 46,48 формируются одновременно потенциалы нуля, и схема 50 вырабатывает сигнал логической единицы, который соответствует сигналу пропадание двоичного сигнала и может использоваться в системах сигнализации и устройствах блокировки, которые в. случаях пропадания сигнала на входе вырабатываю1 на передаче заранее обуславливаемый сиг нал. Одновибраторы 47и 49, срабатывая от заднего фронта импульсов,-. поступак щих на их входы,, выдают импульсы, соответствующие изменению полярности входного сигнала - значащего момента модул ЦЙИ.

На выходах одновибраторов 47,49 формируются импульсы, соответствующие сигналам ЗММ единиц и ЗММ нулей . Эти сигналы необходимы для работы кодирующих преобразователей 2,3,4.

Формула изобретения

вначашего момента модуляции подключен к другому входу допопнитепьного регистра, при этом выход каждого регисщА хадиру1р Шдго преобразователя, кроме | Первого кака па, и выход каждого дЬпопиятепьногррёгис ра ч€1реабпок коммутации подключены к соответствующим входам блока рбьедине ния каналов, а а декодирующем преоС азо вателе выход дешифратора подключен к другому входу дополнительного деипфрато ра, выход которого подключен ко входу триггера, причем вход каждого регистра декодирующего преобразователя, кроме пер вого канала, и вход каждого дополнитель ного регистра соединены с соответствукн шими выходами блока раэделенна каналов через блок коммутации.

Источники информации, принятые во вни-, мание при экспертизе:

fuz.3

Авторы

Даты

1977-07-05—Публикация

1975-07-04—Подача