Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации без обратной связи.

Целью изобретения является повышение скорости передачи информации.

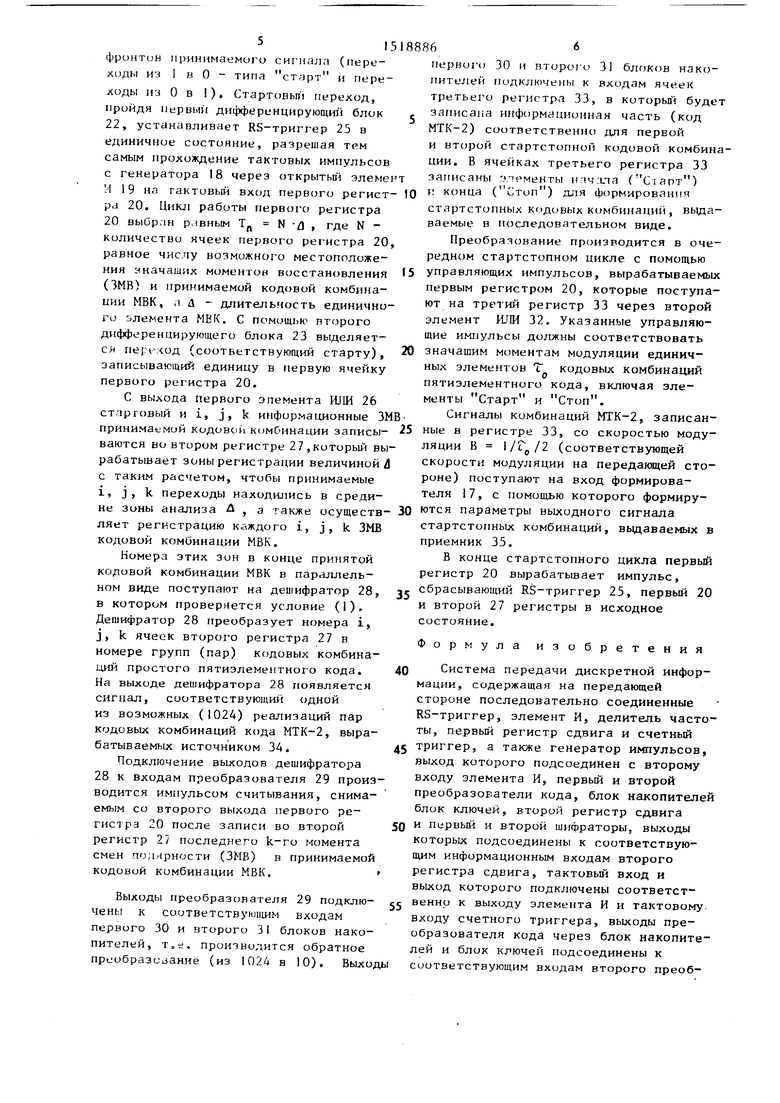

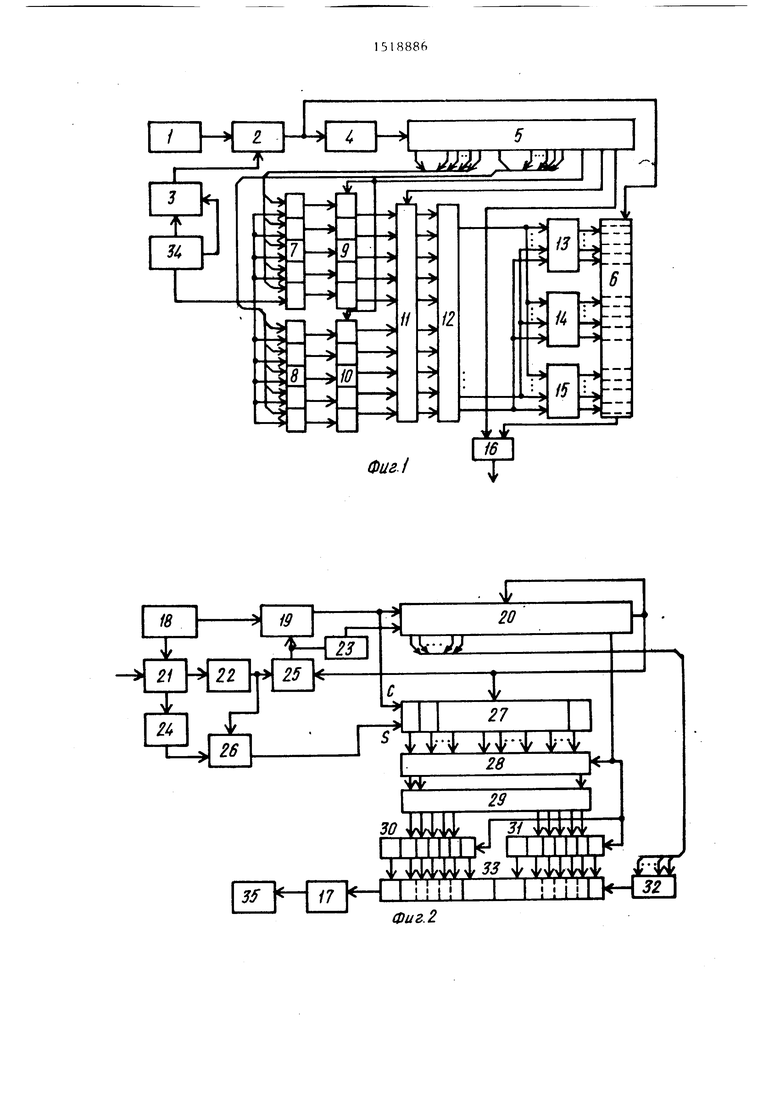

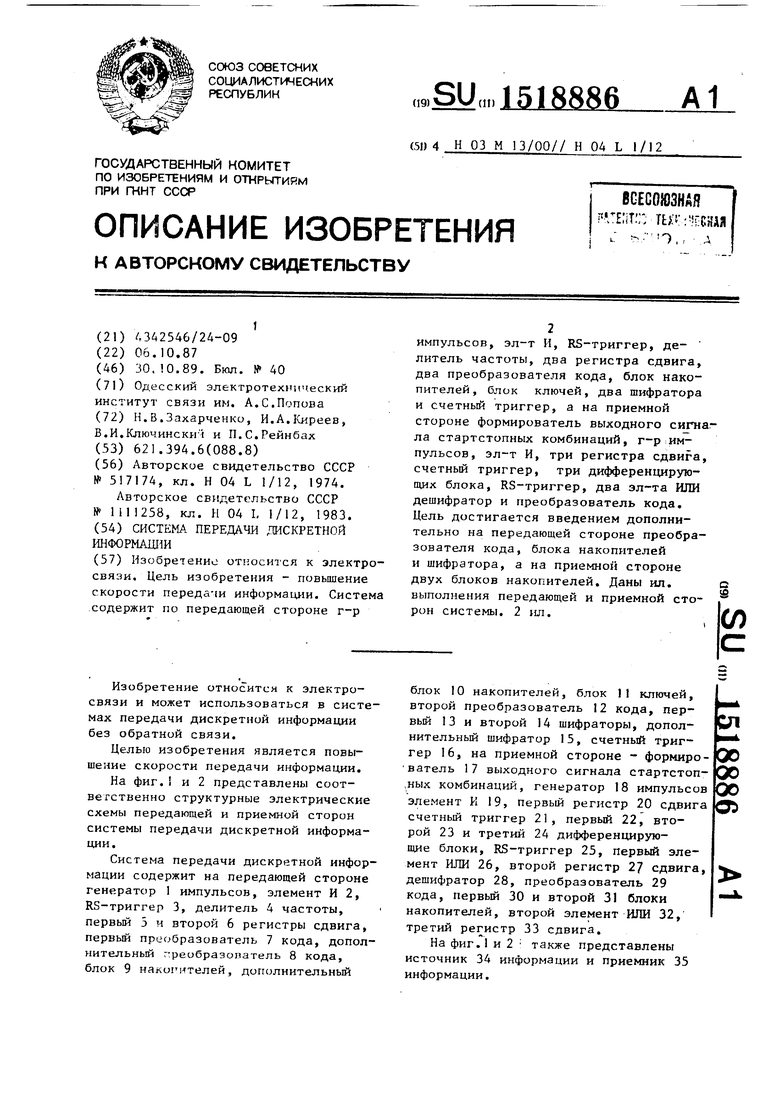

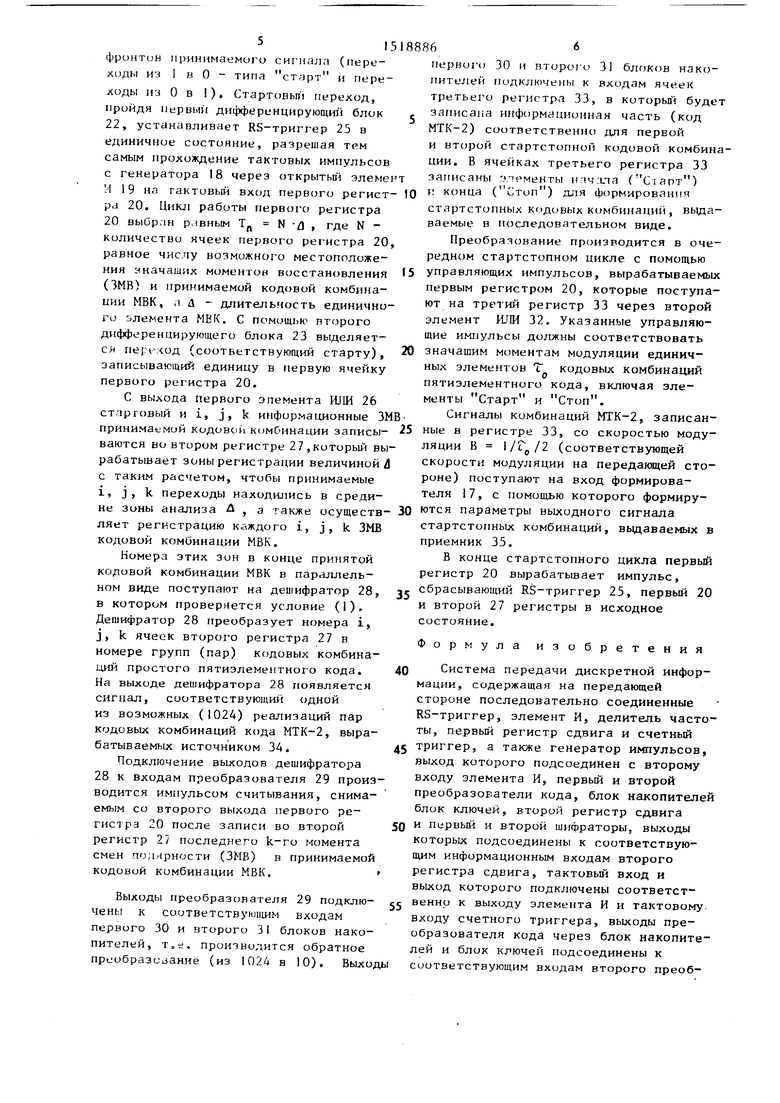

На фиг. и 2 представлены соответственно структурные электрические схемы передающей и приемной сторон системы передачи дискретной информации.

Система передачи дискретной информации содержит на передающей стороне генератор I импульсов, элемент И 2, RS-триггер 3, делитель 4 частоты, первый 5 и второй 6 регистры сдвига, первый преобразователь 7 кода, дополнительный Г реобразонатель 8 кода, блок 9 накопителей, дополнительный

блок 10 накопителей, блок 11 ключей, второй преобразователь 12 кода, первый 13 и второй 14 шифраторы, допол- нительньй шифратор 15, счетный триггер 16, на приемной стороне - формиро- ватель 17 выходного сигнала стартстоп- ,ных комбинаций, генератор 18 импульсов элемент И 19, первый регистр 20 сдвига счетный триггер 21, первый 22, второй 23 и третий 24 дифференцирую- шле блоки, RS-триггер 25, Первый элемент ИЛИ 26, второй регистр 27 сдвига, дешифратор 28, преобразователь 29 кода, первый 30 и второй 31 блоки накопителей, второй элемент ИЛИ 32, третий регистр 33 сдвига.

На фиг.1 и 2 также представлены источник 34 информации и приемник 35 информации.

Система передачи дискретной информации работает следующим образом.

Источник 34 на передающей стороне (фиг.1) определяет начало и конец передаваемого блока данных. С момента формирования источником 34 сигнала начало стартстопной комбинации формируется сигнал, разрешающий запуск RS-триггера 3. При этом разрешается Прохождение тактовых импульсов с генератора 1 через открытый элемент И 2 и делитель 4 на вход первого регистра 5.

Частота поступающих импульсов ран-

на F 1 -7п где (Г - длительность

О I

элемента простого кода, вырабат1)1ва- емого ИСТОЧ11ИКОМ 34.

Информация в последовательном виде (простой код) вырабатываемая источником 34 с длительностью элемента (Гд/2, поступает одновременно на первьй преобразователь 7 и дополнительный преобразователь 8. Одновременно с на-- чалом работы источника 34 первый регистр 5 вырабатывает две серии импульсов, поступающие по тактовым входам соответственно первого 7 и дополнительного 8 преобразователей. Эти импульсы (импульсы регистрации) соответствуют средним частям принимаемых единичных элементов.

Цикл работы первого регистра 5 соответствует двум стартстопным ;икла вырабатываемым источником 34.

С Помощью первого 7 и дон(лнитель- ного 8 преобразователей осуществляется преобразование элементов последовательного простого кода ц параллель- ный. Элементы параллельного кода соответственно запоминаются н блоке 9 накопителей и диполнительном блоке 10 накопителе.

После приема 1и)следиего элемента кода блока информации,соответствующему второму стартстопному циклу источника 34, очередным тактовым импу;)ьсом первого регистра 5 разрещается раб(;та блока 11 ключей. При этом информация с блока 9 накопителей и дополнительного блока 10 накопителе в пара1 лельно виде поступает на второ преобразова- 12, в котором каждой паре комбинаций просгого пятиэлементного кода присБа 1Еается свой номер. В результате с ,bi j второго Преобразовател 12 1роисходит доип1фрац 1и нако 1ительны

КОМбИ1 ацИЙ в одну из ВОЗМОЖ1 ЫХ.

с 1омощью ервого 13 и второго 14 шифраторов и до голнительного шифратора 15 1роизводится преобразование номера пары дешифрованных комбинаций кода МТК-2 в одну из комбинаций много- нозидионного временного i, j, k кода (МВК), где i, J, k - переходы, определяющие Местоположения значащих моментов модуляции (3I-D-I) в формируемом сигнале кодовой комбинации. При этом информация о номере комбинации источника 34, подлежащей передаче, закладывается в сочетании местоположения трех ЗММ сигнала на интервале времени стартстопного цикла. Номера соответствующих смен полярностей (ЗМН) i, j, k, указывающие номера ячеек второго регистра 6, в которые должнь: быть записаны единицы, ог ределяются из условия

А -i + A- j -t- А, k О no mod A

ук

о

(1)

где , , А. определяются параметрами о 1ибок в канале связи и требуемой верностью передачи.

С выхода элемента И 2 тактовые импульсы с частотой следования F I/Л поступают на тактовый вход второго регистра 6 (Д - единичный элемент, используемый при формировании символов МВК в кодовых словах). Из возможных реализаций выбираются только те, которые удовх етворяют условию (I). При этом информация в виде сочетания переходов последовательно считывается со второго регистра на тактовый вход счетного трип ер 16. Пачало каждого цикла формируемого сигнала МВК отмечается импульсом по установочному входу счетного триггера 16, снимаемого с первого регистра 5. В канал связи передаются старт- стопные кодовые комбинации трехэлементного многопозиционного временного кода с постоянным числом ЗММ i, j, k, местоположение которых удовлетворяет условию (1)о

Информация из канала связи поступает на счетный триггер 21 (фиг.2),. в котором осуществляется временная привязка фронтов принимаемых единичны элементов к импульсам генератора 18, работающего с частотой 1/Д. С помощью первого 22 и третьего 24 дифференцирующих блоков производится выделение

фронтин принимаемого сш пала (переходы из 1 и О - типа старт и переходы из О в ). Стартовьп переход, пройдя Первый дифференцирующш блок 22, устанавливает RS-триггер 25 в единичное состояние, разрешая тем самым прохождение тактовых импульсов с генератора 18 через открытьц1 элеме И 19 на тактовый вход первого регист рл 20. Цикл работы первого регистра 20 выбран равным Т N -Д , где N - количество ячеек первого регистра 20 равное числу возможного местоположения аначашях моментов восстановления (ЗМВ) и принимаемой кодовой комбинации МВК, .1 Л - длительность единичного элемента МЕК, С помощью второго дифф ipeнциpyющeгo блока 23 выделяется переход (соответствующий старту), записывающий единицу в первую ячейку первого регистра 20.

С выхода первого эпемента ИЛИ 26 стартовый и i, j, k информационные З

принимаемой кодовой к JMбинaции записы- ваются во втором регистре 27,который вырабатывает зоны регистрации величиной с таким расчетом, чтобы принимаемые i, j, k переходы находились в средине зоны анализа А , а также осуществ

ляет регистрацию каждого i, j, k ЗМВ кодовой комбинации МВК.

Номера этих зон в конце принятой кодовой комбинации МВК в параллельном виде поступают на дешифратор 28, в котором провернется условие ( 1 ) Дешифратор 28 преобразует номера i, j, k ячеек второго регистра 27 в номере групп (пар) кодовых комбина- 1ЛИЙ простого пятиэлемеитного кода. На выходе дешифратора 28 появляется сигнал, соответствующий одной из возможных (1024) реализаций пар кодовых комбинаций кода МТК-2, вырабатываемых источником 34.

Подключение выходов дешифратора 28 к входам преобразователя 29 производится импульсом считывания, снимаемым со второго выхода первого регистра 20 после записи во второй регистр 27 последнего k-ro момента смен полярности (ЗМВ) в принимаемой кодовой комбинации МВК.

Выходы преобразователя 29 подключены к соитветствуюишм входам первого 30 и второго 3I блоков накопителей, т.е. производится обратное преобразсБание (из 1024 в 10). Выход

31 блоков нако- входам ячеек в которьй буде

ные

первиго 30 и пторогч) пителей 11идключе}1Ы к третьего регистра 33, записана информационная часть (код МТК-2) соответственно для первой и второй стартстопной кодовой комбинции. В ячейках третьего регистра 33 записаны г,лементы МсЧч.чла (Стапт) и конца (Стоп) для формирования

стартстопных кодовых комбинаций, выдаваемые в последовательном виде.

Преобразование производится в очередном стартстопном цикле с помощью управляющих импульсов, вырабатываемых первым регистром 20, которые поступают на третий регистр 33 через второй элемент ИЛИ 32. Указанные управляющие импульсы должны соответствовать значащим моментам модуляции единичных элементов Т кодовых комбинаций пятиэлементного кода, включая элементы Старт и Стоп,

Сигналы комбинаций МТК-2, записан- в регистре 33, со скоростью модуные

ляции В 1/Г-/2 (соответствующей

ные

скорости модуляции на передающей стороне) поступают на вход формирователя 17, с помощью которого формируются параметры выходного сигнала стартстопных комбинаций, выдаваемых в приемник 35.

В конце стартстопного цикла первый регистр 20 вырабатьшает импульс, сбрасывающий RS-триггер 25, первый 20

второй 27 состояние.

регистры в исходное

Формула изо

р е т е и и я

Система передачи дискретной информации, содержащая на передающей стороне последовательно соединенные RS-триггер, элемент И, делитель частоты, первый регистр сдвига и счетный триггер, а также генератор иьшульсов, выход которого подсоединен с второму входу элемента И, первьш и второй преобразователи кода, блок накопителей блок ключей, второй регистр сдвига и первый и второй шифраторы, выходы которых подсоединены к соответствующим информационным входам второго регистра сдвига, тактовьй вход и выход которого подключены соответственно к выходу элемента И и тактовому входу счетного триггера, выходы преобразователя кода через блок накопите ей и блок ключей подсоединены к соответствующим входам второго преоб-

разователя кода, причем R-Плод, S- вход RS-Tpiirrepa, иифеормацлоиньц вход первого преобразователя кода н выход счетного триггера являются соответственно первым и вторым управляющими входами, информационным входом и канальным выходом системы, на приемной стороне - последовательно соединенные счетный триггер, первьй дифференцируюишй блок, RS-триггер, второй дифференцирующий блок и первый регистр сдвига, последовательно соединенные генератор импульсов и элемент И, выход которого подсоединен к тактовому вход Первого регистра сдвига, последовательно соединенные третий дифференцирую- -щий блок, nepBbiii элемент HJDi и второй регистр сдвига, тактовый вход которого подключен к выходу элемента И, после- довательно соединенные третий регистр сдвига и формирователь выходного сигнала стартстопных комбинаций, а также второй элемент И11И, дешифратор и преобразователь кода , входы которого через дешифратор подключены к соответству- Ю11ЩМ выходам второго регистра сдвига, установочньп вход второго регистра сдвига, с)бъединенный с установочным входом первог о pernc j pa сдвига и R-входом RS-триггера, подключен к первому выходу первого регистра сдш га, второй выход которого подсоедияен к считывающему,пходу дешифратора, я инверсный выход счетного триггера, выход первого ди(рференцирушщего fijKJKfi и RS-триггера иодсо1:дипены соответственно к входу третьего дифференцирующего Олокг и вторым входам первого элемента Ш1И и элемента И, причем D-ВХОД счетного триггера и выход формирователя выходного сигнала ciартстоп- ных комбинаций являются соответственно канальн1)1м входом и выходом системы, отличающаяся тем, чт1) с целью повышения скорости передачи

информации, на передающей стороне введены дополнительные преобразователь кода, блок накопителей и шифратор, при этом информационный вход доп(Л1Нительного преобразователя кода подключен к информационному вх(щу первого преобразователя кода, тактовые входы первого преобразователя кода и дополнительного преобразователя кода подключены к соответствующим выходам первого регистра сдвига, выходы дополнительного преобразователя кода подсоединены через дополнитель- ньш блок накопителей к соответствующим входам блока ключей, дополнительные выходы которого подсО .-динены к coijTBeTCTBymmHM дополнят ел )ным входам вторе)го преобразователя кода, выходы которого подсоединены t соот- ветствуюишм входам первого, второго и дополнительного шифраторов, выходы дополнителы с го шифратора полсоеди-- нень; к соо гиетс |-в ..чсщим дополнительным входам второго регистра сдвига, а объединенные тактовые входы блока накопительгй и дополнительного блока накопителей и управляющий вход бло1;а KJJHlчeй подключен соответственно к первому и второму допо- 1нительным выходам первого р гистра сдвига, на приемной стороне введены первый и второй блоки накопителей, при этом соот- 1}етству1ощие выходы преобразователя кода через первый и второй блоки накопителей подсоединены к соответствуюш 1 установочным входам третьего регистра сдвига, тактовый вход которого через второй элемент ИЛИ подключен к третьи выходам первого регистра сдвига, тактовые входы первого и второго блоков . накопителей подключены к второму выходу первого регистра сдвига, а дополнительный выход генератора импульсов подсоединен к тактовому входу счетного триггера.

Фиг./

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи дискретной информации с исправлением ошибок | 1985 |

|

SU1283990A1 |

| Система передачи дискретной информации с решающей обратной связью | 1983 |

|

SU1111258A1 |

| Устройство для кодирования и декодирования дискретной информации | 1983 |

|

SU1159166A1 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Двухкратная стартстопно-синхронная система передачи дискретной информации | 1988 |

|

SU1570018A1 |

| Устройство для приема,кодирования и передачи информации | 1973 |

|

SU596998A1 |

| Многоканальное устройство для сбора и регистрации информации | 1980 |

|

SU945857A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для ввода информации | 1981 |

|

SU997024A1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение скорости передачи информации. Система содержит по передающей стороне г-р импульсов, элемент И, RS-триггер, делитель частоты, два регистра сдвига, два преобразователя кода, блок накопителей, блок ключей, два шифратора и счетный триггер, а на приемной стороне формирователь выходного сигнала старт-стопных комбинаций, генератор импульсов, элемент И, три регистра сдвига, счетный триггер, три дифференцирующих блока, RS-триггер, два элемента ИЛИ, дешифратор и преобразователь кода. Цель достигается введением дополнительно на передающей стороне преобразователя кода, блока накопителей и шифратора, а на приемной стороне двух блоков накопителей. Даны ил.выполнения передающей и приемной сторон системы. 2 ил.

21

4

| Устройство для защиты от ошибок | 1974 |

|

SU517174A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Система передачи дискретной информации с решающей обратной связью | 1983 |

|

SU1111258A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-10-30—Публикация

1987-10-06—Подача