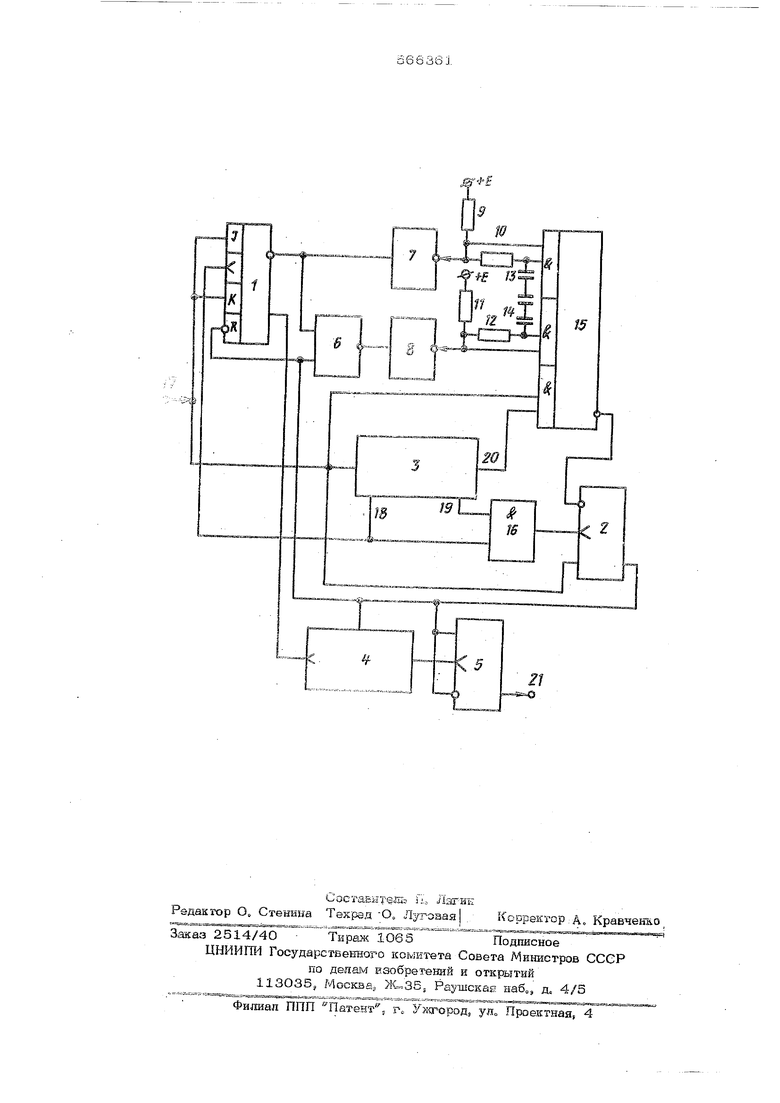

(54) ЛОГИЧЕСКИЙ НАКОПИТЕЛЬ ИМПУЛЬСОВ ческий элемент И, причем вход синхрони-эации входного D К-триггера соединен с п вым выходом элемента задержки, информаод онвые входы которого соединены с шиной запускающих импульсов, информационный вход второго триггера подключен к шине запускаю их импульсов, а его тактируемый вход через дополнительный логический элемент И подключен к первокгу и второму выходу элемента задержки, а вход установки второго триггера соединен с,выходом логического элемента 2И-ЗИЛЙ-НЕ, входы которого подключены соответственно к вхов ду и третьему выходу, элемента задержки, входам инверторов и к емкостным некопяте лям. На чертеже представлена функциональная схЕМа логического накопителя импульсов, Логический накопитель импульсов содержит входной 3 К триггер 1, промежуточный О-Чриггер 2,1 элемент 3 задержки, пересчет ную декаду 4 и выходной D-триггер 5. Инверсный выход триггера 1 соединен с элементом И-НЕ 6 и инвертором 7, второй инвертор 8 соединен с выходом элемента , И-НЕ 6. Выходы инверторов 7 и 8 соеди-. нены с двумя емкостными накопителями, состоящими из резисторов 9-12 и конденса торов 13 и 14, соединенных с элементом 2И-ЗИЛИ-НЕ 15, выход которого соединен с входом установки состояния О промежуточного О-ч-риггера |2. Элемент И 16 соединен с шиной 17 входных сигналов через элемент 3 задержки с отводами 18 и 19. .Шина 17 через выход 20 элемента 3 3aAap жки соединена с элементом 2И-ЗИЛИ-НН 15 Выходной сигнал снимается с выхода триггера 5 по шине 21. В исходном состоянии сигналом с прямого выхода X) -триггера 2 установка в исходное состояние триггеры 1, 5, пересчетная декада 4 и.схема И-НЕ 6 удерживаются в закрытом состоянии, Конденсаторы 13 и 14 разряжены) через резисторы 1О, 12 и выходы инверторов 7 и 8, Перрый импульс последовательности поступает на вход триггера 1, информационный вход триггера 2, входы элемента 3 задержки и элемента 2И-ЗИЛИ-НЕ 15. С от вода 18 элемента 3 задержки снимается сигнал, задержанный на величину i . , равную максимальной длительности импульса помехи в данной аппаратуре, с отвода 19t, равную минимальной длительности -накапливаемого импульса, с выхода 20 д J равную максимальной длительности накапливаемого сигнала. С отвода 18 Элемента задержки сигнал поступает |на ,вход синхронизации триггера 1, однако ввиду того, что промежуточный триггер 2 еще находится в состоянии О, триггер 1 остается в исходном состоянии О за счет наличия сигнала установка в исходно состояние с триггера 2. Если длительность входного импульса меньше минимальной длительности накапливаемых импульсов, триггер 2 остается в исходном состоянии. Если входной импульс имеет длительность, большую времени задержки между отводами 18 и 19, но меньшую, чем задержка между входом и отводом 19, соответствующую минимальной длительности накапливаемых импульсов, то на выходе элемента 16 появляется импульсный сигнал., Однако на информационном входе триггера 2 устанавливается к моменту прихода импульса сигнал О, поэтому триггер 2 остается в состоянии О. Если входной импульс имеет длительность, большуюминимальной длительности накапливаемых импульсов, триггер 2 переключается в состояние 1, сигнал установка в исходное состояние снимается, в результате Чего схема логического накопителя импуль-: сов переключается в рабочее состояние. Открывается элемент И-НЕ 6, на выходе которого устанавливается сигнал О. Инверторы 7 и 8 выбираются с открытым коллекторным выходом для исключения влияния выходного сопротивления на заряд времязадающей емкости. Поэтому выходной транзис- тор инвертора 8 закрывается и начинается заряд конденсатора 14 от источника питания Е через резисторы 11 и 12. Есяи временной интервал между двумд импульсами больше предельно: допустимого, конденсатор 14 заряжается до порога открывания элемента 2И-ЗИЛИ-НЕ 15, сигнал с выхода элемента Г5 переключает триггер 2 в исходное состояние О, в результате чегО;схема возвращается в исходное состояние. Если временной интервал между импульсами меньше предельно допустимого, то с помощью элемента 3 задержки и триггера 1 производится анализ второго импульса Последовательности на условие превышения длительности импульса максимальной длительности помехи. На вход синхронизации триггера 1 поступает задержанный входной импульс с временем задержки 1 . На входы J и К поступает входной импульс без задержки. Поэтому, если длительность входного импульса меньше времени t , на входах и К к моменту прихода импульса синхронизации с отвода 19 элемента 3 задержки устанавливается сигнал О, триггер 1 остается в исходном состоягши. Если входной импульс имеет длительность,большую времени t. , триггер 1 переключается в противоположное состояние, элемент 6 з крывается, на выходе инвертора 8 устанавливается состояние О, в результате чего конденсатор 14 разряжается через резистор 12 и выход инвертора 8. С инверсного выхода триггера 1 сигнал О закрывает инвертор 7, конденсатор 13 заряжается через резисторы 9 и 10. Таким образом, триггер 1 переключается в противоположное состояние только при выполнении условия -длительность входного имп са; -время задержки на отводе 18 элемента 3 задержки. Если длительность входного импульса удовлетворяет условию (где 2 минимальная длительность нак пливаемых импульсов; t -tj- время задержки между отводами 18 и 19 элемента 3 задержки, то триггер 2 переключается в состояние О и возвращает схему в исходное состояние. При превьпиении длительное rti входного импульса максимальной длительности накапливаемых импульсов Ij , равной времени задержки на отводе 20 элемента 3 задержки, открываем ся элемент 2И-ЗИЛИ-НЕ 15 и возвращает триггер 2 в состояние О , в результате чего схема возвращается в исходное состоя ние. Таким образом, схема производит накопление только.импульсов, удовлетворяющих условию t,i,xij, где - максимальная длительность накапливаемых импульсов, По достижении К + I импульсов, следующих с периодом меньше расчетного и удовлетворяющих условию (3), на выходе пересчетной декады 4 появляется сигнал, переключающий триггер 5 в состояние , с прямого выхода которого снимается сигнал в нагрузку,, где К - коэф мциент пересчета декады 4 и триггера 1. По окончании последовательности заряжается один из конденсаторов 13 и 14 до порога открываиия элемента 15, сигналом с выхода которого триггер 2 переключается в состояние О и схема возвра щается в исходное состояние. Выходы пересчетной декады 4 и трнгге ра 1 одновременно могут использоваться как делители частоты следования импульсов (на схеме не показаны). Использование в схеме логического накопителя импульсов дополнительных элементов и ;их взаимосвязи увеличивает помехоустойчивость накопителя импульсов по входу, так как исключается возможность срабатывания накопителя от импульсных сигналов помех, длительность которых меньше длительности накапливаемых импульсов. Это позволяет значительно увеличить надежность работы устройства, особенно в измерительных схемах, где требуется выдать сигнал в нагрузку по определенному импульсу последовательности. Введение контроля длительности импульсов по допусковому принципу расширяет функциональные возможности накопителя, так как по одному каналу связи могут одновременно передаваться несколько послеaoBaTeabHOCTeEjоднако в данном устройстве накапливаются только , удовлетворяющие условию (3), В схемах контроля параметров импульсов уход одного из импульсов за пределы норм регистрируется снятием сигнала на выходе, причем для надежности регистрации отклонения параметров импульсов от нормы выходной I сигнал подается только после К+1 импульсов. Это позволяет регистрировать ошибки в быстродействующих устройствах с помощ1зЮ средств, имеющих более низкое быстродействие. Формула изобретения Логический накопитель импульсов по авт. св. № 514445, о т л и ч а ю щ и й- . с я тем, что, с целью повышения помехоустойчивости , в него введен элемент задержки и дополнительный логический элемент И, причем вход синхронизации входного ЗК риггера соединен с первым выходом элемента задержки, информационные входы которого соедийены с шиной входных сигналов, информа ционный вход промежуточного |0-триггера подключен к шине: входных сигналов, тактируемый вход через дополнительный логический элемент И подключен к первому и второму выходу элемента задержки, а вход установки соединен с выходом логического эле- мента 2И-ЗИЛИ-НЕ, входы которого подключены соответственно к входу и третьему выходу элемента задержки, входам инверторов и к емкостным накопителям.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический накопитель импульсов | 1978 |

|

SU739746A1 |

| Логический накопитель импульсов | 1975 |

|

SU514445A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1117837A1 |

| Одновибратор | 1990 |

|

SU1750027A1 |

| Формирователь импульсов | 1982 |

|

SU1095361A2 |

| Транзисторный инвертор | 1990 |

|

SU1757069A1 |

| Мостовой инвертор | 1988 |

|

SU1529383A1 |

| Формирователь задержки импульсов | 1982 |

|

SU1083354A1 |

| Измеритель характеристик электрического сигнала | 1987 |

|

SU1429053A1 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

Авторы

Даты

1977-07-25—Публикация

1976-02-20—Подача