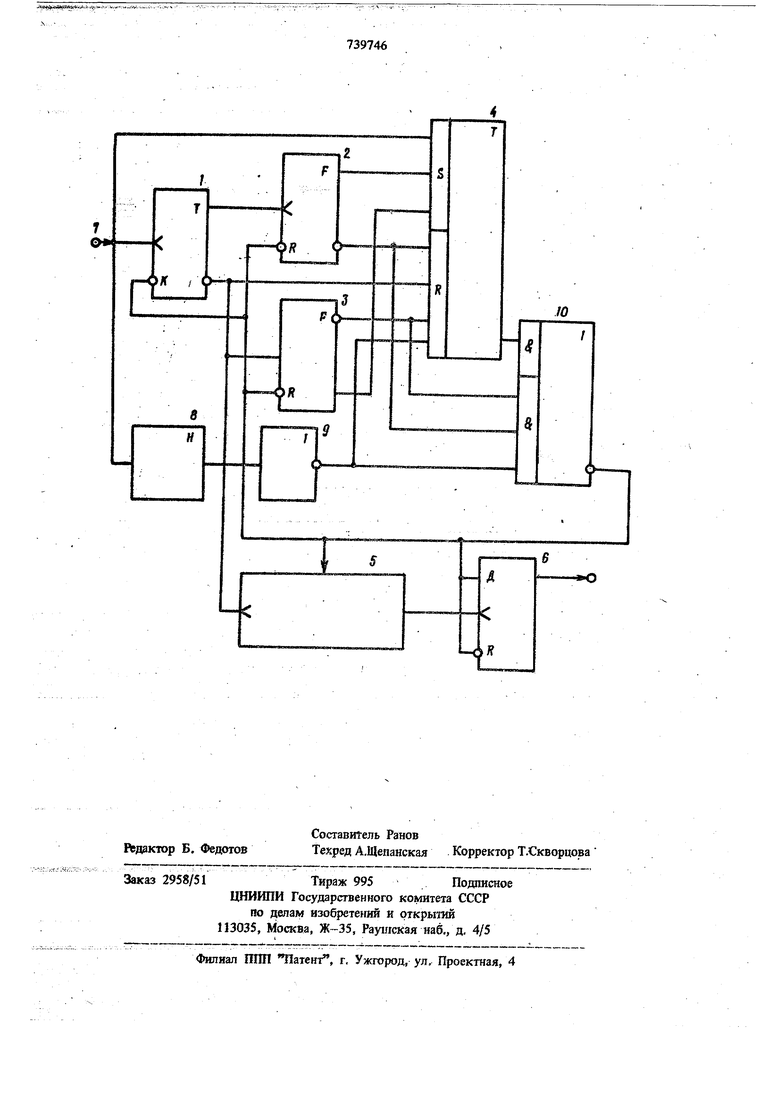

(54) ЛОГИЧЕСКИЙ НАКОПИТЕЛЬ ИМПУЛЬСОВ Предлагаемый логический накопитель импульсоъ относится к импульсной технике, может быть использован в радиоэлектронных устройсгвах вычислительной и измерительной техники, системах автоматического управления и регулирования в качестве простейшего устройства логической обработки последовательности импул сных сигналов. Известно накопительное устройство с контро пем параметров импульсов по методу заряда емкостей дозированным пропорционально длительности импульса током, содержащее триггер, входы которого подключены к накопительным конденсаторам через схемы И-НЕ 1. К недостаткам известного устройства следует отнести -односторонний контроль периода еле- дования накапливаемых импульсов. Известен также логический накопитель импульсов, содержащий входной триггер, входную шину, пересчетную декаду, выходной триггер RS-триггер, управляемый ключ, два элемента НЕ, два элемента И-НЕ и два накопителя на конденсаторах, выходы которых соединены соответственно с первыми входами первого И второго элементов И-НЕ, вторые входы которых соединены со входами соответствующих накопителей на конденсаторах и выходами элементов НЕ, выходы- элементов И-НЕ соединены со входами R В5-триггера, которого соединен со входной шиной и со счетным входом входного триггера, вход установки в 0 которого соединен со входом сброса пересчетной декады, со входами D и установки в О выходного триггера, с прямым выходом RSтриггера и с первым входом управляемого ключа, второй вход которого соединен с ий- версньш выходом входного триггера, со входом первого элемента НЕ, а выход со входом второго элемента НЕ; прямой вход входного триггера соединен со счетным входом пересчет1ЮЙ декады, выход которой соединен со счетным входом выходного триггера 21. ia известном устройстве входной триггер переключает поочередно два накопителя на конденсаторах для контроля временного интервала между двумя соседними импульсами последовательности. ,. ., .37 При превышении интервала времени между i входными импульсами заданной величины срабатывает RS-триггер, который устанавливает элементы устройства в исходное состояние. Когда интервалы времени между вxoд rыми HMnyjibcaMH меньше заданной величины, входныеимпульсы считаются в пересчетпой декаде, переполнение пересчетиой декады индицируется перебросом выходного триггера. Недостатком известного устройства состоит в том, что диапазот частот накапливаемых импулбсов ограничентолько с нижней стороны. Цель Изобретения - получение двустороннего ограничения по частоте следования накапливаемых импульсов.. Поставленная цель достигается тем, что в логический 1акОпитель импульсов, содержащий входную шину, входной триггер, пересчетную декаду, выходной триггер, элемент НЕ и RSтриггер, первый вход S которого соединен со входной шшгой и с тактовым входом входного триггера, вход установки в О которого соединен со входом сброса пересчетной -декады и со входами D и установки в О выходного триггера, тактовый вход которого соедине с выходом пересчетной декады, введены элемен задержки, два формирователя и элемент И-И ЛИ НЕ с двумя структурами И, первь1й вход перво структуры И соединен с прямым выходом RS триггера, второй и третий входы S которого соединены с прямым и. входами первого и второго формирователей, инверсные входы которы соединены с первым и вторым входами R RS триггера и второй структуры И элемента И-ИЛ НЕ, третий вход второй структуры И которого соеди ен с выходом элемента НЕ и с третьим : входом R RS-триггера, четвертый вход R кЪторого соедит1ен с инверсным выходом входног триггера и тактовыми входами второго формирователя и пересчетной депкады, вход сброса которой соединен с выходом элемента И-ИЛИ НЕ и со входами установки в О форйирователей, счетный вход первого формирователя соединен с прямым выходом входного триггера, счетный вход которого соединен через элемент задержки со входом элемента НЕ. На чертеже представлена структура логического накопителя импульсов. , Устройство содержит входной триггер 1, фор .мирователи 2,3, RS-триггер 4, пересчетную дека ду 5, выходной триггер 6, входную шину 7, элемент эадеркжи 8, элемент НЕ 9, элемент И-ИЛИ-НЕ 10. Входная шина 7 соединена с первь1М входом S RS-триггера 4, через элемент задержки 8 - со входом элемента НЕ 9 и 1гепосредствен но - со счетным входом входного триггера 1, вход установки в О которого с)евд тенТ6 входа ми установки в О формиронптелсй 2,3, со входом сброса пересчетной декады 5, со входами D и установки в О П1 1ход11О1О триггера 6 и с вь1ходом элемента И-ИЛИ-НЕ 10, вход первой структуры И которого соединен с прямым выходом RS-триггера 4, второй и третий входы S которого соединены с прямыми выходами формирователей 2,3. Инверсные выходы последних соединены с первым и вторым входами R RS-триггёра 4 и второй структуры И элемента И-ИЛИ-НЕ 10, третий вход второй структуры И которого соединен с выходом элемента НЕ 9 и с третьим входом R RS-триггера 4. Четвертый вход R триггера 4 соединен с инверсным выходом триггера 1, со счетными входами формирователя 3 и пересчетной декады 5, прямой выход триггера 1 соединен со счетным входом формирователя 2, выход пересчетной декадь 5 соединен со счетным входом выходного триггера 6. Устройство работает следующим образом. В исходном состоянии на входной шине 7потенциал О, на выходе элемента НЕ 9 и инверсньхх выходах формирователей 2 и 3-уровень 1, поэтому потенциал О с выхода элемента 10 удерживает в исходном нулевом состоянии входной триггер 1, формирователи 2 и 3, пересчетную декаду 5 и выходной триггер 6. Входной импульс, пройдя элемент задержки & и элемент НЕ 9, закрывает элемент И-ИЛИНЕ 10, на выходе которого устанавливается потенциал 1, в результате чего снимается сигнал установки всего устройства в исходное состояние. Элемент задержки 8 необходим для включения устройства в работу после прихода первого импульса последовательности. По заднему фронту входного импульса триггер I переключается в состояние 1, положительным перепадом с триггера 1 запускается формирователь 2, и на время формирования импульса формирователя потенциалом О с инверсного входа формирователя 2 закрывается элемент И-ИЛИ-НЕ 10, в результате чего на время формирования импульса потенциал установка устройства в исходное состояние с выхода элемента 10 отсутствует. Если второй импульс последовательности приходит во время формирования импульса формирователя 2, происходит переключение входного триггера 1 в состоя1гие О, запускается формирователь 3, а сигналом с инверсного выхода формирователя 3 элемент И -И.Г1И НЕ 10 снова удерживается в закрытом состоянии. В результате этого при условии, что период следования импульсов не 6ojFee длительности импульсов формирователей 2 и 3, на выхсчдс элемента И-ИЛИ-НЕ 10 постоянно сохриияося .потенциал 1. Происходит контроль nepH(vi;i йчедовамия импульсов iro максимуму. По нак лению заданного числа импульсов включается пересчетная декада 5, положительным перепадом напряжения с ее выхода запускается выходпой триггер 6, который выдает в нагрузку сигнал. Если период следова 1йя Импульсов такой, ,к моменту прихода третьего импульса формирователь 2 euie формирует импульс, то на трех S входах RS-триггера Ч устанавливается состояние 1, и по совпадению этих трех потенциалов RS-триггер 4 переключается в состояние , элемент И-И ЛИ-НЕ 10 открывается, на его выходе устанавливается потенциал О, и происходит сброс формиров телей 2 и 3, триггеров 1 и 6 и пересчетной декады 5. Произошел контроль импульсов по минимуму периода их следования. Таким, образом, в накопителе накапливаются только импульсы, период следования которых удовле творяет условию: Т t накапливаемых - период следования импульсов; t - длительность импульса формирователе Переключение триггера 4 в состояние 1 происходит по переднему фронту входного импульса, а по заднему его фронту с выхода элемента задержки 8 и элемента НЕ 9 триггер 4 по совпадению потенциала 1 на четырех R входах переключается в состояние О Устройство оказывается в исходном состоянии При дальнейшем поступлении импульсов накопитель функционирует аналогично. Таким образом, в предлагаемом логическом накопителе импульсов диапазон накапливаемы импульсов ограничен по максимуму и минимуму, что позволяе использовать накопитель д1Я. более широких цемсн, когда требуется накопление импульсов тол.ько определенного диапазона периода следования, например, в мно гократных устройствах связи. Формула .изобретения Логический накопитель импульсов, содержащий входную шину входной триггер, пересчетную декаду, выходной триггер, элемент НЕ и RSтриггер, первый вход S которого соединен со входной шиной и тактовым входом входного триггера, вход установки в О которого соединен со входом сброса пересчетной декады и со входами D и установки в О выходною триггера, тактовый вход которого соединен С выходом пересчетной декады, отличающийся тем, что, с целью двухстороннего ограничения по частоте следования накапливаемых импульсов, в него введены элемент задержки, два формирователя и элемент И-ИЛИ- НЕ с двумя структурами И, первый вход первой структуры И соединен с прямым выходом RS-триггера, второй и третий входы S которого соединены с прямыми выходами первого и второго формирователей, инверсные выходы которых соединены с первым и вторым входами R RS-триггера ивторой структуры И элемента И-ИЛИ-НЕ, третий вход второй структуры И которого соединен с выходом элемента НЕ и с третьим входом R RS-триггера, четвертый вход R которого соединен с инверсным выходом входного триггера и тактовыми входами второго формирователя и пересчетной декады, вход сброса которой соединен с выходом элемента И-ИЛИ-НЕ и со входами установки . . в О формирователей, счетный вход первого формирователя соединен с первым выходом входного триггера, счетный вход коротого соединен через элемент задержки со входом элемента НЕ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 429539, кл. Н 03 К 25/02, 1975.2.Авторс:кое свидетельство СССР N 514445, кл. Н 03 К 25/04, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический накопитель импульсов | 1976 |

|

SU566361A2 |

| Логический накопитель импульсов | 1975 |

|

SU514445A1 |

| Многофункциональное счетное устройство | 1985 |

|

SU1298911A2 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU843245A1 |

| Многофункциональное счетное устройство | 1979 |

|

SU819969A2 |

| Формирователь временной задержки для управления прерывателем | 1990 |

|

SU1780162A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

Авторы

Даты

1980-06-05—Публикация

1978-01-20—Подача