j Изобретение относится к электроизмерительной и импульсной технике и может быть использовано для измерения времени нарастания, установления и выброса ненормированных переходных процессов.

Цель изобретения - расширение функциональных возможностей за счет нормировки электрических сигналов и определения времени нарастания и выброса и повышение точности измерения времени установления путем устранения несинхронности запуска с началом участка нарастания переходной характеристики.

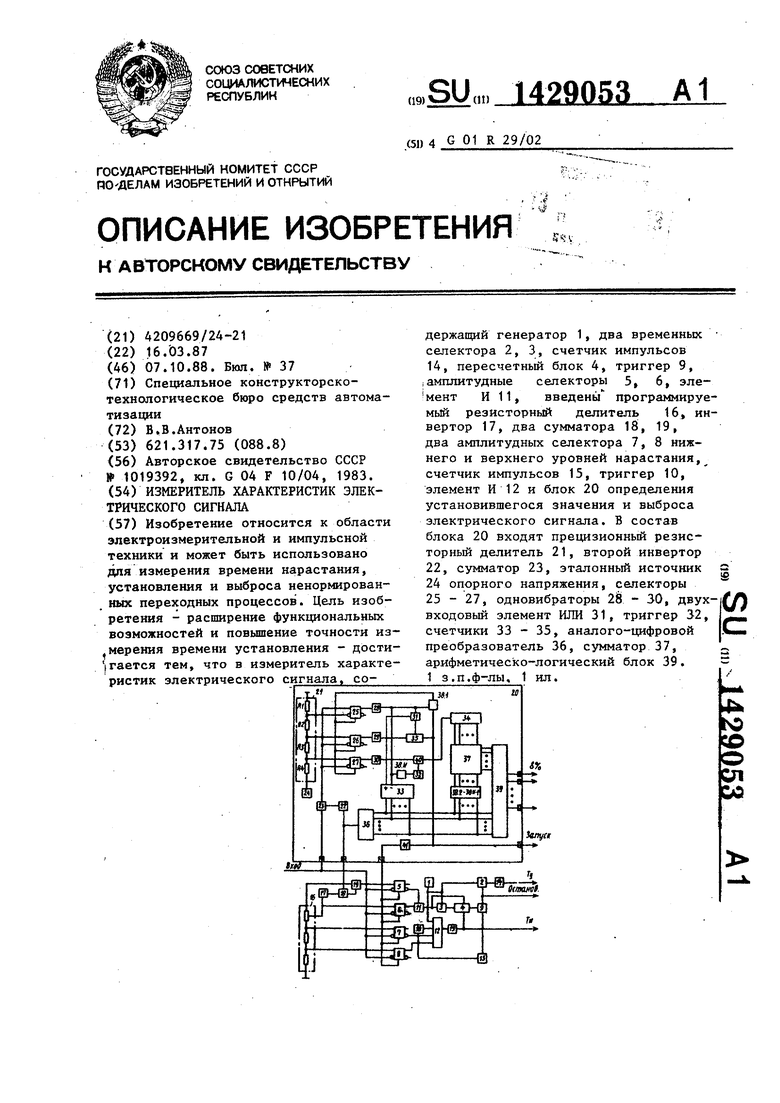

На чертеже представлена функциональная схема измерителя.

Измеритель характеристик электрического сигнала содержит генератор 1, временные селекторы 2 и 3, пересчетный блок 4, амплитудные селекторы 5 и 6 верхнего и нижнего уровней установления, амплитудные селекторы 7 и 8 верхнего и нижнего уровней нараста- ния, первый и второй триггеры 9 и 10, первый двухвходовый элемент И 11, второй четырехвходовый элемент И 12, первый одновибратор 13, первый и второй счетчики 14 и 15 импульсов, программируемый резисторный делитель 16, аналоговый инвертор 17, аналоговые ;сумматоры 18 и 19, блок 20 определе- i ния установившегося значения и выбро- Iса электрического сигнала. : В состав блока 20 определения I установившегося значения и выброса ;входят прецизионный резисторный делитель 21,.второй инвертор 22 и сумматор 23, эталонный источник 24 опорного напряжения, селекторы нижнего приближения 25, поиска установившегося уровня 26, верхнего приближения 27 второй, третий и четвертый одно- вибраторы 28 - 30, двухвходовый элемент ИЛИ 31, триггер 32, реверсивный счетчик 33 установившегося значения, счетчик 34 выброса, двухразрядньА счетчик 35 установления, цифроанало- говый преобразователь 36, логические сумматор 37 и инверторы 38.1 - 38.N, арифметическо-логический блок 39, элементы 2И 40 и задержки 41.

Пересчётный блок 4 включает в себя инвертор,, счетчик останова.

логический компаратор, элемент 2И

НЕ. Программируемый резисторный делия-ель 16 состоит из резисторного делителя и программируемого коммутатора.

Одновибратор 29 составлен из отдельных моновибраторов и элемента ИЛИ.

Выход квантующего генератора 1 соединен с первыми входами временных селекторов 2 и 3 и второго элемента И 12. Второй вход временного селектора 2 соединен с выходом первого триггера 9, а выход - со счетным входом первого счетчика 14 импульсов; Второй вход временного селектора 3 совместно с вторым входом пересчетного блока 4 соединен с выходом первого элемента И 11, а выход - с первым входом блока 4. Второй вход второго элемента И 12 соединен с инверсным выходом амплитудного селектора 7 верхнего уровня нарастания через второй триггер 10, а третий вход элемента И 12 соединен непосредственно с инверсным выходом селектора 7 и через одновибратор 13 - с S - входом первого триггера 9.-Четвертый вход элемента И 12 соединен с прямым выходом селектора 8 нижнего уровня нарастания, а выход этого элемента - со счетным входом второго счетчика

15импульсов, выходом подключенного к третьему Входу пересчетного блока 4, связанного выходом с R-входом триггера 9. Первый элемент И 11 входами соединен с инверслым выходом селектора 5 и прямым выходом селектора 6 соответственно верхнего и нижнего уровней установления. Сигнальный вход блока 20 определения установившегося значения и выброса электрического сигнала соединен с инверсными входами селекторов 5-8, его выход блокировки - с их входами установки триггера памяти, а выход установле- входом программируемого резисторного делителя 16 и с первыми входами аналоговых сумматоров 18 и 19. Первый выход делителя 16 соединен через аналоговые инвертор 17 и сумматоры 18 и 19 С прямым входом селектора 5 верхнего уровня установления,

а непосредственно - с прямым входом селектора 6 нижнего уровня установления. Второй и третий выходы делителя

16соединены с прямыми входами селекторов верхнего уровня 7 и нижнего уровня 8 нарастания соответственно.

Измеритель характеристик электри-. ческого сигнала работает .следующим образом.

Перед поиском установившегося значения электрического сигнала и

началом измерений триггеры 9, 10 и 32 и счетчики 14, 15 и 33 - 35 устанавливают в исходное состояние импульсом общего сброса, а триггеры 9 и 10 и счетчики 14 в пересчетном блоке 4 устанавливают в исходное состояние импульсом системного сброса перед проведением каждого второго и последуюир1Х измерений времени нарастания и установления при интерполяции зоны установления (цепи общего и системного сброса не показаны) . При этом на выходе триггера 9

с выхода эталонного источника 24 опорного напряжения.

При увеличении или уменьшении входного электрического сигнала в пределах триады уровней AU;,K/6, &U,,n/2, ли,ц5/6 с вьгход-ов делителя 21 начинается сравнение в селекторах 25 - 27, одновибраторы 28 и 30 апус- каются положительными перепадами с прямых выходов селекторов 25 и 27. Положительный перепад на прямом выходе селектора 27 появляется при пересечении входным сигналом снизу

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель временных характеристик электрического сигнала | 1985 |

|

SU1291897A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| СЧЕТЧИК-ИДЕНТИФИКАТОР КРИТИЧЕСКИХ ВЫБРОСОВ ИЛИ ПРОВАЛОВ НАПРЯЖЕНИЯ И СУММАРНОГО ВРЕМЕНИ ОТКАЗОВ ЭЛЕКТРООБОРУДОВАНИЯ | 2001 |

|

RU2193275C1 |

| ЦИФРОВОЙ СЧЕТЧИК КРИТИЧЕСКИХ ВЫБРОСОВ И ПРОВАЛОВ НАПРЯЖЕНИЯ И СУММАРНОГО ВРЕМЕНИ ОТКАЗОВ ЭЛЕКТРООБОРУДОВАНИЯ | 2001 |

|

RU2191426C1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Устройство для измерения средней частоты серии импульсов | 1990 |

|

SU1737356A1 |

| Устройство для управления тиристорным регулируемым автономным инвертором с широтно-импульсной модуляцией | 1976 |

|

SU692062A1 |

| Устройство для регулирования температуры | 1986 |

|

SU1403025A1 |

Изобретение относится к области электроизмерительной и импульсной техники и может быть использовано для измерения времени нарастания, установления и выброса ненормированных переходных процессов. Цель изобретения - расширение функциональных возможностей и повышение точности измерения времени установления - дости Гается тем, что в измеритель характеристик злектрического сигнала, содержапщй генератор 1, два временных селектора 2, 3, счетчик импульсов 14, пересчетный блок 4, триггер 9, iамплитудные селекторы 5, 6, эле- мент И 11, введены программируемый резисторный делитель 16, инвертор 17, два сумматора 18, 19, два амплитудных селектора 7, 8 нижнего и верхнего уровней нарастания, счетчик импульсов 15, триггер 10, злемент И 12 и блок 20 определения установившегося значения и выброса злектрического сигнала. В состав блока 20 входят прецизионный резисторный делитель 21, второй инвертор 22, сумматор 23, зталонный источник 24опорного напряжения, селекторы 25- 27, одновибраторы 213 - 30, двух входовый злемент ИЛИ 31, триггер 32, счетчики 33 - 35, аналого-цифровой преобразователь 36, сумматор 37, арифметическо-логический блок 39. 1 з.п.ф-лы. 1 ил. (Л т

устанавливается низкий (запрещающий), 5 вверх уровня и U„,„ 5/6 с третьего

20

30

а на выходах триггеров 10 и 32 - высокий (разрешающий) уровни напряжения. На выходах счетчиков 14, 15 и 33 - 35 устанавливается нулевой код. Низким уровнем с выхода элемента И 11, проинвертированным блоком 4 в высокий уровень, счетчик в пересчет- ном блоке 4 сбрасывается в исходное состояние и на его выходах устанавливается нулевой код. Внешним управляю- 25 щим устройством устанавливается код управления делителя 16, равный половине зоны установления.

В исходном состоянии на входы триггера памяти селекторов 5-8 поступает низкий ( переводящий триггер памяти из режима повторения текущего состояния компараторов в режим памяти предшествующего их состояния) уровень напряжения с выхода блокировки блока 20 и выхода второго разряда его счетчика 35, а на входы триггера памяти селекторов 25 - 27 блока 20 - высокий (переводящий триггер памяти из режима памяти предшествующего состояния компараторов в режим повторения текущего их состояния) уровень с выхода инвертора 38.1.

Селекторы 5-8, 25-27 являются селекторами с встроенным триггером памяти и парафазным выходом (типа КР 597СА2 Ветрунге).

Резисторный делитель 21 блока 20 определения установившегося значения и выброса имеет следующее соотношевыхода делителя 21 (монотонное уве чение сигнала), а положительный перепад на прямом выходе компарато при пересечении входным сигналом сверху вниз уровня &U,/6 с перво выхода делителя 21 (монотонное уме шение сигнала).

При начале поступления исследуе мого электрического сигнала по шин Вход измерителя на сИгнальны вх блока 20 аналоговый сумматор 23 фо мирует разностный сигнал

Ik

ли - UBX-ZUU

мии ,

где и

8Х

мин

35

- входное напряжение элект ческого сигнала; , - i-e (наименьшее) приращ ние выходного напряжени дифроанадогового преобр зователя (в исходном состоянии на входе прео разователя 36 нулевой к а на его выходе-нулевой уровень напряжения); количество задействованных разрядов цифроаналогово го преобразователя 36. Поскольку в исходном состоянии н выходе преобразователя 36 присутств 45 е нулевой уровень напряжения, то н выходе аналогового инвертора 22-так же нулевой уровень.

Когда разностный сигнал с выхода

40

К ние величин резисторов: R1:R2:R3:R4 50 аналогового сумматора 23 достигает

уровня 5/6, положительным перепадом селектора 27 верхнего при лижения запускается одновибратор 30 вырабатьшающий управляющий импульс 55 положительной полярности, который поступает на вход суммирования реве сивного счетчика 33 и вызывает увел чение его кода на единицу и выходно го уровня преобразователя 36 на

1/6:1/3:1/3:1/6.

Соотношение резисторов образует циклическую т)иаду повторяющихся ком- параторных уровней, равноотстоящих один от другого на треть наименьшего приращения уровня напряжения с выхода цифроаналогового преобразователя 36 Аид,„ц, равного по величине уровню

выхода делителя 21 (монотонное увеличение сигнала), а положительный перепад на прямом выходе компаратора - при пересечении входным сигналом сверху вниз уровня &U,/6 с первого выхода делителя 21 (монотонное уменьшение сигнала).

При начале поступления исследуемого электрического сигнала по шине Вход измерителя на сИгнальны вход блока 20 аналоговый сумматор 23 формирует разностный сигнал

Ik

0

ли - UBX-ZUU

мии ,

где и

8Х

мин

5

- входное напряжение электрического сигнала; , - i-e (наименьшее) приращение выходного напряжения дифроанадогового преобразователя (в исходном состоянии на входе преобразователя 36 нулевой код, а на его выходе-нулевой уровень напряжения); количество задействованных разрядов цифроаналогово- го преобразователя 36. Поскольку в исходном состоянии на выходе преобразователя 36 присутству- 5 е нулевой уровень напряжения, то на выходе аналогового инвертора 22-так- же нулевой уровень.

Когда разностный сигнал с выхода

0

К 50 аналогового сумматора 23 достигает

уровня 5/6, положительным перепадом селектора 27 верхнего приближения запускается одновибратор 30, вырабатьшающий управляющий импульс 55 положительной полярности, который поступает на вход суммирования реверсивного счетчика 33 и вызывает увеличение его кода на единицу и выходно го уровня преобразователя 36 на

.1429053

Выходной уровень преобразователя 36 инвертируется в аналоговом инверторе 22 и формируется в аналого |вом сумматоре 23 в разностный сигнал

I Ли Ug, -

;/

уменьшающий входной электрический сигнал на д U,,ц . После каждого уве- пичения выходного кода счетчика 33 иа единицу младшего разряда выходной уровень напряжения цифроаналого- вого преобразователя 36 увеличивается на величину М1„„ц . Процесс верхнего приближения продолжается до тех пор, пока не. прекратится дальнейшее приращение исследуемого сигнала. Эти же импульсы управления проходят через открытый элемент 2И 40 (на втором входе этого элемента присут- стВует высокий уровень с выхода триггера 32) на Ёход счетчика 34 импульсов , который подсчитывает импульсы управления максимума верхнего приближения . Г После достижения максимума верхне |го приближения входной сигнал начинает уменьшаться, и при пересечении уровня , с первого выхода делителя 21 появляется положительный . перепад на выходе селектора 25 нижнего приближения, запускающий одно- вибратор .28, который вырабатывает первый импульс управления положительной полярности. Этот импульс управления поступает на вход вычитания реверсивного счетчика 33 и вызывает первое уменьшение его выходного |кода на единицу, а проинвертирован

ный импульс отрицательной полярности инвертором 38 опрокидывает триггер 32 в противоположное исходное состоя кие. На выходе триггера 32 появляется низкий (запрещающий) уровень напряжения , закрывающий элемент 2И 40

Одновибратор 29 вырабатывает инвариантные импульсы управления относительно пересечений входным сигналом снизу и сверху (при увеличени и уменьшения сигнала разности Д U) среднего уровня Д. с второго выхода делителя 21. Положительному перепаду с прямого выхода компарато ра 26 соответствует импульс положительной полярности одновибратора 29 а отрицательному его перепаду - импульс положительной полярности одно вибратора 29. При однократном пере40 сечении снизу уровня ди

ЛАИИ

/2 одновибратором 29 вырабатывается импуль а при пересечении этого уровня свер ху вырабатывается импульс одновибра тором 29. Одиночный импульс, проход

и тем самым препятствующий дальнейше-45 через элемент ИЛИ одновибратора 29,

подсчитывается счетчиком 35, на выходе которого появляется код 01. Когда не завершены процессы верхнег или нижнего приближений, то после каждого импульса одновибратора 29 вырабатывается управляющий импульс одновибратора 28 или 30 соответстве но, проходя затем через элемент ИЛИ 31 на вход установки счетчика 3 и устанавливая его вновь в исходное состояние. По завершении поиска установившегося значения вторым импульсом одновибратора 29 на выходе счетчика устанавливается код 10.

сигнала ,В

му прохождению импульсов одновибратора 30 на вход счетчика 34, подсчитывающего абсолютную величину максимума входного

JMC.KC мин; где - количество задействованных

р-азрядов счетчика 34 выброса Первое уменьшение выходного кода реверсивного счетчика 33 на единицу младшего разряда приведет к уменьшению выходного уровня напряжения преобразователя 36 на uUMiAM

6

u,

Ь 1

После каждого уменьшения выходного хода счетчика 33 на единицу уровень выхода преобразователя 36 послдовательно уменьшается процесс нижнего приближения продолжается до прекращения дальнейшего снижения иследуемого сигнала.

Процессы последовательной смены нижнего и верхнего приближений продолжаются до тех пор, пока входной сигнал не прекратит пересечений уровней лил,у,„ /6,йид,„ 5/6. Попадание входного сигнала в зону завершения поиска установившегося значения согласно выражению

Лимин/6 йи

5/6

завершается определением его установившегося значения, которое осуществляется следуюпщм образом. В исходном состоянии на выходах двухразрядного счетчика 35 установления - нулевой код 00.

Одновибратор 29 вырабатывает инвариантные импульсы управления относительно пересечений входным сигналом снизу и сверху (при увеличении и уменьшения сигнала разности Д U) среднего уровня Д. с второго выхода делителя 21. Положительному перепаду с прямого выхода компаратора 26 соответствует импульс положительной полярности одновибратора 29, а отрицательному его перепаду - импульс положительной полярности одно- вибратора 29. При однократном пересечении снизу уровня ди

ЛАИИ

/2 одновибратором 29 вырабатывается импульс, а при пересечении этого уровня сверху вырабатывается импульс одновибра- тором 29. Одиночный импульс, проходя

через элемент ИЛИ одновибратора 29,

подсчитывается счетчиком 35, на выходе которого появляется код 01. Когда не завершены процессы верхнего или нижнего приближений, то после каждого импульса одновибратора 29 вырабатывается управляющий импульс одновибратора 28 или 30 соответственно, проходя затем через элемент ИЛИ 31 на вход установки счетчика 35 и устанавливая его вновь в исходное состояние. По завершении поиска установившегося значения вторым импульсом одновибратора 29 на выходе счетчика устанавливается код 10.

Высоким уровнем с выхода второго разряда счетчика 35, проинвертирован- ным в низкий уровень инвертором 38.1 селекторы 25 - 27 по входу триггера памяти переводятся из режима повторения текущего состояния компараторов в режим памяти их предшествующего состония , предотвращая тем самым последующие ложные срабатывания селекторов 25 - 27 и сбои удержания установившегося уровня напряжения с выхода преобразователя 36 в случае случай- ньк выходов входного сигнала за пределы зоны завершения поиска уста- : новившегося значения. На выходе счетчика 33 устанавливается код установившегося значения, а на выходе преобразователя 36 - напряжение, уровень которого соответствует коду устано- вившегося значения исг I В логич еском сумматоре 37 проис- .ходит логическое сложение максимума исследуемого сигнала в прямом коде- с выходов счетчика 34 и его установив- шегося уровня в инверсном коде после инвертирования прямого кода с. выходов счетчика 33 в инверторах 38. 38.N-1. На выходе сумматора 37 устанавливается код, соответствующий абсолютному значению выброса исследуемого сигнала

Uj BKMotKc V

В арифметическо-логическом блок.е 39 осуществляются последовательно one рации: сдвига влево кода абсолютного значения выброса с выхода -сумматора 23 на один разряд; сравнения сдвинутого влево кода абсолютного значения выброса с кодом установив- шегося уровня напряжения(при результате меньше осуществляется возврат в первую операцию; при результате больше или равно - вычитание кода установившегося уровня из сдвинуто- го влево кода абсолютного значения выброса); возврата в первую операцию (при двухкратном сдвиге влево прекращается сдвиг запятой, означая отсчет результата в процентах); повторения операции сравнения до сигнала переполнения (ограничения сдвига) . .

В результате на .выходе арифметического-логического блока 39 устанав- ливается код, соответствующий относительному значению выброса исследуемого сигнала в процентах.

На этом завершается определение установившегося уровня и выброса и начинается определение времени нарастания и установления электрического сигнала.

Резисторный делитель, входящий в состав резисторного делителя 16, имеет следующее соотношение величин резисторов: R1:..,:R10:R11:R12 1/100:.,.:1/100:4/5:1/10,

Подключением выводов резисторов управляет пpoгpaм шpyeмый кo fl yтaтop. Подключение выхода делителя 16 осуществляется к селектору 6 нижнего уровня установления. Выход делителя 16 предназначен для формирования нижнего уровня установления. Формирование верхнего уровня установления осуществляется в двух аналоговых сумматорах 18 и 19. В сумматоре 18 вьщеляет- ся разностное значение половины зоны установления по выражению

yii -и и

2 У

где bUq - значение зоны установления;

ucr установивщееся значение электрического сигнала; UuH проинвертированное значение нижнего уровня установления в аналоговом инверторе 17. 1

В сумматоре 18 вьщеляется верхний уровень установления в соответствии с выражением

+ йЦй

который затем поступает на селектор 5 верхнего уровня установления.

Одновременно с завершением определения установившегося уровня положительным перепадом с выхода второго разряда счетчика 35 в исследуемой системе по шине Запуск вновь запускается переходный процесс. Положительной перепад, задержанный в элементе 41 на время запуска нового переходного процесса и подачя испытательного сигнала на исследуемую систему, по входу триггера памяти переводит селекторы 5 - 8 из режима памяти предшествующего их состояния в режим повторения текущего состояния, тем самым подготавливая измеритель к измерению временных-характеристик.

На вход программируемого резистор- Н0ГО делителя 16 поступает установившийся уровень напряжения Uцсг с выхо- д цифроаналогового преобразователя 3i. Кодом управления от внешнего уст- р эйства предварительно подключается из резисторов к выходу, устанав- Л1вая требуемую величину половины зоны установления.

За время задержки в элементе 41 производится запуск нового переходного процесса в исследуемой системе и подготавливаются селекторы 5 - 8 к процессу измерения времени нараста- ния и установления. На инверсных вы- ходох селекторов 5 и 7 установлен высокий уровень напряжения, а на прямых выходах селекторов 6 и 8 - иизкий уровень до поступления иссле- руемого сигнала на инверсиые входы селекторов 5-8. При этом на выходах элементов 11 и 12 присутствует низ-- ЛИЙ уровень напряжения, временной селектор 3 закрыт. Временной селек- тор 2 также закрыт низким уровнем Напряжения с выхода триггера 9. На йыходе пересчетного блока 4 присутст- высокий уровень. Поэтому счетчики 14 и 15 остаются в исходном со- Йтоянии.

При поступлении исследуемого сигнала на инверсные входы селекторов- 5 - 8 начинается процесс измерения време- itii нарастания. При пересечении иссле.дуемым сигналом уровня 0,1 третьего выхода программируемого делителя 16 на прямом выходе компаратора 8 нижнего уровня нарастания по- 5|вляется высокий уровень напряжения, на выход элемента И 12 проходят импульсы квантующего генератора 1, которые подсчитываются счетчиком 15. 11ри..пересечении исследуемым сигналом уровня 0,9 иис с второго выхода делителя 16 на инверсном выходе селектора 7 верхнего уровня нарастания появляется низкий уровень напряжения, который, опрокидьшая триггер 10, устанавливает на выходе элемента И 12 низкий уровень, тем самым прекращая подсчет импульсов счетчиком 15. На выходе счетчика 15 фиксируется код, соответствующий времени нарартания электрического сигнала Т,, Размах колебательного уменьшения (вслед за выбросом) электрического сигнала может пересечь сверху вниз уровень 0,9 и ист . На инверсном выходе селек

о 5

0

, О

0

тора 7 в этом случае появляется высокий уровень. Триггер 10 предотвращает появление ложных импульсов на выходе элемента И 12 и искажения результата измерения Т счетчиком 15.

Тем же низким уровнем напряжения с инверсного выхода селектора 7 запускается одновибратор 13, вырабатывающий импульс отрицательной полярности, опрокидывающий триггер 10 в противоположное исходному состояние. На выходе триггера 10 появляется высокий уровень напряжения, который открывает временной селектор 2, и счетчик 14 начинает подсчитывать импульсы квантующего генератора 1.

До пересечения исследуемым сигналом нижнего уровня установления UM с первого выхода программируемого делителя 16 на выходе счетчика 15 находится код, соответствующий времени нарастания Т,. При неравенстве кодов блока 4 и счетчика 15 на выходе пересчетного блока 4 устанавливается низкий уровень напряжения. На втором входе пересчетного блока 4 как и на первом присутствуют низкие уровни, а на выходе пересчетного блока 4 - высокий уровень. Поэтому триггер 10 не опрокидьшается в исходное состояние.

При пересечении исследуемым сигна- лом нижнего уровня установления UUH с первого выхода делителя 16 на- прямом выходе селектор. 6 нижнего уровня установления появляется высокий уровень напряжения, поступающий на второй вход элемента И 11, на первом входе которого присутствует высокий уровень с инверсного выхода селектора 5 верхнего уровня установления. Временной селектор 3 открывается высоким уровнем с выхода элемента И 11 и через него начинают проходить им-, пульсы квантующего генератора 1 на счетный вход счетчика останова пересчетного блока 4. Тем же высоким уровнем с выхода элемента И 11, про- инвертированным в инверторе блока 4, счетчик по входу установки открывается и начинает подсчитывать импульсы с выхода временного селектора 3.

При пересечении исследуемым сигналом верхнего уровня установления с выхода аналогового сумматора 19 на инверсном выходе компаратора 5 верхнего уровня установления.появляется низкий уровень напряжения. На выходе элемента И 11 устанавливается низкий

уровень, закрывающий временной селектор 3. Счетчик останова блока 4 прекращает подсчитывать импульсы квантующего генератора 1. Этим же низким уровнем с выхода элемента И 11, про- инвертированным инвертором блока 4 в высокий, счетчик блока 4 устанавливается в исходное состояние.

По завершении процесса нарастания исследуемого сигнала (прохождение первого экстремума - выброса) начинается процесс уменьшения сигнала, вновь открывается временной селектор

3и счетчик блока 4 подсчитывает импульсы генератора 1, а после пересечения уровня вновь счетчик блока 4

.устанавливается в исходное состояние В момент установления элемент И 11 удерживает временной селектор 3 в открытом состоянии,, а счетчик блока

4- в состоянии непрерывного набора выходного кода. В момент совпадения выходного кода счетчика блока 4 с кодом Т счетчика 15 схема сравнения кодов блока 4 вырабатывает высокий уровень напряжения, совпадающий с высоким уровнем с выхода элемента

И 11 и инвертирующийся в низкий уровень элементом 2И-НЕ блока 4. Огрица- перепадом с выхода пересчетного блока 4 триггер 9 опрокидывается в исходное состояние. Отрицательный перепад с выхода триггера 9 подается на шину Останов для считывания результатов измерений и закрывает временной селектор 2, останавливая счетчик 14, на выходе которого фиксируется код, соответствующий времени установления электрического сигнала Тц .

Для целей интерподяции измерений Tf, и TU относительно вариаций величины зоны установления используется системный сброс, устанавливающий триггеры 9 и 10 и счетчики 14 блока- 4 в исходное состояние. Снимается испытательньш перепад с исследуемой системы и подается импульс по цепи системного сброса. Затем подается новый код управления с внешнего устройства на программируемый коммутатор, запускается испытательный перепад на исследуемую систему и процессы измерения I и Т,, повторяются вновь.

Измеритель характеристик электрического сигнала в двух запусках переходного процесса в исследуемых системах осуществляет нормировку

0

этого сигнала, определение относительной величины выброса в процентах и измерение времени нарастания и установления. Измеритель обеспечивает интерполяцию измерений времени установления, что расщиряет возмЬж- ности применения измерителя в автома-- тизированных комплексах контроля g характеристик импульсных электричес ких сигналов.

Формула изобретения

«

5 1. Измеритель характеристик электрического сигнала, содержащий генератор , выход которого подключен к первым входам первого и второго вре- . менных селекторов, выход первого из которых соединен со счетным вхо дом первого счетчика импульсов, а выход второго временного селектора подключен к первому входу пересчетного блока, выходом соединенного через

5 R-вход первого триггера к второму входу первого временного селектора, амплитудные селекторы нижнего и верхнего уровней установления и первый элемент И, входами соединенный с пря-

0 мым выходом амплитудного селектора нижнего и с инверсным выходом амплитудного селектора верхнего уровней установления, объединенных инверсными входами с входом измерителя, а выхо дом подключенный к второму входу второго временного селектора, отличающийся тем, что, с целью расширения функциональных возможностей и повьшения точности измерений,

0 в него введены программируемый резис- торный делитель, инвертор, два сумматора, два амплитудных селектора нижнего и верхнего уровней нарастания, формирователь импульсов, вторые

5 счетчик импульсов, триггер и элемент И, а также блок определения установившегося значения и выброса электрического сигнала, выход установления которого подключен к входу программируемого резисто рного делителя ,и к первым входам сумматоров, выход блокировки соединен с входами установки амплитудных селекторов уровней установления и нарастания, а сигнальный вход соединен с инверсными входами первого и второго амплитудных селекторов уровней нарастания и с входом измерителя, первый выход . программируемого резисторного делите0

5

jnfl соединен непосредственно с прякым ходом амплитудного селектора нижне- о уровня установления, а через ин- JBeprop и два последовательно соединеных сумматора - с прямым входом ам- Ьлитудного селектора верхнего уровня Кгстановления, второй и третий выходы программируемого реэисторного делите пя подключены к прямым входам ампли- тудных селекторов соответственно верхнего и нижнего уровней нарастания, инверсный выход амплитудного селектора верхнего уровня нарастания соединен с третьим входом второго элемента И непосредственно а с вторым его вх Одом - через второй триг- |гер и подключен к S-входу первого |триггера через первый одновибратор, к первому входу второго элемента И |подключен выход квантующего генерато |ра, а к его четвертому входу - прямой выход амплитудного селектора нижнего уровня нарастания, выход допол- |нительного элемента И соединен через I второй счетчик импульсов с третьим jвходом пересчетного блока, к второму I входу которого подключен выход перво |го элемента И.

; 2. Измеритель по п. 1, о т л и - :чающийся тем, что блок опре- iделения установившегося значения и

:выброса электрического сигнала содержит резисторный делитель, инвертор, сумматор,, источник опорного напряжения, селекторы верхнего и нижне- го приближения и поиска установившегося уровня, три одновибратора, элемент ИЛИ, триггер, счетчик установившегося значения, счетчик выброса, счетчик установления, цифроаналого- вый преобразователь, логический сумматор, N логических инверторов, ариф- метическо-логический блок, элементы 2И и задержки, причем сигнальный вход соединен через сумматор с прямым вхо- дом селектора нижнего приближения и с инверсными входами селекторов поиска установившегося уровня и верхнего приближения, выход блокировки через

г 0 5

5 0 5

0

элемент задержки соединен с выходом второго разряда счетчика установления и с входом первого логического инвертора, выход которого соединен с входами селекторов нижнего и верхнего приближения, резисторного делителя , подключен к выходу источника опорного напряжения, первый выход резисторного делителя соединен с инверсным входом селектора нижнего приближения, прямым входом подключенного через второй одновибратор к одному из входов элемента ИЛИ, к входу вычитания реверсивного счетчика установившегося значения, а через N-й логический инвертор и триггер - к одному из входов элемента 2И, второй и третий выходы резисторного делителя соединены с прямыми входами соответственно селекторов поиска установившегося уровня и верхнего приближения, прямой выход верхнего приближения через третий одновибратор соединен с другими из входов элементов ИЛИ и 2И и с входом сумми-- рования счетчика установившегося значения, а прямой выход селектора поиска установившегося уровня через четвертый одновибратор соединен со счетным входом счетчика установления, входом установки подключенного к выходу элемента ИЛИ, выход элемента 2И соединен со счетным входом счетчика i выброса, выходы которого подключены к входам первого слагаемого логического сумматора, с входами второго слагаемого которого через N-1 логических инверторов соединены входы цифроаналогового преобразователя и выходы счетчика установившегося значения, выход цифроаналогового преобразователя соединен с выходом установления блока, а через аналого-, вый инвертор - с другим входом сумматора, выходы логического сумматора и выходы счетчика установившегося значения соединены с входами делимого и делителя соответственно арифме- тическо-логического блока.

| Устройство для измерения времени установления электрического сигнала | 1981 |

|

SU1019392A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-10-07—Публикация

1987-03-16—Подача