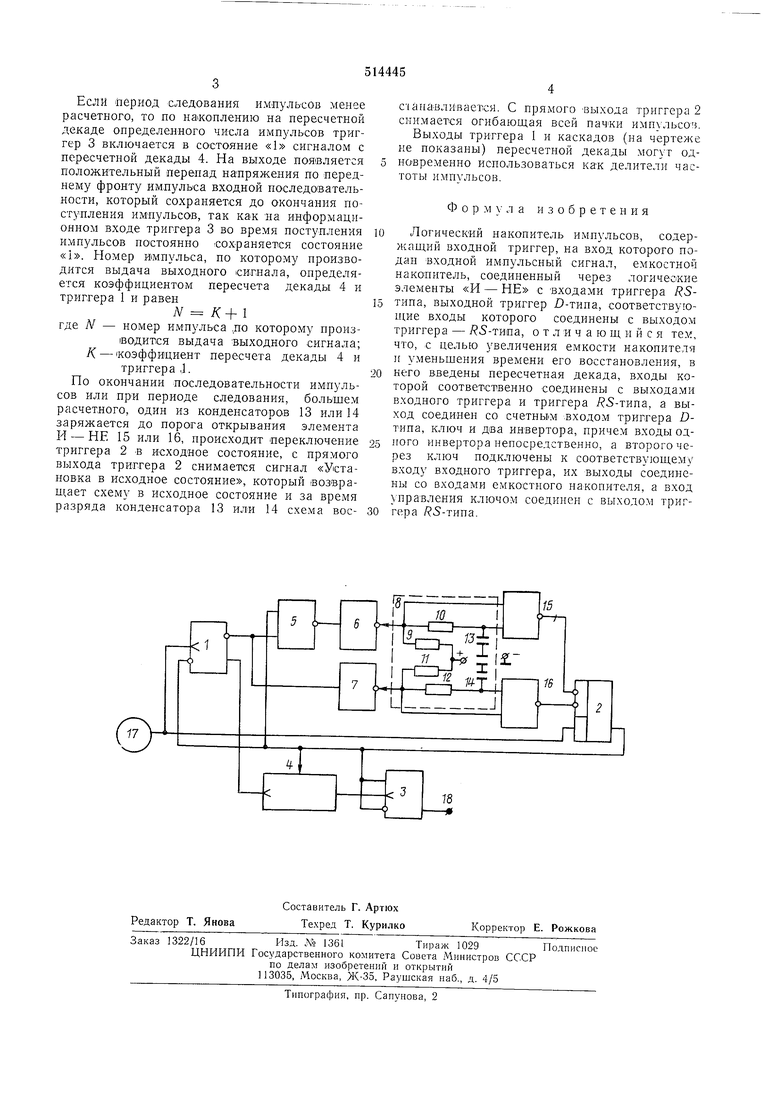

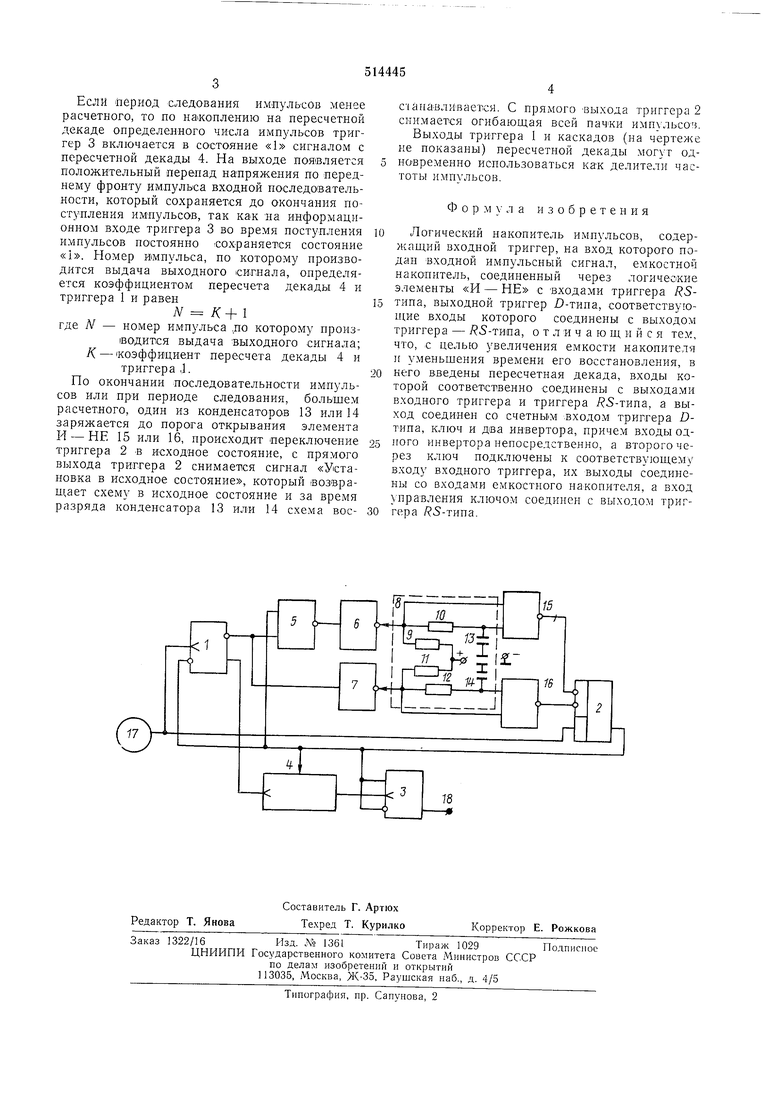

(54) ЛОГИЧЕСКИЙ НАКОПИТЕЛЬ ИМПУЛЬСОВ

Если период следования импульсов менее расчетного, то по накоплению на пересчетной декаде определенного числа импульсов триггер 3 включается в состояние «1 сигналом с пересчетной декады 4. На выходе появляется положительный перепад напряжения по переднему фронту импульса входной последовательности, который сохраняется до окончания поступления импульсов, так как на информационном входе триггера 3 во время ноступления импульсов постоянно сохраняется состояние «i. Номер импульса, по которому производится выдача выходного сигнала, определяется коэффициентом пересчета декады 4 и триггера 1 и равен

N

где N - номер импульса ,по которому производится выдача выходного сигнала; /С - коэффициент пересчета декады 4 и

триггера ,1.

По окончании последовательности импульсов или при периоде следования, большем расчетного, один из конденсаторов 13 или 14 заряжается до порога открывания элемента И - НЕ 15 или 16, происходит переключение триггера 2 -в исходное состояние, с прямого выхода триггера 2 снимает1ся сигнал «Установка в исходное состояние, который возвращает схему в исходное состояние и за время разряда конденсатора 13 или 14 схема воеС1анаВливается. С прямого выхода триггера 2 снимается огибающая всей пачки импульсоч. Выходы триггера 1 и каскадов (на чертеже не показаны) пересчетной декады могут одновременно использоваться как делители частоты импульсов.

Формула изобретения

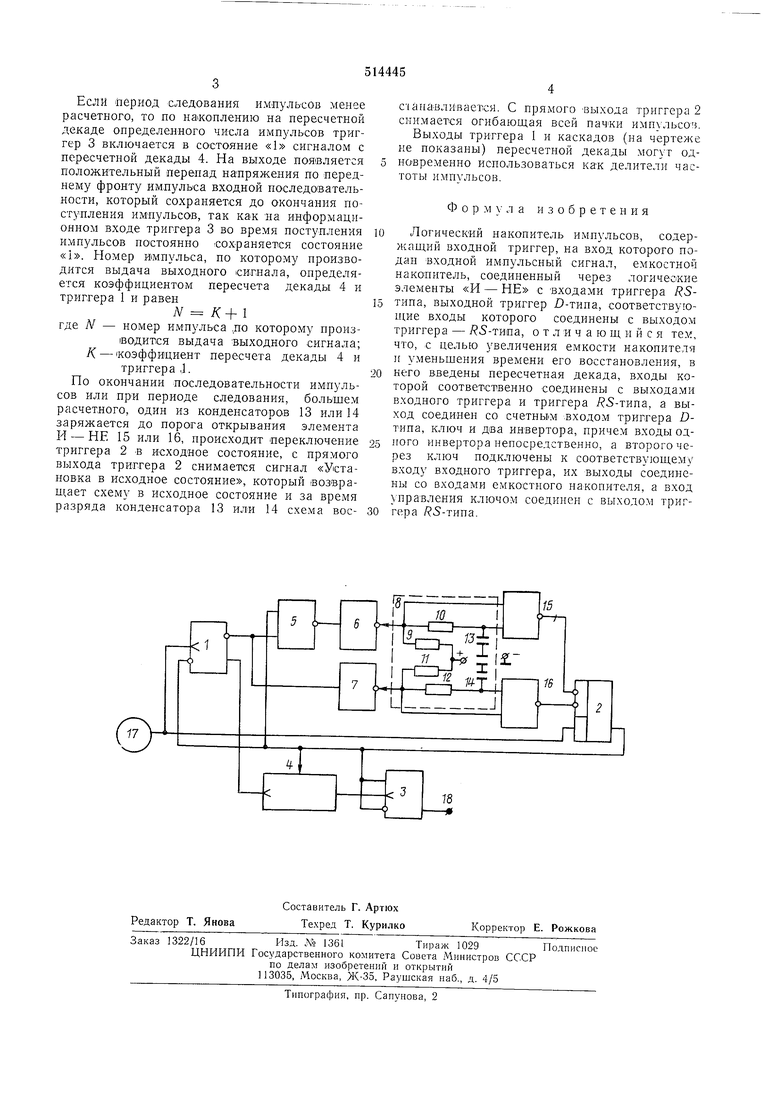

Логический накопитель импульсов, содержащий входной триггер, на вход которого подан входной импульсный сигнал, емкостной накопитель, соединенный через логические элементы «И - НЕ с входами триггера RSтипа, выходной триггер D-тииа, соответствуюИ1,ие входы которого соединены с выходом триггера - / 5-типа, о т л и ч а ю щ и и с я тем, что, с целью увеличения емкости накопителут и уменьпления времени его восстановления, в него введены пересчетная декада, входы которой соответственно соединены с выходами входного триггера и триггера RS-nna, а выход соединен со счетныМ входом триггера Dтипа, ключ и два инвертора, причем входы одного инвертора непосредственно, а второго через ключ подключены к соответствующему входу входного триггера, их выходы соединены со входами емкостного накопителя, а вход управления ключом соединен с выходом триггера / 5-типа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический накопитель импульсов | 1976 |

|

SU566361A2 |

| Логический накопитель импульсов | 1978 |

|

SU739746A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1973 |

|

SU383085A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU687578A1 |

| ДЕКАДНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1973 |

|

SU372706A1 |

| УСТРОЙСТВО для СЧЕТА ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1971 |

|

SU311406A1 |

| РЕГУЛИРУЕМОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО ДЛЯ | 1970 |

|

SU264458A1 |

| Коммутатор | 1981 |

|

SU1014145A1 |

| Фазоимпульсный счетчик | 1975 |

|

SU524323A1 |

| Устройство для синхронизации системы управления преобразователем | 1988 |

|

SU1658316A1 |

Авторы

Даты

1976-05-15—Публикация

1975-02-14—Подача