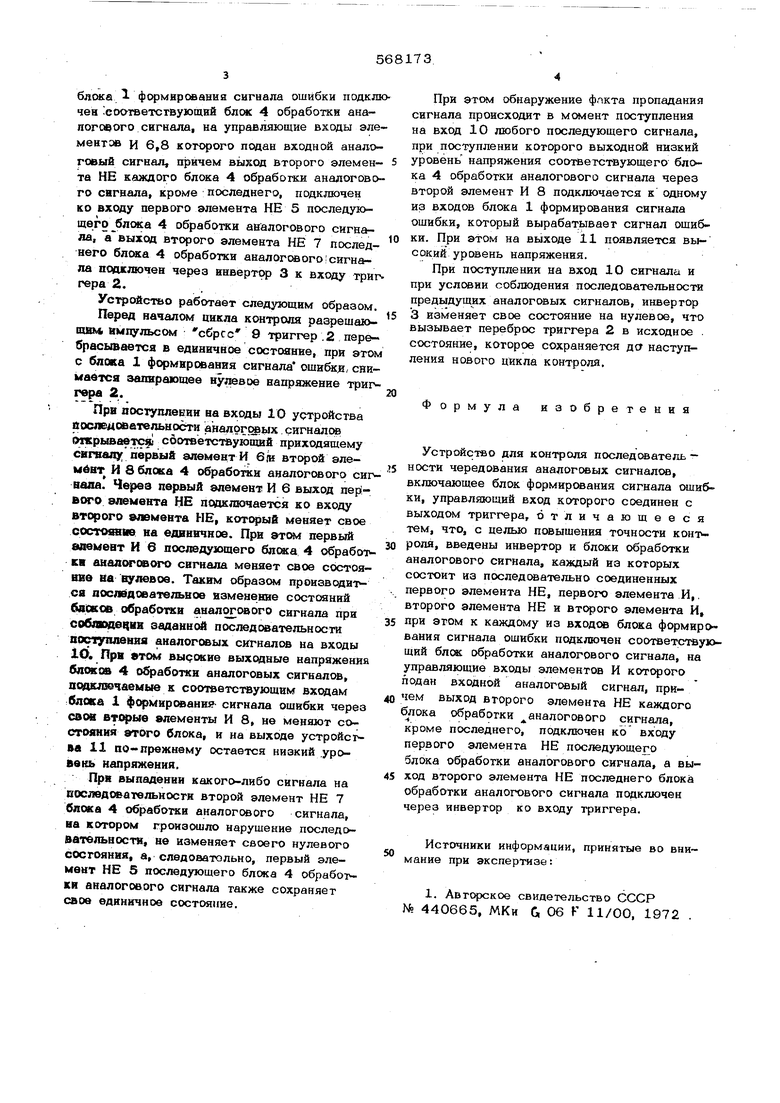

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ ЧЕРЕДОВАНИЯ АНАЛОГШЫХ СИГНАЛОВ блока 1 формирования сигнала ошибки подкл чен соо гветсгвуюший блс« 4 обработки аналогового сигнала, иа управляющие входы эле меитов и 6,8 которого подан входной анало говый сигнал, причем выход второго элемен та НЕ каждого блока 4 обрабопш аналогово го сигнала, кроме последнего, подключен ко входу первого элемента НЕ 5 последующего бпжа 4 обработки аналогового сигнала, Vвыход второго элемента НЕ 7 последиего блока 4 обработки аналогового сигнала псдключен через инвертор 3 к входу три гера 2. Устройство работает следующим образом Перед началом цикла контроля разрешаюпшм импульсом сбрсс 9 триггер .2 пере брасывается в единичное состояние, при это с блока 1 формирования сигнала ошибк г, сни мается запирающее нушвое напряжение триг гера 2. При поступлении на входы 10 устройства йослемовательноёти аналоговых сигналов (хгкрываетс соответствующий приходящему cBre&iqrпервый элемент И бк второй элемент И 8 блока 4 обработки аналогового сиг вала Через первый элемент И 6 выход nepiвого алюмента НЕ пооключается ко входу второго влемента НЕ, который меняет свое состоввне на едвввчное. При 9ТСМ первый аяемевт И 6 последующего блока 4 обработ ке аналогового сигнала меняет свое состоявве ва вулевое. Таким образом производится последовательное изменение состсяний блоков обрабопси аналогового сигнала при собякщвции заданной последовательности поетуплевия аналоговых сигналов на входы id. Прв втом вырсжие выходные напряжения блоков 4 обработки аналоговых сигналов, подключаемые к соответствующим входам блока 1 формировани - сигнала ошибки через своа элементы И 8, не меняют ct стояния этого блока, и на выходе устройсглл 11 по-прежнему остается низкий уровень напряжения. Пря выпадении какого-либо сигнала на последовательности второй элемент НЕ 7 блока 4 обработки аналогового сигнала, ва котором гроизошло нарушение последовательности, не изменяет своего нулевого состояния, а, следовательно, первый элемент НЕ 5 последующего блока 4 обработ кн аналогового сигнала также сохраняет свое единичное состояние. При этом обнаружение фпкта пропадания сигнала происходит в момент поступления на вход 10 любого последующего сигнала, при поступлении которого выходной низкий уровень напряжения соответствующего блока 4 обработки аналогового сигнала через второй элемент И 8 подключается к одному из входов блока 1 формирования сигнала ошибки, который вырабатывает сигнал ошибки. При этом на выходе 11 появляется высокий уровень напряжения. При поступлении на вход 10 сигнала и при условии соблюдения последовательности предыдущих аналоговых сигналов, инвертор 3 изменяет свое состояние на нулевое, что вызывает переброс триггера 2 в исходное . состояние, которое сохраняется дет наступления нового цикла контроля. Формула изобретения Устройство для контроля последователь - кости чередования аналоговых сигналов, включающее блок формирования сигнала ошибки, управляющий вход которого соединен с выходом триггера, отличающееся тем, что, с пелью повышения точности контроля, введены инвертор и блоки обработки аналогового сигнала, каждый из которых состоит из последовательно соединенных первого элемента НЕ, первого элемента И,. второго элемента НЕ и второго элемента И, при этом к каждому из входов блока формирования сигнала ошибки подключен соответствующий блок обработки аналогового сигнала, на управляющие входы элементов И которого подан входной аналоговый сигнал, причем выход второго элемента НЕ каждого блока обработки аналогового сигнала, кроме последнего, подключен ко входу первого элемента НЕ последующего 5лока обработки аналогового сигнала, а выход второго элемента НЕ последнего блока обработки аналогового сигнала подключен через инвертор ко входу триггера. Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР № 440665, МКи G 06 К 11/00, 1972 .

ОО . е OfO

О JO

о to

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности прохождения сигналов | 1982 |

|

SU1030804A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1986 |

|

SU1363494A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1977 |

|

SU680183A1 |

| Регистратор последовательности логических сигналов | 1983 |

|

SU1108467A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1984 |

|

SU1203712A1 |

| Устройство для автоматического контроля и поиска неисправностей | 1977 |

|

SU696463A1 |

| Устройство для контроля выполненияпОСлЕдОВАТЕльНОСТи дЕйСТВий ОпЕРАТОРА | 1978 |

|

SU807300A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1984 |

|

SU1238257A1 |

| Измерительный прибор | 1988 |

|

SU1589072A1 |

| Устройство для измерения рассогласования между углом и кодом | 1985 |

|

SU1277397A1 |

Авторы

Даты

1977-08-05—Публикация

1975-12-08—Подача