Изобретение относится к технике контроля систем связи и может быть использовано, в частности, в тренажерах с жестким алгоритмом работы оператора.

Цель изобретения - расширение области применения путем контроля последовательности устранения ошибки в чередовании аналоговых сигналов.

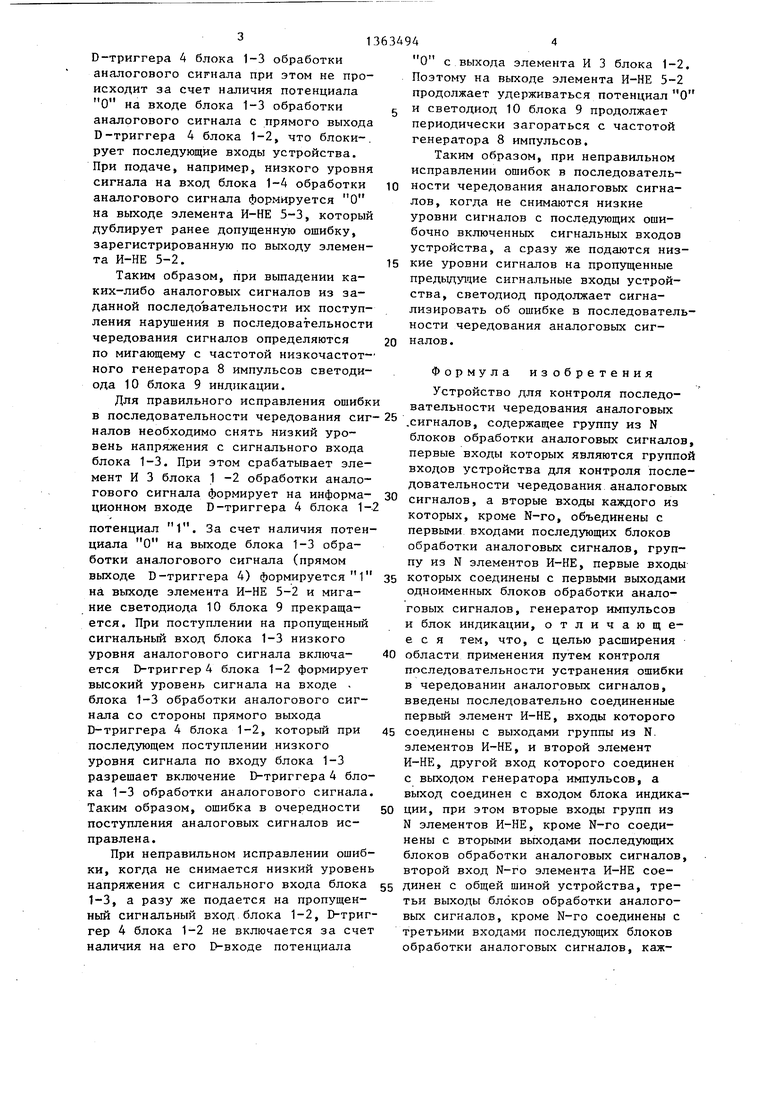

На чертеже представлена электрическая структурная схема устройства для контроля последовательности чередования аналоговых сигналов.

Устройство для контроля последовательности чередования аналоговых сигналов содержит группу N блоков 1-1 - 1-N обработки аналоговых сигналов, кадлый из которых состоит из элемента НЕ 2, элемента И 3 и

В-триггера4 группу из N элементов И-НЕ 5-1 - 5-N, первьй элемент И-НЕ 6 второй элемент И-НЕ 7, генератор 8 импульсов и блок 9 индикации, состоящий из светодиода 10 и резистора 11.

Устройство для контроля последовательности чередования аналоговых сигналов работает следующим образом.

В исходном состоянии на всех входах блоков 1-1 - 1-N обработки аналогового сигнала присутствуют высокие уровни входных аналоговых сигналов. Поэтому D-триггеры 4. за счет наличия на их входах установки нуля ВБЮОКИХ потенциалов находятся в нулевом сос- т(янии. При этом на их инверсных выходах присутствуют потенциалы 1, а на прямых выходах присутствуют потенциалы О.

На выходах инверторов 2 присутствуют потенциалы О, поэтому на выходах элементов И-НЕ 5-1 - 5-N-формируются потенциалы 1, которые поступают на входы первого элемента И-НЕ 6, что вызывает формирование на его выходе потенциала О. Соответственно на выходе второго элемента И-НЕ 7 присутствует потенциал Ч и светодиод 10 блока 9 индикации не горит. На выходе элемента И 3 блока 1-1 обработки аналогового сигнала присутствует потенциал 1 за счет наличия 1 на его другом входе. При поступлении на сигнальный вход низкого уровня аналогового сигнала снимается блокировка с R-входа Е-триггера 4 и с задержкой на время срабатывания элемента НЕ 2 на С-входе D-триггера формируется логический перепад, по которому D-триггер 4 срабатывает, так как на его информационном входе присутствует потенциал

1 с выхода элемента И 3, что вызывает появление 1 на втором выходе блока 1-1 обработки аналогового сигнала. Однако сигнал на выходе элемента И-НЕ 5-1 не меняется и светодиод

10 блока 9 индикации, сигнализирующий об ошибках в последовательности чередования аналоговых сигналов, не горит.

При включении D-триггера 4 блока

1-1 обработки аналогового сигнала срабатывает элемент И 3 блока 1-2 обработки аналогового сигнала, который формирует потенциал 1 на D-входе D-триггера 4 блока 1-2, который

включается при появлении низкого

уровня на сигнальном входе. При этом формируется сигнал 1 на выходе блока 1-2 обработки аналогового сигнала, по которому элемент И 3 блока

обработки аналогового сигнала,

формирует на входе D-триггера 4 блока 1-2 и сигнал О на выходе блока 1-2 обработки аналогового сигнала. Однако сигнал на выходе элемента И-НЕ 3-2 не меняется и светодиод 10 блока 9 индикации, сигнализирующий об ошибках в последовательности чередования аналоговых сигналов, не горит.

Таким образом, при соблюдении заданной последовательности поступления аналоговых сигналов происходит срабатывание D-триггеров 4 в блоках 1-1 - 1-N в соответствии с заданной Последовательностью и светодиод 10 блока

9 индикации не загорается.

При вьтадении из контролируемой последовательности чередования аналоговых сигналов сигнала, например, на выходе блока 1-2 и при появлении

низкого уровня на входе блока 1-3 (ошибочное включение) формируется сигнал О на выходе элемента И-НЕ 5-2, который вызывает появление уровня 1 на выходе первого элемента

И-НЕ 7, разрешающий прохождение импульсов тактовой частоты с выхода генератора 8 импульсов на выход второго элемента И-НЕ 7. При этом светодиод 10 блока 9 индикации начинает

периодически загораться с частотой, раврой частоте импульсов генератора 8, сигнализируя тем самым о вьтадении из заданной последовательности пре- дьщущего сигнала. Однако включения

D-триггера 4 блока 1-3 обработки аналогового сигнала при этом не происходит за счет наличия потенциала О на входе блока 1-3 обработки аналогового сигнала с прямого выхода D-триггера 4 блока 1-2, что блоки-. рует последующие входы устройства. При подаче, например, низкого уровня сигнала на вход блока 1-4 обработки аналогового сигнала форхчируется О на вькоде элемента И-НЕ 5-3, который дублирует ранее допущенную ошибку, зарегистрированную по выходу элемента И-НЕ 5-2,

Таким образом, при выпадении каких-либо аналоговых сигналов из заданной последовательности их поступления нарушения в последовательности чередования сигналов определяются по мигающему с частотой низкочастотного генератора 8 импульсов светоди- ода 10 блока 9 индикации.

Для правильного исправления ошибк

Устройство для контроля послед вательности чередования аналоговы

в последовательности чередования сиг- 25 .сигналов, содержащее группу из N

30

налов необходимо снять низкий уровень напряжения с сигнального входа блока 1-3. При этом срабатывает элемент И 3 блока 1 -2 обработки аналогового сигнала формирует на информационном входе D-триггера 4 блока 1-2

потенциал 1. За счет наличия потенциала О на выходе блока 1-3 обработки аналогового сигнала (прямом выходе D-триггера 4) формируется 1 35 на выходе элемента И-НЕ 5-2 и мигание светодиода 10 блока 9 прекращается. При поступлении на пропущенный сигнальный вход блока 1-3 низкого уровня аналогового сигнала включается D-триггер4 блока 1-2 формирует высокий уровень сигнала на входе - блока 1-3 обработки аналогового сигнала со стороны прямого выхода D-триггера 4 блока 1-2, который при последующем поступлении низкого уровня сигнала по входу блока 1-3 разрешает включение D-триггера 4 блока 1-3 обработки аналогового сигнгша. Таким образом, ошибка в очередности поступления аналоговых сигналов исправлена.

При неправильном исправлении ошибки, когда не снимается низкий уровень

блоков обработки аналоговых сигна первые входы которых являются гру входов устройства для контроля по довательности чередования аналого сигналов, а вторые входы каждого которых, кроме N-ro, объединены с первыми входами последующих блоко обработки аналоговых сигналов, гр пу из N элементов И-НЕ, первые вх которых соединены с первыми выход одноименных блоков обработки анал говых сигналов, генератор импульс и блок индикации, отличающ еся тем, что, с целью расширен области применения путем контроля последовательности устранения оши в чередовании аналоговых сигналов введены последовательно соединенн первый элемент И-НЕ, входы которо

45 соединены с выходами группы из N. элементов И-НЕ, и второй элемент И-НЕ, другой вход которого соедин с выходом генератора импульсов, а выход соединен с входом блока инд

50 ции, при этом вторые входы групп N элементов И-НЕ, кроме N-ro соед нены с вторыми выходами последующ блоков обработки аналоговых сигна второй вход N-ro элемента И-НЕ со

40

напряжения с сигнального входа блока 55 динен с общей шиной устройства, тре- 1-3, а разу же подается на пропущен- тьи выходы блоков обработки аналого- ный сигнальный вход блока 1-2, D-триг- вых сигналов, кроме N-ro соединены с гер 4 блока 1-2 не включается за счет третьими входами последующих блоков наличия на его D-входе потенциала обработки аналоговых сигналов, каж

634944

О с выхода элемента И 3 блока 1-2. Поэтому на выходе элемента И-НЕ 5-2 продолжает удерживаться потенциал О

g и светодиод 10 блока 9 продолжает периодически загораться с частотой генератора 8 импульсов.

Таким образом, при неправильном исправлении ошибок в последователь10 ности чередования аналоговых сигналов, когда не снимаются низкие уровни сигналов с последующих ошибочно включенных сигнальных входов устройства, а сразу же подаются низ15 кие уровни сигналов на пропущенные предыду1чие сигнальные входы устройства, светодиод продолжает сигнализировать об ошибке в последовательности чередования аналоговых сиг- налов.

Формула изобретения

Устройство для контроля последовательности чередования аналоговых

.сигналов, содержащее группу из N

0

5

блоков обработки аналоговых сигналов, первые входы которых являются группой входов устройства для контроля последовательности чередования аналоговых сигналов, а вторые входы каждого из которых, кроме N-ro, объединены с первыми входами последующих блоков обработки аналоговых сигналов, группу из N элементов И-НЕ, первые входы которых соединены с первыми выходами одноименных блоков обработки аналоговых сигналов, генератор импульсов и блок индикации, отличающееся тем, что, с целью расширения области применения путем контроля последовательности устранения ошибки в чередовании аналоговых сигналов, введены последовательно соединенные первый элемент И-НЕ, входы которого

5 соединены с выходами группы из N. элементов И-НЕ, и второй элемент И-НЕ, другой вход которого соединен с выходом генератора импульсов, а выход соединен с входом блока индика0 ции, при этом вторые входы групп из N элементов И-НЕ, кроме N-ro соединены с вторыми выходами последующих блоков обработки аналоговых сигналов, второй вход N-ro элемента И-НЕ сое0

1363494

дый из которых содержит элемент НЕ,С-вход которого соединен с выходом

вход которого является первым входомэлемента НЕ и является вторым выходом

блока обработки аналогового сигнала,блока обработки аналогового сигнала,

элемент И, первый вход которого, кро-R-вход которого объединен с входом

ме N-ro блока обработки аналоговогоэлемента НЕ, а D-вход соединен с

сигнала, является вторым входом бло-выходом элемента И, второй вход котока обработки аналогового сигнала,рого в первом блоке обработки аналовторой вход, кроме первого .блока об-гового сигнала и первый вход в N-M

работки аналогового сигнала, являет- Qблоке обработки аналогового сигнала

ся третьим входом блока обработкиявляется сигналом задания уровня

аналогового сигнала, и D-триггер,логической единицы.

Составитель Э. Борисов .Рвда;ктор Т. Лаэоренко Техред М.Ходанич Корректор С. Черни

Заказ 6382/55Тираж 636Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистратор последовательности логических сигналов | 1983 |

|

SU1108467A1 |

| Устройство для контроля последовательности прохождения сигналов | 1982 |

|

SU1030804A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1983 |

|

SU1099394A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1984 |

|

SU1203712A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1977 |

|

SU680183A1 |

| Устройство для индикации аналоговых сигналов | 1986 |

|

SU1446647A1 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Устройство для определения объема контролируемых параметров | 1984 |

|

SU1168903A1 |

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2029352C1 |

Изобретение может быть использовано в тренажерах с жестким алгоритмом работы оператора. Цель изобретения - расширение области применения путем контроля последовательности устранения ошибки в чередовании аналоговых сигналов (ЧАС). Устройство содержит группу из блоков 1-1-1-N обработки аналоговых сигналов каждый из которых состоит из элемента НЕ 2, элемента И 3 и D-триггера 4, группу из N элементов И-НЕ 5-1 - 5-N, элементы И-НЕ 6 и 7, генератор 8 импульсов и блок 8 индикации, состоящий из светодиода 10 и резистора 11. При неправильном исправлении ошибок в последовательности ЧАС, когда не снимаются низкие уровни с сигналов с последующих ошибочно включенных сиг- - нальных входов устройства, а сразу же подаются низкие уровни сигналов на пропущенные предьщущие сигнальные входы устройства, светодиод 10 продолжает сигнализировать об опшбке в последовательности ЧАС. 1 ил. сл

| Устройство для контроля последовательности чередования аналоговых сигналов | 1977 |

|

SU680183A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1983 |

|

SU1099394A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-20—Подача