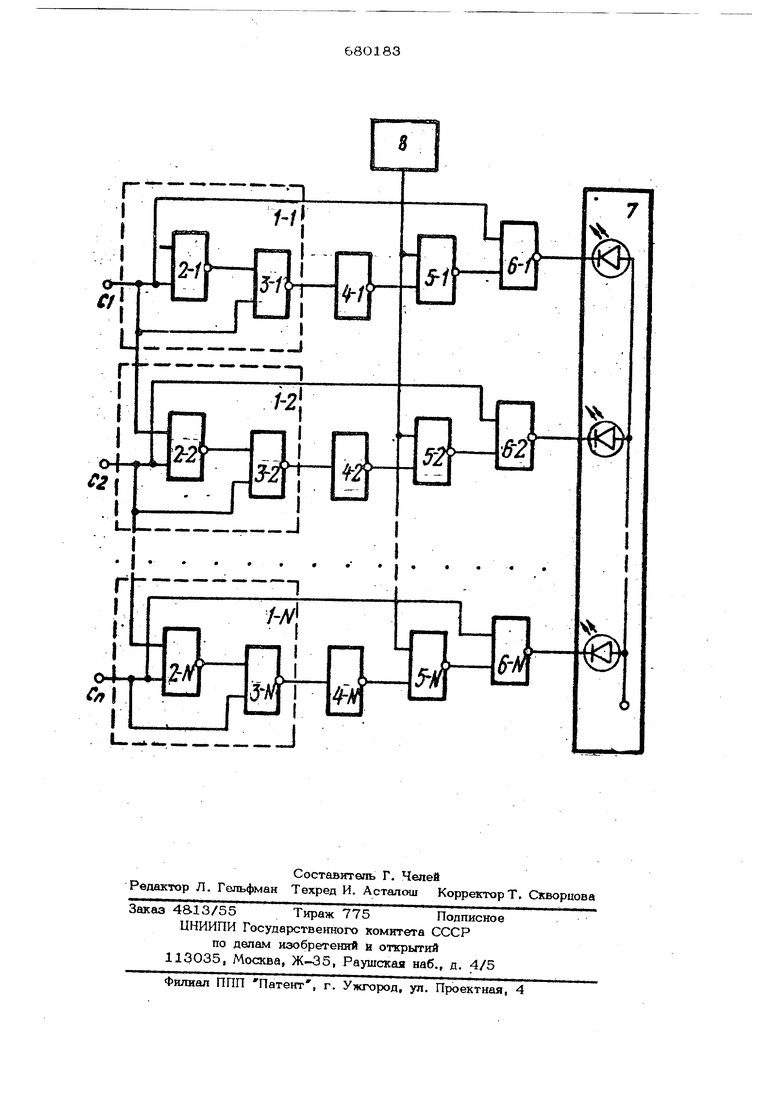

Изобретение относится к устройствам контроля систем связи и может использоваться в автоматике и вычислительной технике. Известно устройство для контроля последовательности чередования аналоговых сигналов, содрежащее N блоков обработки аналогового сигнала, каждый из котогрых содержит первый и второй двухвхо-довые элементы И-НЕ, первые входы которых объединены и являются входом блока обработки аналогового сигнала, причем выход первого элемента И-НЕ подключен к второму входу второго элемента И-НЕ, а каждый вход предыдущего блока обработки аналогового сигнала объединен с вторым входом первого элемента И-НЕ последующего блока обработки аналогового сигнала, выход каждого второго элемента И-НЕ является выходом блока обработки аналогового сигнала, и блок отображения ин(}юрмации l. Однако известное устройство имеет невысокую точность контроля, так как в нем фиксируется лишь факт появления сигнала ошибки, а не пропуск каких-либо аналоговых сигналов в чередовании к оп- ределение того сигнала, на котором произошло нарушение последовательности чередования. Целью изобретения является повышение точности контроля. Для этого в устройство для контроля последовательности чередования аналоговых сигналов, содержащее N блоков обработки аналогового сигнала, каждый из которых содержзгг первый и второй двухвходовые элементы И-НЕ, первые входы которых объединены и являются входом блока обработки аналогового сигнала, причем выход первого элемента И-НЕ подключен к второму входу второго элемента И-НЕ, а каждый вход предьщутцего блока обработки аналогового сигнала объединен с вторым входом первого элемента И-НЕ последующего блока обработки аналогового сигнала, выход каждого второго элемента И-НЕ является выходом блока обработки аналогового сигнала, и блок отображения информации, введены низкочастотный генератор, N инверторов, N третьих и N четвертых двухвходовых элементов И-НЕ, при этом выход каждого блока обработки аналогового сигнала подключен через инвертор к первому входу одного из N третьих элементов И-НЕ, вторые входы которых объединены с выходом низкочастотного генератора, первый вход каждого из N четвертых элементов И-НЕ соединен с входом соответствующего блока обработки аналогового сигнала, а второй вход - с выходом одного из N -третьих элементов И-НЕ, вьхход каждого из N четвертых элементо И-НЕ подключен к соответствующему входу блока отображения информации. На чертеже представлена структурная электрическая предложенного устройства. Устройство для контроля последовател ности чередования аналоговых сигналов содержит N блоков обработки аналоговог сигнала 1 (1-1...1- N), каждый из кото рых содержит первый 2 (2-1.,.2- N ) и второй 3 (3-U...3- N } двухвходовые элементы И-НЕ, N инверторов 4 (4-1... 4- N ), N третьих и N четвертых двухвходовых элементов И-НН 5 (5-1...5-N и 6 (6-1...6- N) соответственно, блок отображения информации 7 и низкочастот ный генератор 8. Предложенное устройство работает сле дующим образом. В исходном состоянии на всех входах блоков обработки аналогового сигнала 1 присутствуют низкие уровни входных С. С аналоговых сигналов. Поэтому в исходном состоянии все двухвходовые элементы И-НЕ 2, 3, 5 и устройства за счет наличия на их входах нулевых уровней напряжения находятся в единичном состоянии, а инверторы 4 за счет наличия на его входах высоких уров ней напряжения находятся в нулевом состоятш. При Постутшенин на входы блоков обра ботки аналогового сшнала 1 высоких уровней аналоговых сигналов С1...Сц в соответствии с заданной последовательностью их чередования первый двухвходо- вый элемент И-НВ 2, на который приходит аналоговый сигнал, перебрасывается в нулевое состояние, а второй двухвходовы элемент И-НЕ 3 за счет наличия на первом его входе низкого уровня напряжения Первого двухвхоаового элемента И-НН 2 остается в единичном состоянии. Первый инвертор 4 (4-1) и третий двухвходовый элемент И-НЕ 5 при этом также остаются в исходном состоянии, а четвертый двухвходовый элемент И-НЕ 6 за счет наличия на его входах высокого уровня соответствующего входного аналогового сигнала и высокого выходного уровня третьего двухвходового элемента И-FiE перебрасьюается в нулевое состояние , и в блоке отображения информации 7, вьтолненном, например, на светодио- дах, загорается соответствующий приходящему аналоговому сигналу светодиод. При этом каждым предыдущим входным аналоговым сигналом производится подготовка к работе первого двухвходового элемента. И-НЕ 2 последующего блока обработки аналогового сигнала 1. Таким образом, при соблюдении заданной посл. довательностй следования аналоговых сигналов С1...Сп производится последовательное изменение состоянии первых двухвходовых элементов И-НЕ 2 блоков обработки аналогового сигнала 1 и в соответствии с заданной последовательностью свечение светодиодов блока отображения информации 7. При вьтаденми из контролируемой последовательности чередования аналоговых сигналов одного или нескольких сигналов, первый двухвходовый элемент И-НЕ 2 блока обработки аналогового сигнала, на котором произошло нарушение последовательности, не изменяет своего единичного состояния, а второй двухвходовой элемент И-НЕ 3 блока обработки аналогового сигнала за счет появления на его втором входе высокого уровня входного аналогового сигнала изменяет свое состояние на нулевое. При этом инвертор 4 изменяет свое состояние на единичное и своим высоким выходным уровнем напряжения по первому входу третьего двухвходового элемен-. та И-НЕ 5 разрёщает прохождение низкочастотных импульсов с низкочастотного генератора 8 на первый вход четвертого двухвходового элемента И-НЕ 6, на втором входе которого присутствует высокий уровень того входного аналогового сигнала, на котором произощло нарушение последовательности чередования сигналов. С выхода четвертого двухвходового элемента И-ЯЕ б низкочастотные импушсы поступают на соответствующий светодиод, который будет периодически загораться с частотой, равной частоте низкочастотного генератора 8. Таким образом, при выпадении какихлибо аиалоговых С1..,Сп сигналов из за- данной последовательности их следования обнаружение нарушения последовательност чередования сигналов определяется по ми гающим с частотой низкочастотного гeн& ратора 8 и соответс.твующкм месту нару,шения чередования сигналов светояиодагл блока отображения информации 7. Возврат устройства в исходное состояние осуществляется подачей на все вхо- ды блоков обработки аналогового сигнала низких уровней аналоговых С1,,.Сп сигналов. Предложенное устройство имеет высокую точность контроля, надежно в работе компактно и просто по конструкхши, обладает высокой информативностью и может быть выполнено на однотипных логических элементах с повышенным уровнет 1 интеграции. Формула изобретения Устройство для контроля последовательности чередования аналоговых сигналов, содержащее N блоков обработки аналогового сигнала, каждый из которых содержит первый и второй двухвходовые элементы И-НЕ, первые входы которых объединены и являются входом блока обработки аналогового сигнала, причем выход первого элемента И-НЕ подключен квторомувхэо- ду второго элемента И-НЕ, а каждый вход предыдущего блока обработки аналогового сигнала объединен с вторым входом первого элемента И-НЕ последующего блока обработки аналогового сигнала, выход каждого второго элемента И-НЕ является выходом блока обработки аналогового сигнала, и блок отображения информации, отличающееся тем, что, с целью повышения точности контроля, введены низкочастотный генератор, N инверторов, Н третьих и N четве1 тых двухвходовых элементов И-НЕ, при этом выход каждого блока обработки аналогового сигнала подключен через инвертор к первому входу одного из N третьих элементов И-НЕ, вторые входы которых объединены с выходом низкочастотного генератора, первый вход каждого из N четвертых элементов И-НЕ соединен с входом соответствующего блока обработки аналогового сигнала, а второй вход - с выходом одного из N третьих элементов И-НЕ, выход каждого из N четвертых элйv eнтoБ И-НЕ подключен к соответствующему входу блока отображения информации. Источники информации, прин5гтые во внимание при экспертизе 1. Авторское свидетельство СССР № 568173. кл. Н 04 В 17/ОО, 1975. L, J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности чередования аналоговых сигналов | 1984 |

|

SU1203712A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1986 |

|

SU1363494A1 |

| Регистратор последовательности логических сигналов | 1983 |

|

SU1108467A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1983 |

|

SU1099394A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1987 |

|

SU1492482A2 |

| СИСТЕМА БЕСПЕРЕБОЙНОГО ЭЛЕКТРОПИТАНИЯ | 1992 |

|

RU2037249C1 |

| МНОГОУРОВНЕВЫЙ АНАЛИЗАТОР-РЕГИСТРАТОР НАПРЯЖЕНИЯ ИСТОЧНИКА ПОСТОЯННОГО ТОКА | 1991 |

|

RU2046357C1 |

| Устройство для автоматического контроля и поиска неисправностей | 1977 |

|

SU696463A1 |

| Устройство для контроля последовательности чередования аналоговых сигналов | 1975 |

|

SU568173A1 |

| Широтно-импульсный N-фазный инвертор | 1989 |

|

SU1815776A1 |

Авторы

Даты

1979-08-15—Публикация

1977-12-30—Подача