1

Изобретение относится к телемеханике и технике связи. Оно может быть использо вано при проектировании декодирующих yci ройств для каналов с коррекцией ошибок.

Известны устройства для декодирования линейных кодов, содержащие приемный регистр, сумматор по модулю два, комму татор и пороговый элемент.

В этих устройствах используют порого вый элемент с жестким значением порога, поэтому все символы декодируются с одинаковой степенью верности.

Известно также устройство, выполншэщее посимвольное декодирование с учетом важ ности определенных символов. Расширение функциональных возможностей этого устройсва достигается тем, что в него введены двоичный счетчик, счетный вход которого подключен к выходу сумматора по модулю два, дешифратор, входы которого соедннены с разрядами счетчика, а выходы объединены через элементы ИЛИ в группы в соответствии со значениями порогов для декодируемых символов, определяемых структурой кода. Выход каждого элемента ИЛИ подключен ко входу соответствующего элемента .совпадения.

Это устройство не полностью реализует возможности кода корректировать ошибки.

Цель изобретения « увеличения веройтности безошибочного декодирования - доств гается тем, что в устройство, содержащее двоичный счетчик, дешифратор, сумматор по модулю два , элементы ИЛИ, ключ, введе ны дополнительны© юэочй ясдвиговой рв ГЕСтр, вход которого подключен к соответствующему входу устройства, а входы разрядов этого регистра через дополнительные клочи соединены со входом сумматора по модулю два.

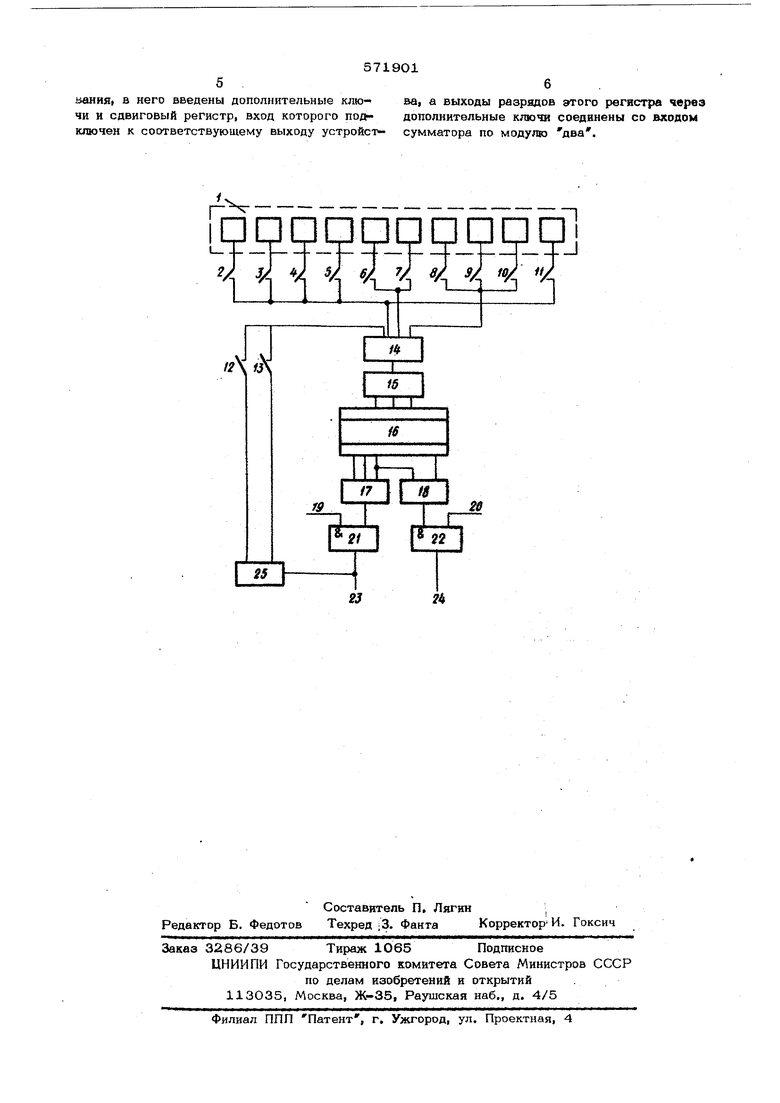

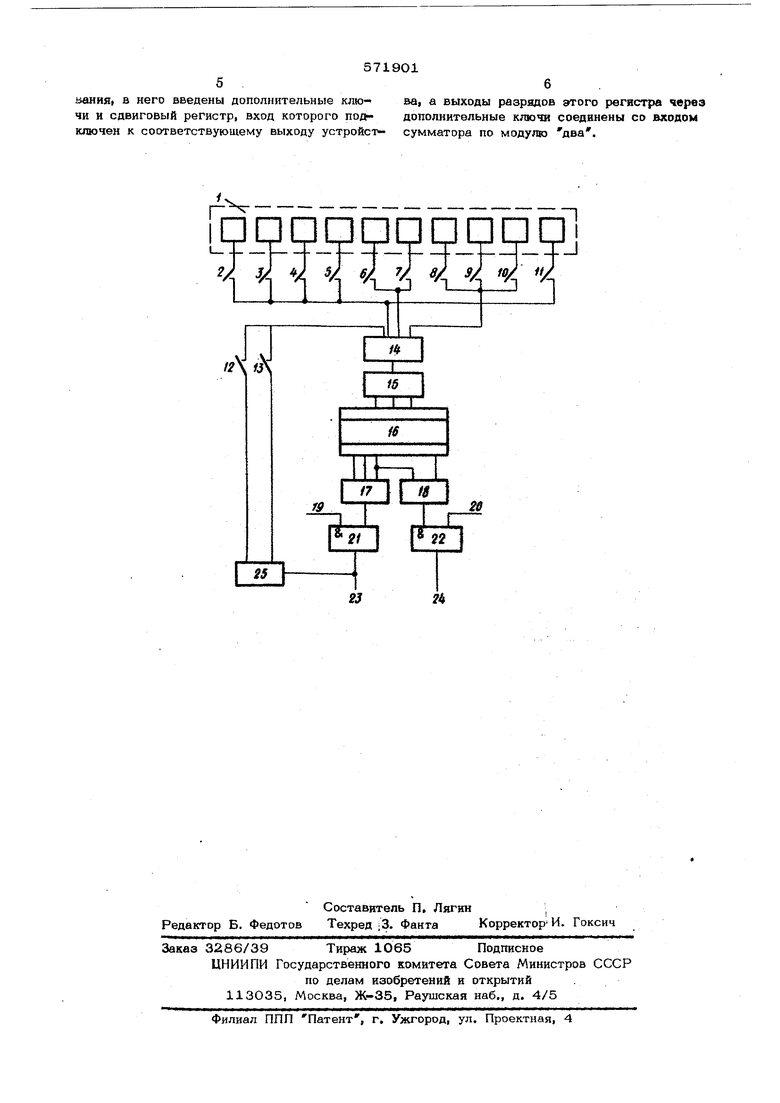

На чертеже изображена структурнйя схема устройства.

Устройство содержит приемный регистр 1 ключи 2-13 коммутатора, сумматор 14 по модулю двоичный счетчик 15, Дешифратор 16, элементы ИЛИ 17, 18, вхош1ые шины 19, 2О, элементы совпадения 21, 22, выходные шины 23, 24 и сдвиговый регистр 25. Сущность предложения поясняется на примере устройства для декодирования линейного (10,4) кода, допускающего ортого нализаиию. Пусть для примера проверочные символы bj , Ь Ь заданы линейными комбинациями информационных символов а, а,, а« I а. (здесь сложение Дю модулю два) Ц «2 + ъ Ц- О| Qj Ь Oj а bg- Oj + О, Oj а, bj- 04 + а Для каждого информационного символа можно составить систему разделенных проверок:Oj- a 2 Oj Oj, + bj «i bi а, Оз + Ц a,- «I Oji+b . «Г bg+b Og bj + «з- а 4 - 04 Oj-ai + bg + ba Oj Oj + b Информационные символы можно разбить га числу проверочных соотношений на две гругаш. Символы первой группы а. и Qj могут быть найдены пятью нгаависимымн способамв, т. е. безошибочно декодированы ш|зв ошибках кратности 4 2. Соответствен о символы второй группы а и Ог могу бить правильно определены лишь при любой одвночной ошибке, т. е. менее достоверно но сревнению с символами первой группы. Устройство по принципу действия представлаёт собой синхронный автомат. Шины гавтового Питания и считывания на чертеже ве показаны. устройства удобно рао cii irpiffiaTb во тактам. В исходном положение декодируемое сло uoa OfO Of Oib -b aanacmo в регистр 1 (сямвол Q. слева}, ключе. разомкну ты« замыкаются по жесткой дрограк ме, определяемой свютемой проверочных сооткош 1вй. На первом такте замыкается кпюч 2, в символ о. (возможно, искаже вый), подключается к одному яз входов суь матора 14. На втор (м«| такте ключ 2 размыкается, в замыкаются ключи 3 и 6, которые подключают ко входам сумматора сим волы 92 и Ь| . На третьем такте ключи 3 и 6 размыкаются, и замыкаются ключи 4 и 7, которые подкпючают ко входам сумматора символы а , bj и т. д. &1ачения символа а, снимаемые с сумматора 14 на каждом такте, поступают в счетчик 15. На пятом такте а счетчике оказывается записанным число единичных значейнй символов о t , & в дешифраторе 16 возбуждается выход, соответствующий этому . Выходы дешифратора, со ответствуюище числам 5, 4, 3 на его входе, объединены элементом ИЛИ 17, а соответствующие числам 3 и 2 элементом ИЛИ 18. Одновременно, на пятом же также, подают сигнал разрешения исполнения на шину 19 и снимают результирующее значение символа а, с выходной шины 23, Кроме того, значение этого символа записывают в сдв говый регистр 25. После этого счетчик 15 приводится в нулевое состояние, и начинается аналогичный цикл декодирования cHMBOiла Qj. Значение символа а, в итоге также записывают в сдвиговый регистр. Символ а. при этом сдвигается влево (на чертеже). Символы Qa и Q. декодируются за три такта (по числу, проверочных соотношений). В проверочные соотношения для этих символов входят символы о. и си а Их значения в предложенном устройстве снимают с вь ходов разрядов сдвигового регистра и nt дают через дополнительную группу ключей 12 и 13 коммутатора на сумматор по Модулю два. Сигнал разрешения исполнения в этом случае подают на шину 2 О, а резульгтирующие значения символов д и otj снимают с выходной шины 24. Таким образом, для декодирования символов а и 01 используют значения символов O и о2 не из приемного регистра (как это делается в прототипе), ас выхода устройства, соответствующего символам а,и 0g(возможно скорректированным). Это повышает вероятность правильного декодирования символов а и Ot. (следовательно, и всего слова), -так как на результат декодирования в этом не влияют дополнительные комбинедйи (ошибок во входном слове, HanpHMep,o(ja2.,a,oi,of,b4 . ад1з2 :и.д.-Рпрототйпе подобного рода ошибки П1щводят к .йр сному декодированию одного ййй обоих 0ЙМВОЛОВ а J и d I В рассмотренном примере выход дешифратора, соответствующий числу три на его входе, является общим для обоих элементов ИЛИ. Однако выходной сигнал будет сниматься только с одной выходной шины, в зависимости от того, на KaKjTo из входных шин будет подан сигнал разрешения исполнения. Формула изо.бретения Устройство для декодирования линейных кодов по авт. св. № 514435,, отличающееся тем, что, с целью увеличения вероятности безошибочного декодиро-.

56

ввниЯ( в него введены дополнительные клю- ва| а выходы разрядов этого {югистра через чи и сдвиговый регистр, вход которого noif дополнительные ключи соединены со входом ключей к соответствующему выходу устройст- сумматора по модулю два.

571901

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования циклических линейных кодов | 1984 |

|

SU1179548A2 |

| Устройство для декодирования циклических линейных кодов | 1980 |

|

SU930666A2 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКИХ ЛИНЕЙНЫХ КОДОВ | 1972 |

|

SU433637A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Устройство для декодирования линейных кодов | 1975 |

|

SU514435A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

Авторы

Даты

1977-09-05—Публикация

1976-05-17—Подача