(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Устройство для кодирования | 1985 |

|

SU1275782A1 |

| Устройство для кодирования | 1987 |

|

SU1462494A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

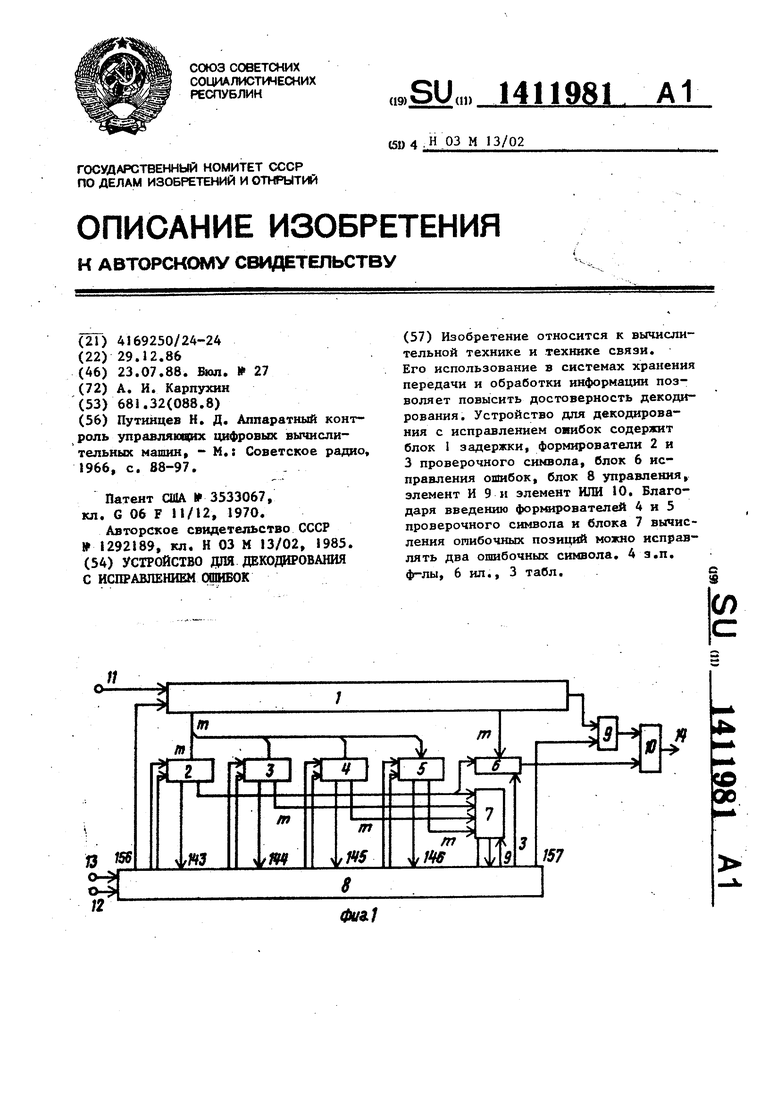

Изобретение относится к вычислительной технике и технике связи. Его использование в системах хранеиия передачи и обработки информации позволяет повысить достоверность декодирования. Устройство для декодирования с исправлением овшбок содержит блок I задержки, формирователи 2 и 3 проверочного символа, блок 6 исправления ошибок, блок 8 управления, элемент И 9 и злемент ИЛИ 10. Благодаря введению фор в1рователей 4 и 5 проверочного символа и блока 7 вычисления ошибочных позиций можно исправлять два ошибочных символа. 4 з.п. ф-лы, 6 ил., 3 табл. с s

ф1/а.1

;о

Изобретение относится к вычисли- Т€шьной технике и технике связи и может быть использовано в системах хранения передачи и обработки информа-

НИИ „

Цель изобретения - повышение достоверности декодирования.

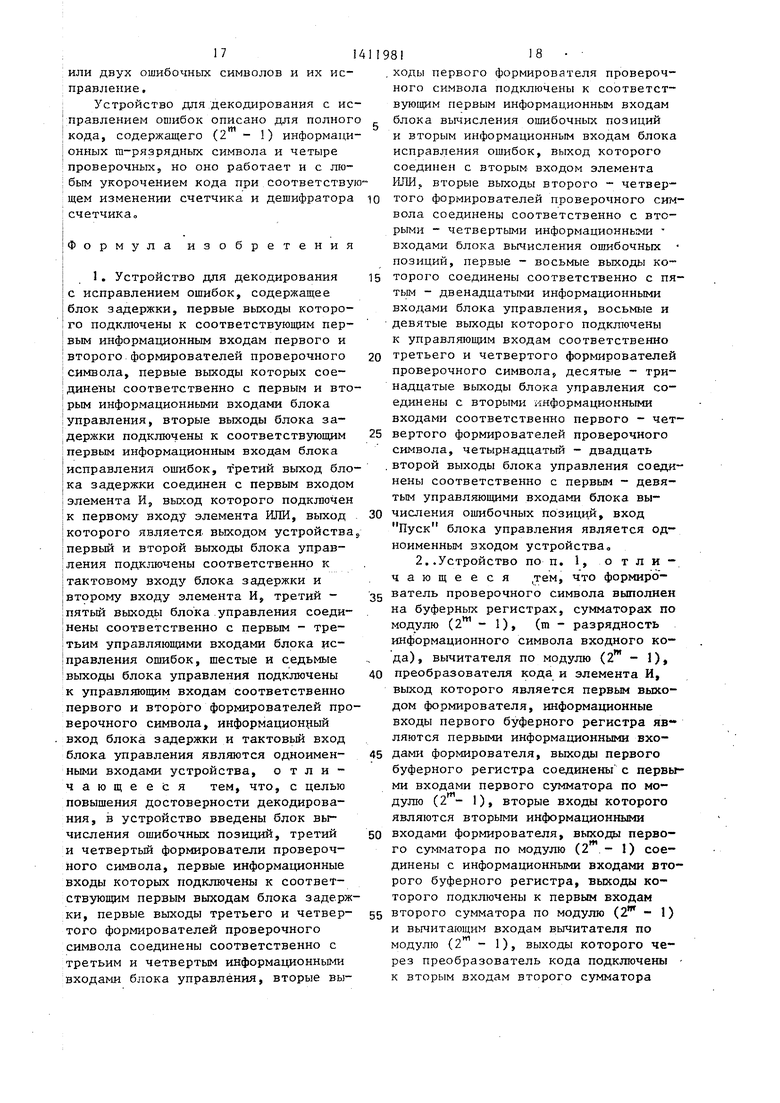

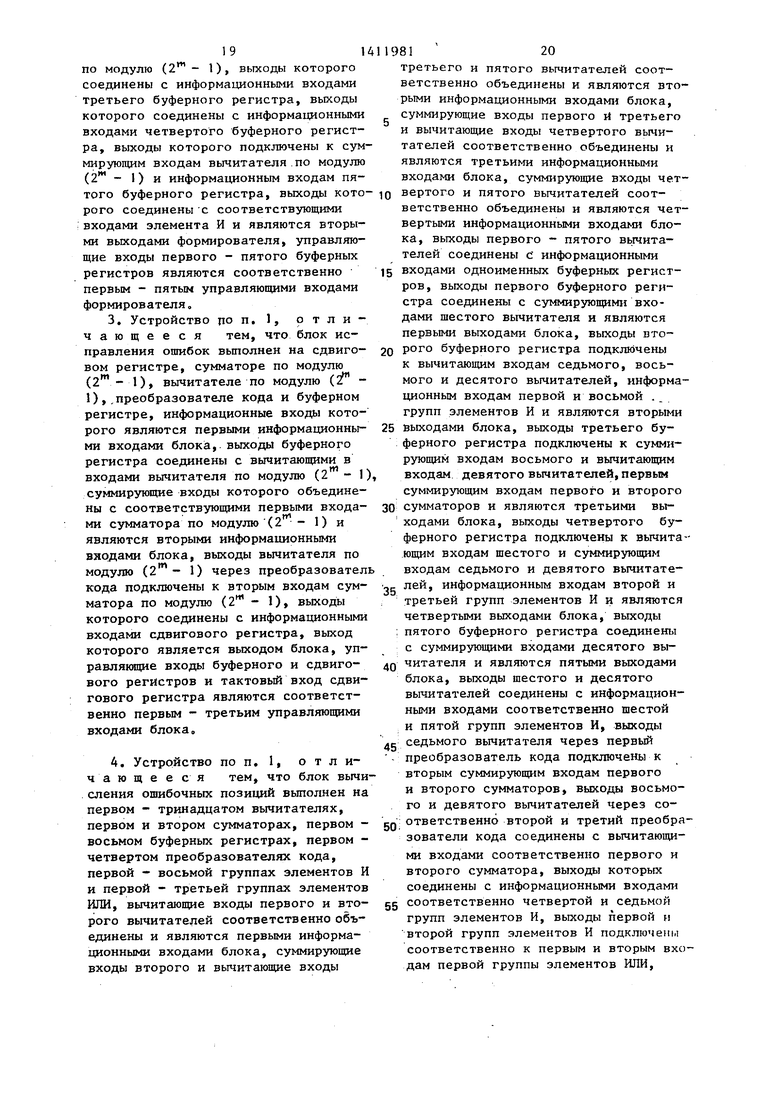

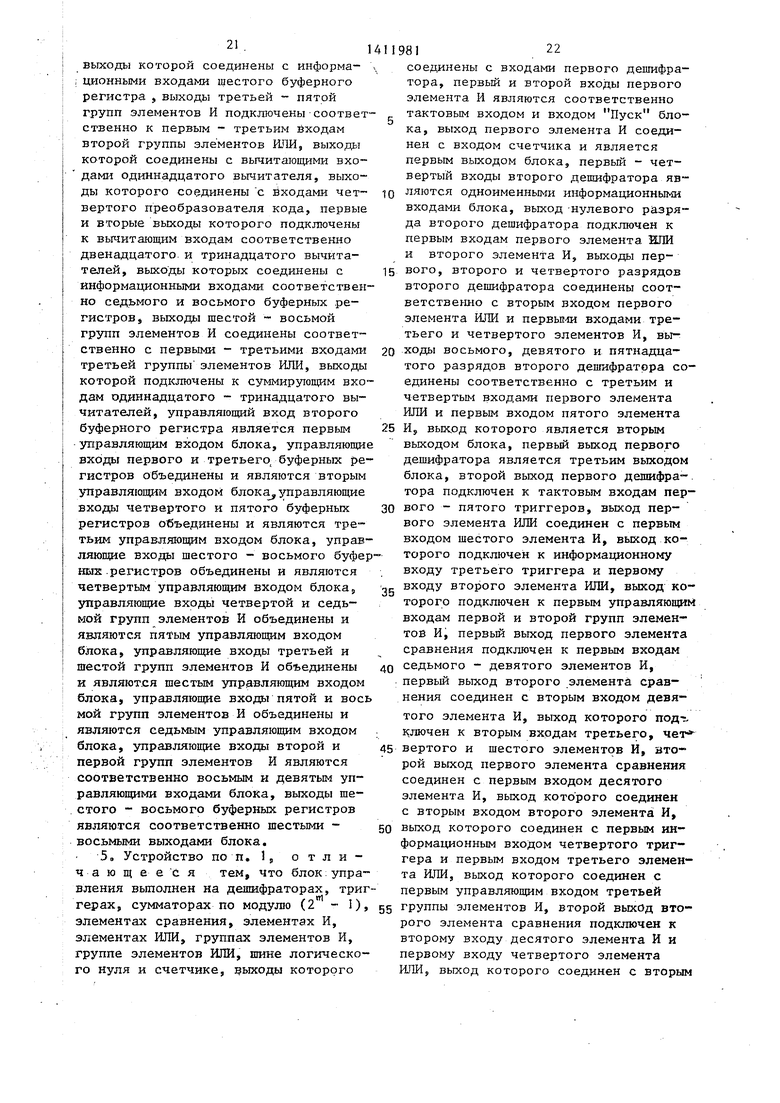

На фиг. 1 приведена блок-схема устройства для декодирования с испра влением ошибок| на фиг.2-5 - функциональные схемы соответственно формирователя проверочного символа, блока исправления ошибок, блока вычисления ошибочных позиций и блока управления на фиг. 6 - временные диаграммы сигналов

Устройство для декодирования с исправлением ошибок (фиг, ) содержит блок 1 задержкиJ первый - четвертый формирователи 2-5 проверочного символа, блок 6 исправления ошибок, блок 7 вычисления ошибочных позиций, блок 8 управления, элемент И 9 и элемент ИЛИ 10, а также информационный 11 и тактовый 12 входы, вход 13 Пуск и выход 14.

Блок 1 задержки представляет собой т (2 + 6)1 -разрядный сдвиговый регистр, где ш - разрядность символа входного кода. Первыми выходами блока 1 являются выхода первого - т-го разрядов регистра, вторыми выходами блока 1 - выходы (2 + 5)-го - т (2 - 5) -го разрядов, третий вы- ход блока 1 - выход последнего разряда регистра.

Каждый из формирователей 2-5 (фиг. 2) выполнен на первом - пятом буферных регистрах 15-19, первом 20 и втором 21 сумматорах по модулю (2 - 1), вычитателе 22 по модулю ( 1), преобразователе 23 кода и элементе И 24. На фиг. 2 обозначены первые 25 и вторые 26 информационные входы, первый - пятый управляющие входы 27-31, первый 32 и вторые 33 вькоды.

Блок 6 исправления ошибок (фиг. 3) вьтолнен на буферном регистре 34, вычитателе 35 по модулю (2 - 1), преобразователе 36 кода, сумматоре 37 по модулю (2 - 1) и сдвиговом регистре 38, На фиг. 3 обозначены первые 39 и вторые 40 информационные входы, первый - третий управляющие входы 41 - 43 и выход 44.

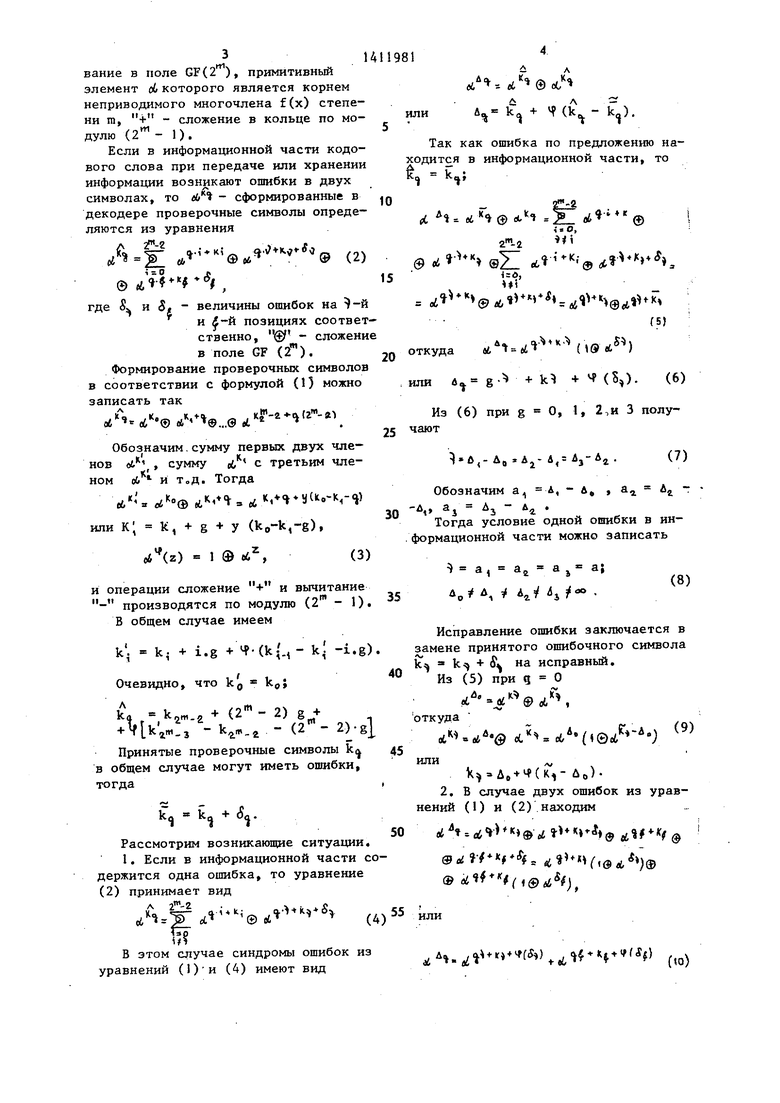

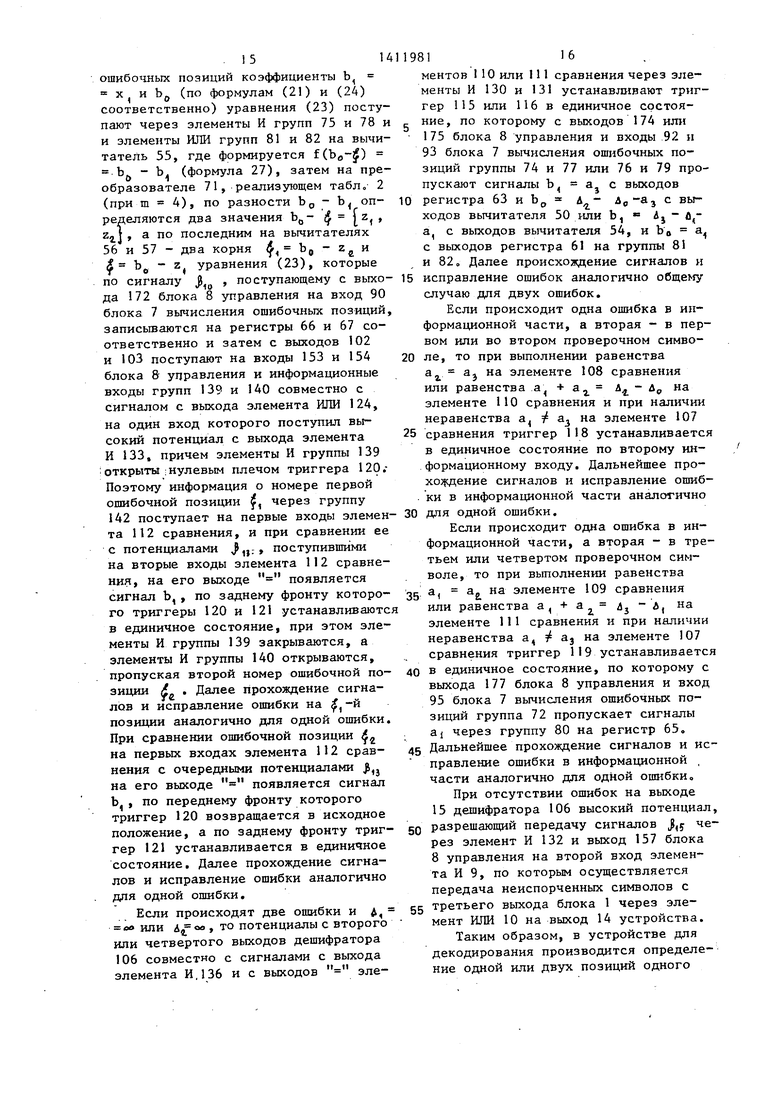

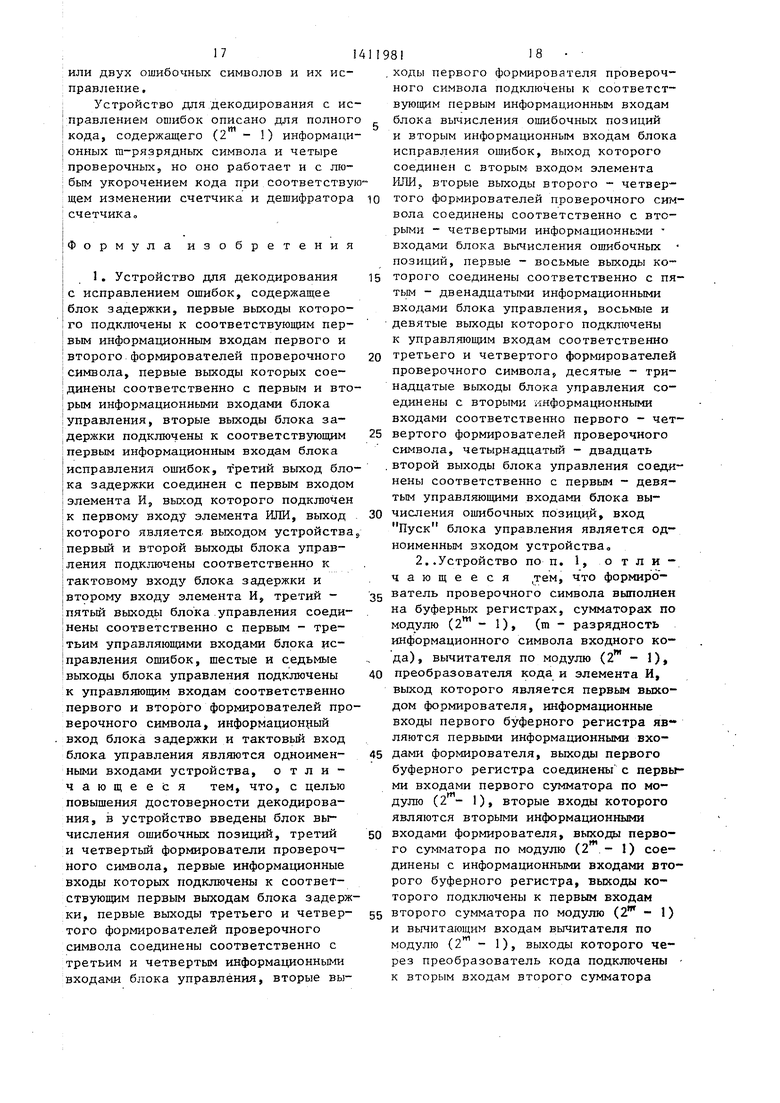

Блок 7 вычисления ошибочных позиций (фиг, 4) выполнен на первом тринадцатом вычитателях 45-57, перво 58 и втором 59 сумматорах, первом - восьмом буфепных регистрах 60-67, первом - четвертом преобразователях 68-71 кода, первый - восьмой группах 72-79 элементов И и первой - третьей группах 80-82 элементов ИЛИ, На фиг. 4 обозначены первые - четвертые информационные входы 83-86, первый девятый управляющие входы , первые - восьмые выходы 96-103.

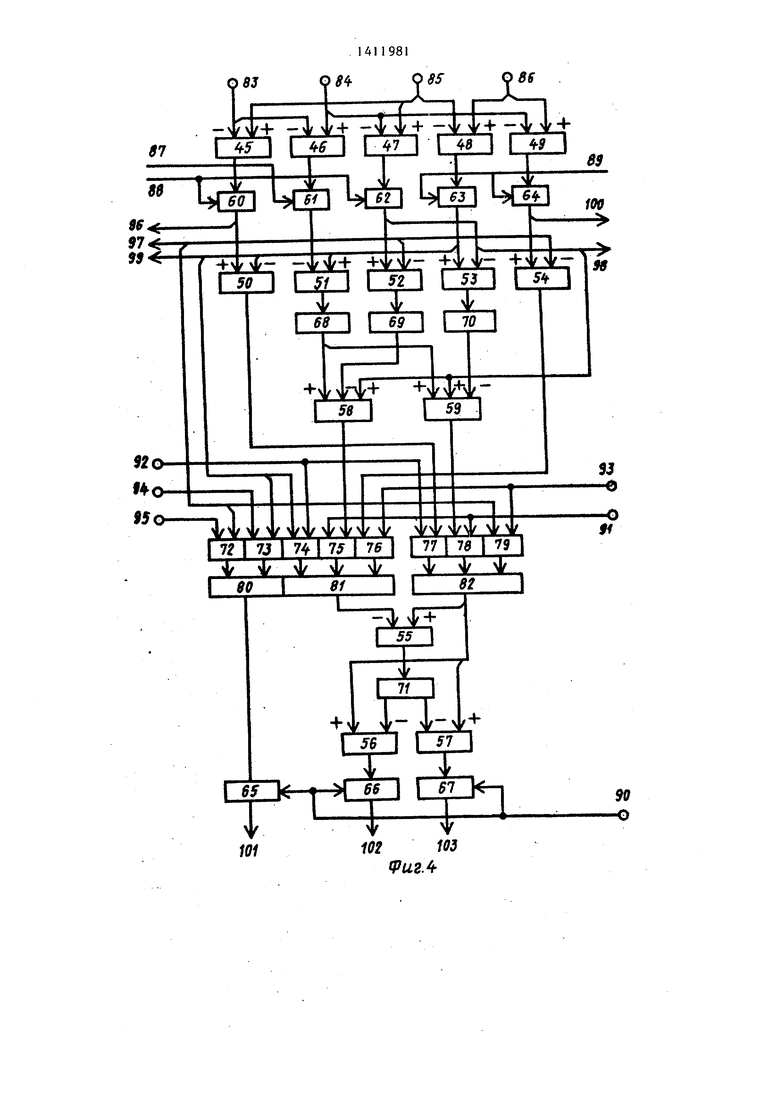

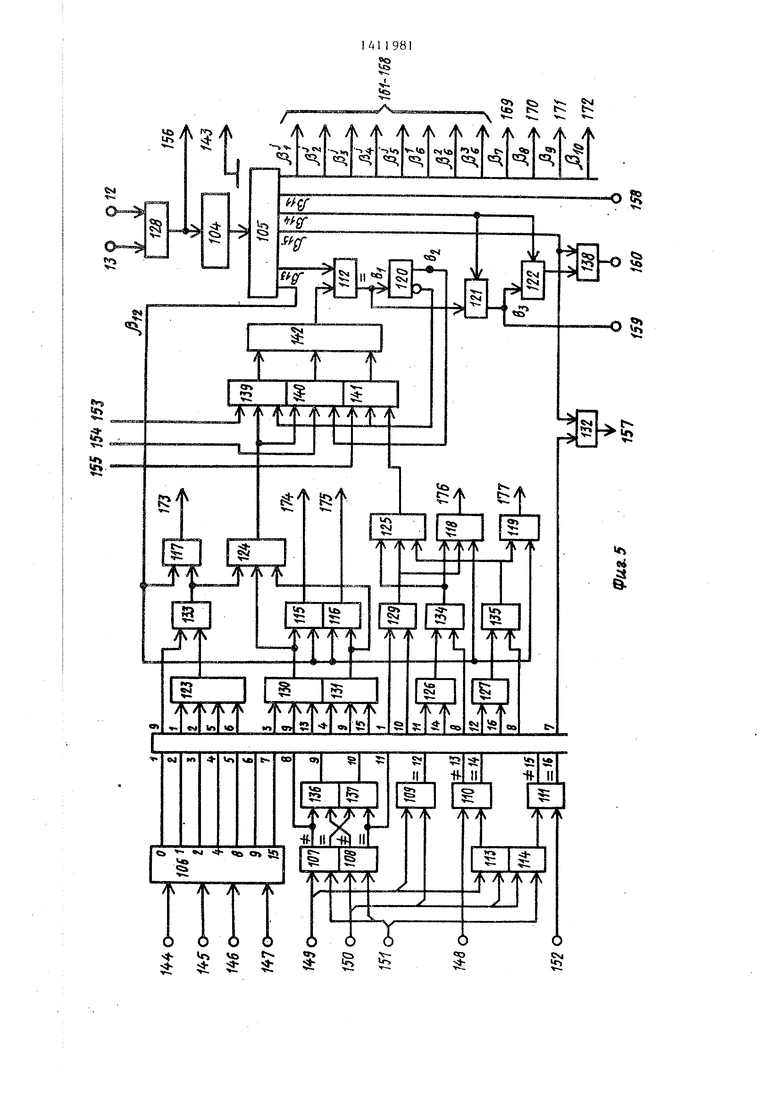

Блок 8 управления (фиг. 5) вьтолнен на счетчике 104, первом 105 и втором 106 дешифраторах, первом - шестом элементах 107-112 сравнения, первом 113 и втором 114 сумматорах п модулю (2 - I), первом - восьмом триггерах 115-122, первом - пятом элементах 123-127 ИЛИ, первом - одиннадцатом элементах 128-138 И, первой третьей группах 139-141 элементов Иу группе 142 элементов ШШ и шине 143 нулевого потенциала. На фиг, 5 обозначены первый - четвертый информационные входы 144-147, пятые - двенадцатые информационные входы 148 - 155, первый - пятый выходы 156-160, шестые - тринадцатые выходы 161-168, четырнадцатый - двадцать второй выходы 169-177. Кройе того, на фиг, 5 обозначены сигналы в различных точках схемы, временные диаграммы которых показаны н фиг.. 6. Сигналы, обозначенные й - , образуют четыре группы, причем при j О - это сигналы на шестых выходах 161, при j 1 - на седьмых выходах 162, при j 2 - на восьмых выходах 163, при j ьгЗ - на девятых выходах 164 блока 8.

Принцип действия устройства для декодирования с исправлением ошибок заключается в следующем.

Кодовые слова, поступающие на вхо 11 устройства, содержат по (2 - 1) т-разрядных информационных символов К. (i О, ,...,2 3 2) и четыре проверочных символа Кв (g О, 1, 2, 3), формируемых в кодирующем устройстве по формуле

об

% 1+ «

(1)

и передаваемых после информационньк символов. Знак обозначает суммиродекодере проверочные символы определяются из уравнения

. 1411981

вание в поле GF(2 ), примитивныйД л

элемент об которого является корнемei s«6 ®oC

неприводимого многочлена f(x) степе- .6 л сг

ни га, + - сложение в кольце по мо- iv KO). дулю ().5

Если в информационной части кодо- как ошибка по предложению на- вого слова при передаче или хранении ходится в информационной части, то информации возникают ошибки в двух 1 символах, то Л - сформированные в .«

I и21 2.

л i eiH® лЧ 51 i

i« О)

,-- ®. (2) @.,,г -.-,ьки.

© ,15 ,.

где Sjj и 5, - величины ошибок на -й л и -й позициях соответ- fSJ

ственно, - сложение

Ъл ж Ч. Ж - ЛКЪ.ДКГ&Ъ V ъ.1,.

В поле GF (2). jO откуда et) Формирование проверочных символов

в соответствии с формулой (1) можно . или А g- + k (S). (6) записать так

ot -сб ® 0 (6) при g О, 1, 2.и 3 полу 25 чают

Обозначим.сумму первых двух членов et , сумму ( с третьим чле- )/,-Дд , Лд-А . (7)

ном d и ТоД. ТОГДЯ

. ® i y -V«i Обозначим а, А, - л. . а, А, - 30 s 4

KnHK; k,+g+y (ko-k,-g),Тогда условие одной ошибки в ин.формационной части можно записать

) 1 ® «6, (3)

а, а а а;

и операции сложение + и вычитание, jjjx ,

- производятся по модулю ( - о. 35 о i- А

В общем случае имеем

Исправление ошибки заключается в

k . k- + i.g + Ck-.- k -i.g). замене принятого ошибочного символа

k « k + (У на исправный. Очевидно, что kj, (5) при q О

k. ,k,.., + ( - 2) g +-откуда - ®

+ ,w., - k.m. - (2 - 2)-g|ki A ;г A Гл-А ч (9)

rot o(, t ( )

Принятые проверочные символы k|j45

в общем случае могут иметь ошибки, ™ . А,

тогда. Ц Д.-(К,-Л,).

2, В случае двух ошибок из уравk k + S .нений (1) и (2) находим

т,50 rf , ,-

Рассмотрим возникающие ситуации. И f@

(2) принимает вид® ,

, (4) или

W.

В этом случае синдромы ошибок из . , Wit + rf) , «i Ht- vUj) , , уравнений (1)-и (4) имеют вид « ( О)

Обозначим k + Ч (5 ) К ; ,

(S)--v ,f.

Тогда (Ю) перепишется

I41198J6

X, а + (aj-a,) - Ч(а,,-а,).

Учитьшая, что «i ° ei и

(,,). cc eci - ; ab --rf ®,i , Л об - @ Г#;(12)

(13) °

15

Умножая (11) на л# и слагая с (12) получаем

rf О (22) Переписьшаем (22) так 15fli ® ) О

к; , .. о (23)

84 + oi г в6 ffli @в6 Д (15)Сравнивая свободные коэффициенты

уравнений (22) и (23), получаем

20

Ь, X,.;

Аналогично из (12),(13) и (13), (14) получаем

, (6).

. V2Vfli @ J. (17)

25

х,-х а, + (а,-а ) -4(aj-a,) (24)

SПреобразуем уравнение (23), исУмножая (15) на о и слагая с пользуя функцию tf(z) (16), получаем

. Ао.. Л, . . ,.. А .,... ..Ц. ,bo.Hf-H

Л Ф Чо6 9об9}®о6.0.(18)30 ...).с.-Ь,-Ьо-с,(-Ь.

Аналогично из (16) и (17) , Ь, -(bj (.;Н0/чЛ- х « о.(19) ,;Л1 1; :ГгдГ

, (2.Ь,-Ъ.-Ч(Ь«))«- (25)

ei Тогда уравнения (18) и (19) принимают вид

Функция Ч (г) 1 + flt обладает следзтощими необходимыми далее свой- 40 ствами: если (z) у, то z V (у); y(z) - P(-z) z. Введем функцию

--9л. . О;

«i - ©fli

© О,

X, V

откуда в6 т; т Функция Ч (г) 1 + flt обладает следзтощими необходимыми далее свой- 40 ствами: если (z) у, то z V (у); y(z) - P(-z) z. Введем функцию

f(z) Z + P(z) (26)

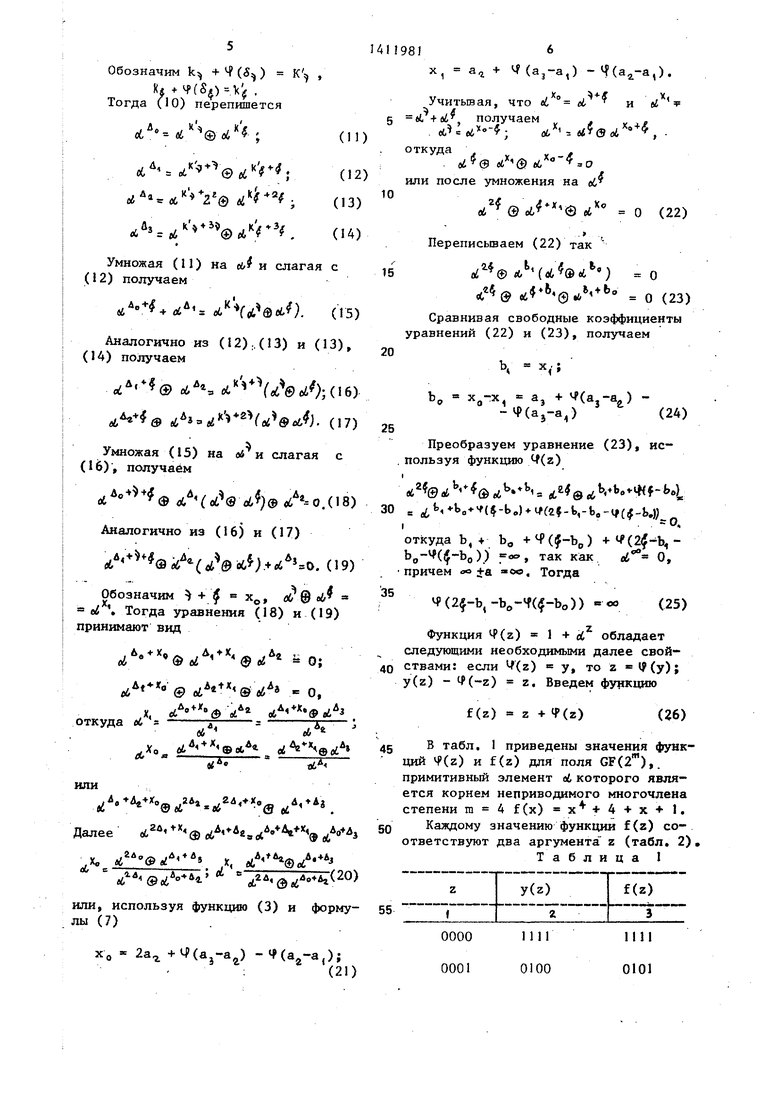

X .j4,, д ,,/ 45 табл. 1 приведены значения функ. J Vу IS У-. r r fn lf

tli

или

ций 4(z) и f(z) для ПОЛЯ GF(2 ),. примитивный элемент at которого является корнем неприводимого многочлена степени m 4 f(x) + х+1.

Лалее .л.«, А+Л 50 Каждому значению функции f(z) со- ответствуют два аргумента z (табл. 2),

.

откуда

«6

или после умножения на ci

°

rf О (22) Переписьшаем (22) так 15fli ® ) О

25

х,-х а, + (а,-а ) -4(aj-a,) (24)

Функция Ч (г) 1 + flt обладает следзтощими необходимыми далее свой- ствами: если (z) у, то z V (у); y(z) - P(-z) z. Введем функцию

f(z) Z + P(z) (26)

7иП981

Продолжение табл.1

з 1 J«.

В обеих таблицах запись 1111 эк- 6, Если одна ошибка в информационвивалентна записи .ной части, а вторая - впервом провеУчитывая, что fC) О, перепись -рочном символе (k), то в соответстваем уравнение (25)вии с условием (8)

I, 4 а Ь а

9

i- „

3

4 о t .9„ Если одна ошибка в информацион„ . л - А л - Л части, а вторая - в четвертом

е1л ОяЛ йл А - а/j

X. 1 1проверочном символе, то а f aj;

-.. ao

aj flj- U4, 1 1 e

откуда a + a A- - До1Исправление ошибки в информацион L 15ной части по nft, 6 - 9-заключается в

и а 7 а , ) 3 Iнахождении номера ошибочной позиции

При этом в п. 4 а + а Л. -До- з пп. 6 и 7 и й для

ной части, а вторая - в третьем про- .символа k по формуле (II). верочном символе, то 0 10. Если при хранении или передаче информации ошибок нет, то все син

а д д .дромы равны со.

Все указанные варианты сведены в

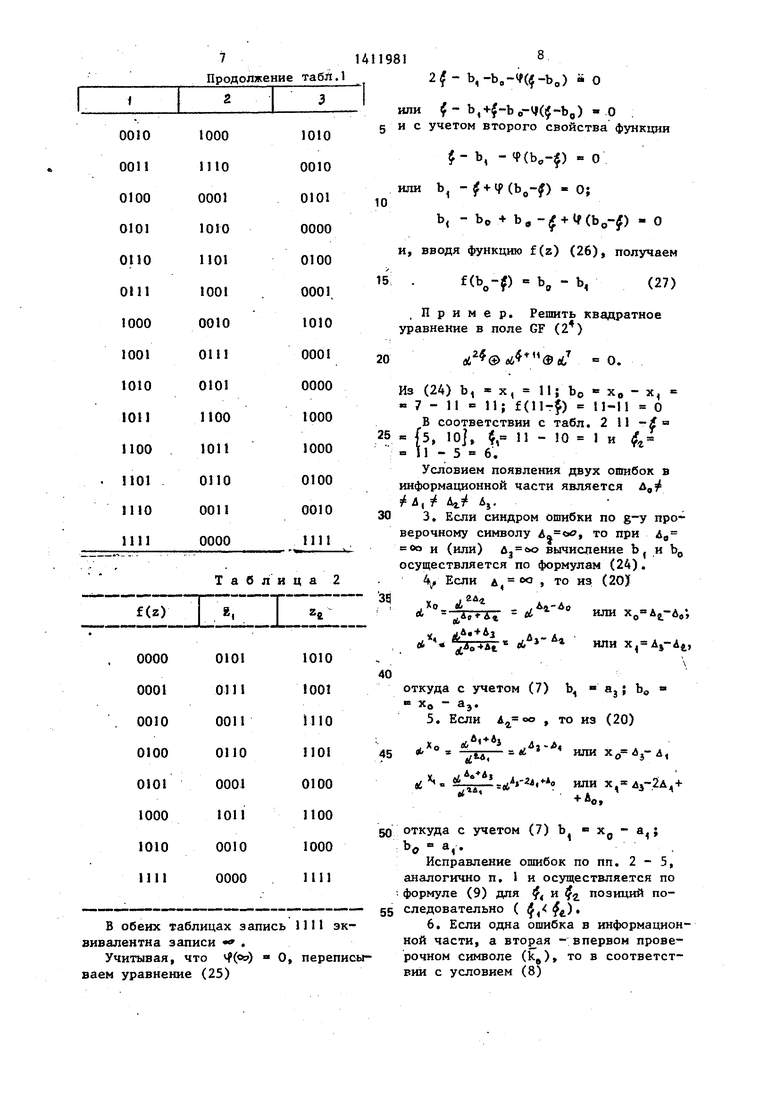

32 , iтабл. 3.

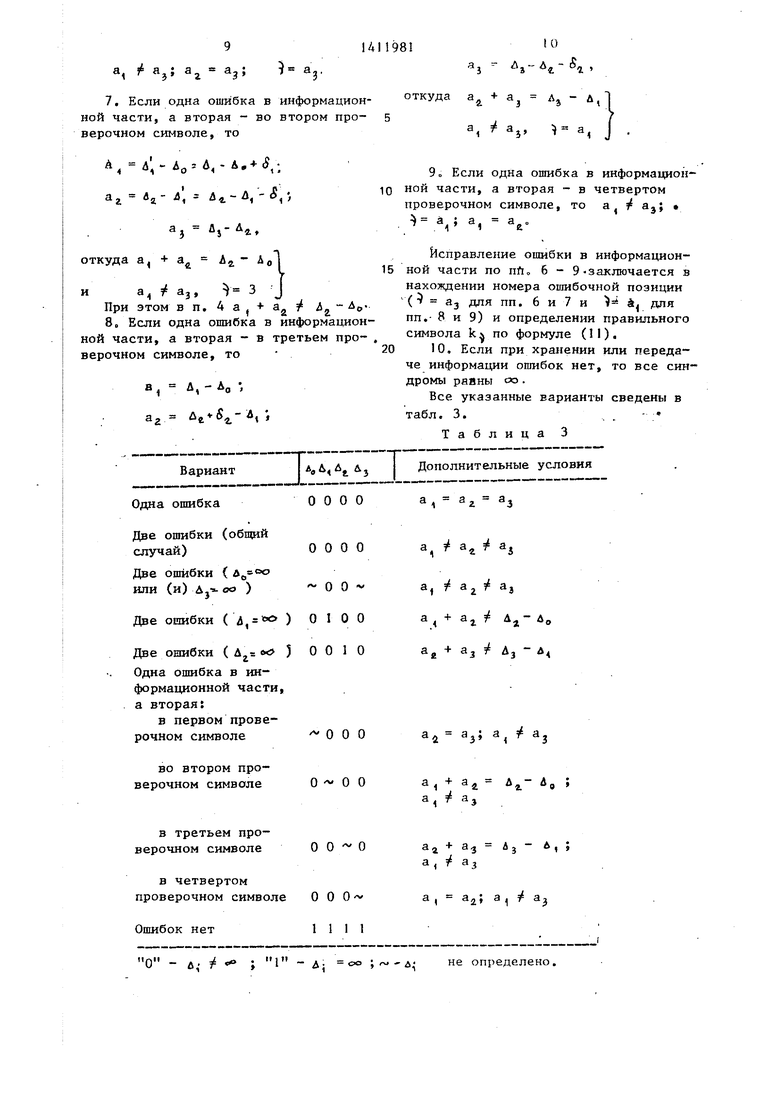

ТаблицаЭ

Вариант ,Дополнительные условия

Одна ошибка 0000 ц г з

Две ошибки (общий

случай) 0000а 7 а э aj

Две ошибки ( uf,°

или (и) uj s-oo ) 00 «а, ,

Две ошибки ( Л, «) 0100а + а / До

Две ОЕшбки ( Д х) 0010 й з Дз 4 Одна ошибка в информационной части, а вторая:

в первом проверочном символе 000а а ;

во втором проверочном символе О -ООа,+ а & ;

а, а,

в третьем проверочном символе

а, / аз

в четвертом

проверочном символе , aj,

Оошбок нет1111

О - л,- f « ; 1 Aj 00 ; г й: не определено.

II1А11981

Устройство работает следующим об- зователи 23, а результат преобразоразом.вания складывается с содержимым реПри поступлении сигнала Пуск на гистров 16 (k) на сумматорах 21 и

элемент И 128 блока 8 управления так- g записывается в буферные рег истры 17

товые импульсы с входа J 2 начинают

по сигналам .

поступать на вход счетчика 104 и на тактовый выход блока 1 (регистра), который начинает пропускать блоки кодовых слов по (2 + 3)-разрядных символов в каждом блоке. Первые m тактов следует нулевой цикл, в течение которого заполняются первые m разрядов регистра блока 1.

В следующем первом (вторые m тактов) по сигналам J (J О, 1, 2, 3), поступающим на входы 27 формирователей 2-5, производится перепись первого (ko) символа с первых m

Циклы с третьего по пятнадцатый аналогичны второму циклу, причем в соответствии с формулой (3) множитель 10 при g (i - позиция символа) в каждом последующем цикле увеличивается на 1 по сравнению с предьщущим,

В 16-м цикле по сигналу произ- , водится перепись с регистра блока 1 15 первого проверочного символа k, на регистр 15 первого формирователя 2, затем сложение его с О на сумматоре 20 и запись результата сложения

(k(j) на регистр 16 по сигналу | .

разрядов регистра блока 1 на реги- 20 Одновременно по сигналу произво- стры 15 формирователей 2 - 5, а за- дится перепись содержимого регистра тем его сложение с нулем входов 26 17 () на регистр 18. Затем на вычитателе 22 осуществляется вычитание содержимого регистра 16 (k) из содержимого регистра 18 (ко). Результат вычитания поступает на преобразователь 23, затем на сз мматоре 21 производится сложение (,) с содерна сумматоре 20 (так как в формуле (2) i О) и запись результата в буферный регистр 16 по сигналам , поступающим на Входы 28 формиров ате- лей 2-5. Затем на вычитателях 22 осуществляется вычитание содержимого регистров 16 (ko) из содержимого ре25

жимым регистра 16 (ko и запись режимым регистра 16 (ko и запись реtrt ч 4 vy ri OajlnWU fc/C

гистров 18 (« - отсутствие информа- 30 ( AO k (1,) на pe „ ±I „ ™I™ o7 °пает на преобразователи 23, работающие по табл. 1 (для m 4), и результат преобразования (О) складыВ 17-м цикле аналогично 6-му н втором формирователе 3 производитс формирование второго синдрома ошиб

В 17-м цикле аналогично 6-му на втором формирователе 3 производится формирование второго синдрома ошибок

л X /« 1, 4J Л i, j ЧДИП.ЧЛ

T. L,. l i o) записью резульна сумматорах 21 и записьшается на. буферные регистры 17 по сигналам , поступающим на входы 29 преобразователей .

тата на регистр 17 по сигналу ,

Одновременно по сигналу % произвоч

дится перепись первого синдрома ошиВо втором цикле (третьи m тактов) 40 бок &д с регистра регистр 18

по сигналам производится перепись второго (k,) символа с регистра блока 1 на регистры 15 формирователей 2-5 и затем его сложение с величиной g i (i- 1 - позиция поступающего символа, формула (2)), поступающей на входы 26 формирователей 3 - 5 с выходов 166 - 168 блока 8 управления на сумматорах 20, и запись результатов на буф ерных регистрах 16 по сигналам . Jl , Одновременно по сигналам , поступающим на входы 30 формирователей 2-5, производится перепись содержимого регистров 17 на регистры 18. Затем на вычитателях 22 осуществляется вычитание содержимого регистров I6 (k ) из содержимого регистров 18. Результат вычитания (kft - k, - g) поступает на преобраи далее по сигналу j - на регистр 19 первого формирователя 2. i В 18-м цикле аналогично 17-му на . третьем формирователе 4 производитс 45 формирование третьего синдрома ошибок 4 с записью результата на ре- ; гистр 17 по сигналу j , во втором формирователе 3 - перепись второго : синдрома д с регистра 17 на регист 50 18 по сигналу 5 , далее - на регис 19 по сигналу , а сформированной на вычитателе 46 блока 7 вычисления ошибочных позиций.разности а, Д, - Дд по сигналу - на ре- 55 гистр 61.

В 19-м цикле (0-й цикл следующег блока) аналогично 17-му циклу на че вертом формирователе 5 производится формирование четвертого синдрома оп

записывается в буферные рег истры 17

по сигналам .

Циклы с третьего по пятнадцатый аналогичны второму циклу, причем в соответствии с формулой (3) множитель при g (i - позиция символа) в каждом последующем цикле увеличивается на 1 по сравнению с предьщущим,

В 16-м цикле по сигналу произ- водится перепись с регистра блока 1 первого проверочного символа k, на регистр 15 первого формирователя 2, затем сложение его с О на сумматоре 20 и запись результата сложения

25

тателе 22 осуществляется вычитание содержимого регистра 16 (k) из содержимого регистра 18 (ко). Результа вычитания поступает на преобразователь 23, затем на сз мматоре 21 производится сложение (,) с содер

жимым регистра 16 (ko и запись ре ч 4 vy ri OajlnWU fc/C

( AO k (1,) на °В 17-м цикле аналогично 6-му на втором формирователе 3 производится формирование второго синдрома ошибок

1, 4J Л i, j ЧДИП.ЧЛ

; i o) записью резуль i o) записью результата на регистр 17 по сигналу ,

Одновременно по сигналу % произвоч

дится перепись первого синдрома ошии далее по сигналу j - на регистр 19 первого формирователя 2. i В 18-м цикле аналогично 17-му на . третьем формирователе 4 производится 45 формирование третьего синдрома ошибок 4 с записью результата на ре- ; гистр 17 по сигналу j , во втором формирователе 3 - перепись второго : синдрома д с регистра 17 на регистр 50 18 по сигналу 5 , далее - на регистр 19 по сигналу , а сформированной на вычитателе 46 блока 7 вычисления ошибочных позиций.разности а, Д, - Дд по сигналу - на ре- 55 гистр 61.

В 19-м цикле (0-й цикл следующего блока) аналогично 17-му циклу на вертом формирователе 5 производится формирование четвертого синдрома опш13

бок Aj с записью результата на регистр 17 по сигналу f , в третьем фop иpoвaтeлe 4 - перепись третьего синдрома л с регистра 17 на регистр 18 по сигналу , далее - на регистр I9 по сигналу | , а сформированных на вычитателях 45 и 47 блока 7 вычисления ошибочных позиций разностей Ар и а Л,., - д на регистры 60 и 62 соответственно по сигналу 20-м цикле (1-й цикл следующего блока) в четвертом формирователе 5 осуществляется перепись четвертого синдрома Д} с регистра 17 на регистр 18 по сигналу далее - на ре- гистр 19 по сигнару || , а сформированных на вычитателях 48 и 49 блока 7 вычисления ошибочных позиций 1 разностей а.з - Л - & и Л} Л( на регистры 63 и 64 соответственно по сигналу э .

Если при передаче или хранении информации возникает одна ошибка, то в соответствии с условием (8) синдромы ошибок йл и выходы элементов И 24 формирователей 2-5 имеют низкий потенциал, который с выходов 32 формирователей, поступая на Iвходы 144 - 147 блока 8 управления, I возбуждает первый выход (О) дешифра- I тора 106, а выходы регистров 61 - I63 имеют поразрядно равные потенциа- 1лы (а , а а,), которые с выходов 97 - 99 блока 7 формирования ошибоч- 1ных позиций поступают на входы 149 - 1151 блока 8 управления и, возбудив {выходы элементов 107 и 108 срав- нения, создают высокий потенциал на выходах элементов И 129 и 137 и элемента ИЛИ 125, возбуждают первый информационный вход триггера 118 по сигналу ,2. с дешифратора 105 устанавливают триггер 118 в единичное положение. Этот сигнал с выхода 176 блока 8 управления через вход 94 блока 7 вычисления ошибочных позиций 7 открьюает группу 73 элементов И, на информационных входах которых присутствуют потенциалы выходов регистра 63 (величина а - ошибочный разряд), которые через группу 80 элементов ИЛИ по сигналу с выхода i72 блока 8 управления записываются на регистр 65. С выходов 101 блока 17 вычисления ошибочных позиций через Ьходы 155 эти потенциалы поступают

1198114

на информационные входы группы 139 элементов И совместно с потенциалами с выхода элемента ИЛИ 125 и инверсно- g го выхода триггера 120, затем на группу 142 элементов ИЛИ и на первые входы элемента 112 сравнения. На управляющий вход 41 блока 6 и.справле- ния ошибок поступают импульсы в

10 с выхода 158 блока 8 управления, по. которым в каждом цикле производится перепись (2 + 6)-го символа из регистра блока 1 на регистр 34 блока 6 , исправления ошибок. При сравнении

15 информации, поступившей на первые

входы элемента 112 сравнения, с сиг- налами ,j на его выходе появляется сигнал Ь,, по заднему фронту которого триггеры 120 и 121 устанав20 ливаются в единичное положение, при этом элементы И группы 141 закрываются, а на выход 159 блока 8 управления, и далее на вход 42 блока 6 исправления ошибок поступает импульс

bj, по которому сформированная на сумматоре 37 сумма k (формула (9)) записывается на сдвиговый регистр 38. По переднему фронту очередного им пульса триггер 121 сбрасьшается,

30 устанавливая триггер 122 в единичное состояние, разрешающее передачу пачки из m символов с выхода 160 блока 8 управления на вход 43 блока 6 исправления ощибок, по которой осущест35 вляется последовательная передача записанного в регистр 38 исправленного символа с выхода 44 блока 6 на второй вход элемента ИЛИ 10 и далее на выход устройства. По переднему

40 фронту очередного импульса J, триггер 122 сбрасывается, запрещая выдачу сигналов на выход 160 блока 8 управления.

45 Если происходят две ошибки и А «« (g О, 1, 2, 3) или Д, 00 и (или) , ТО сигнал с нулевого, первого, восьмого или девятого выходов дешифратора 106 через элемент

50 ИЛИ 123 совместно с сигналом с выхода элемента И 136 при наличии высоких потенциалов на выходах элементов 107 и 108 сравнения поступают на элемент И 133, сигнал с которого ус55 танавливает триггер 117 в единйчнре состояние, по которому сформированные на вычитателях 51-53, преобразователях 68 и 70 и сумматорах 58 и 59 с вычитанием блока 7 вычисления

. 5

ошибочных позиций коэффициенты Ь X и Ь„ (по формулам (21) и (24)

ментов I 10 или 111 сравнения через элементы И 130 и 131 устанавливают триггер 115 или 116 в единичное состояние, по которому с выходов 174 или 175 блока 8 управления и входы 92 и 93 блока 7 вычисления ошибочных позиций группы 74 и 77 или 76 и 79 пропускают сигналы Ъ Hj с выходов

10 регистра 63 и Ь.

о -г.

ходов вычитателя 50 цли Ь,

Ла аJ с - V

соответственно) уравнения (23) поступают через элементы И групп 75 и 78 и g и элементы ИЛИ групп 81 и 82 на вычи- татель 55, где формируется f(bo-J) bjj - b. (формула 27), затем на преобразователе 71, реализующем табл. 2 (при m 4), по разности Ь - Ь определяются два значения z ,

, а по последним на вычитателях а, с выходов вычитателя 54, и be а. 56 и 57 - два корня Ьд - z и с выходов регистра 61 на группы 81 Ьд - Zj уравнения (23), которые и 82 о Далее происховдение сигналов и по сигналу , поступающему с выхо- 15 исправление ошибок аналогично общему да 172 блока 8 управления на вход 90 случаю для двух ошибок.

Если происходит одна ошибка в информационной части, а вторая - в первом или во втором проверочном симво- 20 ле, то при выполнении равенства

блока 7 вычисления ошибочнык позиций, записываются на регистры 66 и 67 соответственно и затем с выходов 102 и 103 поступают на входы 153 и 154 блока В управления и информационные входы групп 139 и 140 совместно с сигналом с выхода элемента ИЛИ 124, на один вход которого поступил высокий потенциал с выхода элемента И 133. причем элементы И группы 139 открыты :нулевым плечом триггера 120,- Поэтому информация о номере первой ошибочной позиции , через группу

а- на элементе 108 сравнения

г

или равенства а +

г

Л Лр

на

элементе 110 сравнения и при наличии неравенства а а на элементе 107 25 сравнения триггер 118 устанавливается в единичное состояние по второму информационному входу. Дальнейшее про- хо сдение сигналов и исправление ошиб- . ки в информационной части аналогично

142 поступает на первые входы элемен- 30 для одной ошибки. та 112 сравнения, и при сравнении ее с потенциалами ,|: поступившими на вторые входы элемента 112 сравнеЕсли происходит одна ошибка в информационной части, а вторая - в третьем или четвертом проверочном символе, то при выполнении равенства

ния, на его выходе появляется сигнал Ь., по заднему фронту которо-

1

го триггеры 120 и 121 устанавливаютс

в единичное состояние, при этом элементы И группы 139 закрываются, а элементы И группы 140 открываются, пропуская второй номер ошибочной позиции . Далее прохождение сигналов и исправление ошибки на ,-и позиции аналогично для одной ошибки При сравнении ошибочной позиции на первых входах элемента 112 сравнения с очередными потенциалами ,j на его выходе появляется сигнал Ъ. , по переднему фронту которого триггер 120 возвращается в исходное положение, а по заднему фронту триггер 121 устанавливается в единичное состояние. Далее прохождение сигналов и исправление ошибки аналогично для одной ошибки.

Если происходят две ошибки и А,

- 00 или Ад ов ,

ТО потенциалы с второго

или четвертого выходов дешифратора 106 совместно с сигналами с выхода элемента И, 136 и с выходов эле141198116

ментов I 10 или 111 сравнения через элементы И 130 и 131 устанавливают триггер 115 или 116 в единичное состояи g - ние, по которому с выходов 174 или 175 блока 8 управления и входы 92 и 93 блока 7 вычисления ошибочных позиций группы 74 и 77 или 76 и 79 пропускают сигналы Ъ Hj с выходов

регистра 63 и Ь.

о -г.

ходов вычитателя 50 цли Ь,

Ла аJ с - V

а, с выходов вычитателя 54, и be а. с выходов регистра 61 на группы 81 и 82 о Далее происховдение сигналов и исправление ошибок аналогично общему случаю для двух ошибок.

а- на элементе 108 сравнения

г

или равенства а +

г

Л Лр

на

элементе 110 сравнения и при наличии неравенства а а на элементе 107 5 сравнения триггер 118 устанавливается в единичное состояние по второму информационному входу. Дальнейшее про- хо сдение сигналов и исправление ошиб- . ки в информационной части аналогично

для одной ошибки.

Если происходит одна ошибка в информационной части, а вторая - в третьем или четвертом проверочном символе, то при выполнении равенства

а, на элементе 109 сравнения

или равенства а, + элементе 111

Z 3

на

неравенства а,

сравнения и при наличии

aj на элементе 107 сравнения триггер 119 устанавливается

0 в единичное состояние, по которому с выхода 177 блока 8 управления и вход 95 блока 7 вычисления ошибочных позиций группа 72 пропускает сигналы ai через группу 80 на регистр 65.

5 Дальнейшее прохождение сигналов и исправление ошибки в информационной , части аналогично для одной ошибки. При отсутствии ошибок на выходе 15 дешифратора 106 высокий потенциал, разрешающий передачу сигналов J, через элемент И 132 и выход 157 блока 8 управления на второй вход элемента И 9, по которым осуществляется передача неиспорченных символов с третьего выхода блока 1 через элемент ИЛИ 10 на выход 14 устройства. Таким образом, в устройстве для декодирования производится определение одной или двух позиций одного

0

5

17

или двух ошибочных символов и их исправление ,

Устройство для декодирования с исправлением ошибок описано для полног кода, содержащего (2 - 1) информационных га-рязрядных символа и четыре проверочных, но оно работает и с любым укорочением кода при соответству щем изменении счетчика и дешифратора счетчика

Формула изобретения

ходы первого формирователя проверочного символа подключены к соответствующим первым информационным входам

блока вычисления ошибочных позиций и вторым информационным входам блока исправления ошибок, выход которого соединен с вторым входом элемента ИЛИ, вторые выходы второго - четвертого формирователей проверочного символа соединены соответственно с вторыми - четвертыми информационными входами блока вычисления ошибочных позиций, первые - восьмые выходы которого соединены соответственно с пятым - двенадцатыми информационными входами блока управления, восьмые и девятые выходы которого подключены к управляющим входам соответственно

третьего и четвертого формирователей проверочного символа, десятые - тринадцатые выходы блока управления соединены с вторыми информационными входами соответственно первого - четвертого формирователей проверочного

символа, четырнадцатый - двадцать второй выходы блока управления соединены соответственно с первым - девятым управляющими входами блока вычисления ошибочных позиций, вход

Пуск блока управления является одноименным входом устройства

ватель проверочного символа выполнен на буферных регистрах, сумматорах по модулю (2 1) (т - разрядность информационного символа входного кода), вычитателя по модулю (2 - О,

преобразователя кода и элемента И, выход которого является первым выходом формирователя, информационные входы первого буферного регистра являются первыми информационными входами формирователя, выходы первого буферного регистра соединены с первыми входами первого сумматора по модулю (2 - 1), вторые входы которого являются вторыми информационными

входами формирователя, выходы первого сумматора по модулю (2 .- 1) соединены с информационными входами второго буферного регистра, выходы которого подключены к первым входам

второго сумматора по модулю (2 - 1) и вычитающим входам вычитателя по модулю (2 - 1), выходы которого через преобразователь кода подключены - к вторым входам второго сумматора

по модулю ( 1), выходы которого соединены с информационными входами третьего буферного регистра, выходы которого соединены с информационными входами четвертого буферного регистра, выходы которого подключены к суммирующим входам вычитателя.по модулю (2 - 1) и информационным входам пятого буферного регистра, выходы кото- IQ вертого и пятого вычитателей соотвычитающими в по модулю (2 - 1

рого соединены с соответствующими входами элемента И и являются вторыми выходами формирователя, управляющие входы первого - пятого буферных регистров являются соответственно первым - пятым управляющими входами формирователя,

3,Устройство по п. 1, отличающееся тем, что блок исправления ошибок вьтолнен на сдвиговом регистре, сумматоре по модулю ( 1), вычитателе по модулю (2: - 1),.преобразователе кода и буферном регистре, информационные входы которого являются первыми информационными входами блока, выходы буферного регистра соединены с

входами вычитателя суммирующие входы которого объединены с соответствующими первыми входами сумматора по модулю (2 - 1) и являются вторыми информационными анодами блока, выходы вычитателя по модулю ( 1) через преобразовател кода подключены к вторым входам сумматора по модулю (2 - 1), выходы которого соединены с информационными входами сдвигового регистра, выход которого является выходом блока, управляющие входы буферного и сдвигового регистров и тактовьй вход сдвигового регистра являются соответственно первым - третьим управляющими входами блока

третьего и пятого вьгчитателей соответственно объединены и являются вторыми информационными входами блока, суммирующие входы первого rt третьего и вычитающие входы четвертого вьгчитателей соответственно объединены и являются третьими информационными входами блока, суммирующие входы четветственно объединены и являются четвертыми информационными входами блока, выходы первого - пятого вьтчита- телей соединены с информационными

входами одноименных буферных регистров, выходы первого буферного регистра соединены с суммирующими входами шестого вычитателя и являются первыми выходами блока, выходы второго буферного регистра подключены к вычитающим входам седьмого, восьмого и десятого вычитателей, информационным входам первой и восьмой . групп элементов И и являются вторыми

выходами блока, выходы третьего буферного регистра подключены к суммирующим входам восьмого и вычитающим входам девятого вычитателей, первым суммирующим входам первого и второго

сумматоров и являются третьими выходами блока, выходы четвертого буферного регистра подключены к вычитающим входам шестого и суммирующим входам седьмого и девятого вычитате-

лей, информационным входам второй и третьей групп элементов И и являются четвертыми выходами блока, выходы пятого буферного регистра соединены с суммирующими входами десятого вычитателя и являются пятыми выходами блока, выходы шестого и десятого вычитателей соединены с информационными входами соответственно шестой и пятой групп элементов И, выходы седьмого вычитателя через первый преобразователь кода подключены к вторым суммирующим входам первого и второго сумматоров, выходы восьмого и девятого вычитателей через соответственно второй и третий преобразователи кода соединены с вычитающими входами соответственно первого и второго сумматора, выходы которых соединены с информационными входами соответственно четвертой и седьмой групп элементов И, выходы первой и второй групп элементов И подключе1И|1 соответственно к первым и вторым входам первой группы элементов ИЛИ,

2 1

выходы которой соединены с информа- ; ционными входами шестого буферного регистра , выходы третьей - пятой групп элементов И подключены-соответственно к первьм - третьим входам второй группы элементов ШШ, выходы которой соединены с вычитающими входами одиннадцатого вычитателя, выходы которого соединены с Входами чет- вертого преобразователя кода, первые и вторые выходы которого подключены к вычитающим входам соответственно двенадцатого, и тринадцатого вычита- телей, выходы которых соединены с информационными входами соответственно седьмого и восьмого буферных регистров, выходы шестой - восьмой групп элементов И соединены соответственно с первыми - третьими входам третьей группы элементов ИЛИ, выходы которой подключены к суммирующим входам одиннадцатого - тринадцатого вы- читателей, управляющий вход второго буферного регистра является первым управляющим входом блока, управляющие входы nejpBoro и третьего буферных регистров объединены и являются вторым управляющим входом блок а., управляющие входы четвертого и пятого буферных регистров объединены и являются третьим управляющим входом блока, управляющие входы щестого - восьмого буферных .регистров объединены и являются четвертым управляющим входом блока, управляющие входы четвертой и седьмой групп элементов И объединены и являются пятым управляющим входом блока, управляющие входы третьей и шестой групп элементов И об-ьединены и ЯВЛЯЮТ.СЯ шестым управляющим входом блока, управляюпще входы пятой и вось мой групп элементов И объединены и являются седьмым управляющим входом блока, управляющие входы второй и первой групп элементов И являются соответственно восьмым и девятьм управляющими входами блока, выходы шестого - восьмого буферных регистров являются соответственно шестьми - восьмыми выходами блока.

5, Устройство поп. Ij отличаю щ е е С я тем, что блок;управления выполнен на дешифраторах, триггерах, сумматорах по модул о (2 ), элементах сравнения, элементах И, элементах ИЛИ, группах элементов И, группе элементов ИЛИ, шине логического нуля и счетчике, выходы которого

98122

соединены с входами первого дешифратора, первый и второй входы первого элемента И являются соответственно тактовым входом и входом Пуск блока, выход первого элемента И соединен с входом счетчика и является первым выходом блока, первый - четвертый входы второго дешифратора являются одноименными информационными входами блока, выход -нулевого разряда второго дешифратора подключен к первым входам первого элемента ШШ н второго элемента И, выходы первого, второго и четвертого разрядов второго дешифратора соединены соот- ветствешю с вторым входом первого элемента ИЛИ и первьп-ш входами третьего и четвертого элементов И, выходы восьмого, девятого и пятнадцатого разрядов второго дешифратора соединены соответственно с третьим и четвертым входами первого элемента ИЛИ и первым входом пятого элемента И, выкод которого является вторым выходом блока, первьй выход первого дешифратора является третьим выходом блока, второй выход первого дешифратора подключен к тактовым входам первого - пятого триггеров, выход первого элемента ИЛИ соединен с первым входом шестого элемента И, выход которого подключен к информационному входу третьего триггера и первому входу второго элемента ШШ, выход которого подключен к первым управляющи входам первой и второй групп элементов И, первьш выход первого элемента сравнения подключен к первым входам седьмого - девятого элементов И, первьй выход второго элемента сравнения соединен с вторым входом девятого элемента И, выход которого подт- ключен к вторым входам третьего, чет вертого и щестого элементов И, второй выход первого элемента сравнения соединен с первым входом десятого элемента И, выход которого соединен с вторым входом второго элемента И, выход которого соединен с первым информационным входом четвертого триггера и первым входом третьего элемента ИЛИ, выход которого соединен с первым управляющим входом третьей группы элементов И, второй выхОд второго элемента сравнения подключен к второму входу десятого элемента И и первому входу четвертого элемента ИЛИ, выход которого соединен с вторым

23,4

входом седьмого элемента И, выход которого подключен к второму информационному входу четвертого триггера и второму входу третьего элемента Ш1И, выход третьего элемента сравнения соединен с первым входом пятого элемента ИЛИ, выход которого подключен к второму входу восьмого элемента И, выход которого соединен с информационным входом пятого триггера и третьим входом третьего элемента ИЛИ, выходы первого сумматора по модулю (2 - 1) соединены с первыми входами четвертого элемента сравнения, первый и второй выходы которого соединены соответственно с вторым входом четвертого элемента ИЛИ и третьим входом третьего элемента И, выход которого подключен к информационному входу первого триггера и второму входу второго элемента ИЛИ, выходы второго сумматора по модулю (Z - 1) соединены с первыми входами пятого элемента сравнения, первый и второй выходы которого соединены соответственно с вторым входом пятого элемента ИЛИ и с третьим входом четвертого элемента Иj выход которого подключен к информационному входу второго триггера и третьему входу первого элемента ИЛИ, выходы первой - третьей групп элементов И соединены соответственно с первыми - третьими входами группы элементов ИЛИ, выходы которой соединены с первыми входами шестого элемента сравнения, выход которого подключен к Входу шестого и информационному входу седьмого триггеров, прямой и инверсный выходы шестого триггера подключены соответственно к второму управляющему входу второй группы элементов И и к вторым управляющим входам первой и третьей групп элементов И, выход седьмого триггера соединен с информационным входом восьмого триггера и является четвертым выходом блока, выход восьмого

8124

триггера соединен с первым входом одиннадцатого элемента И, выход которого является пятым выходом блока, третий выход первого дешифратора соединен с тактовыми входами седьмого и восьмого триггеров, четвертый выход первого дешифратора подключен к вторым входам пятого и одиннадцатого

элементов И, вторые входы четвертого элемента сравнения являются пятыми информационными входами блока, первые входы первого и третьего элементов сравнения и первого сумматора по

модулю (2 - 1) соответственно объединены и являются шестыми информационными входами блока, первые входы второго элемента сравнения и второго сумматора по модулю (2 - ) и вторые

входы третьего элемента сравнения и первого сумматора по модулю (2 - 1) соответственно объединены и являются седьмыми информационными входами блока, вторые входы первого и второго

элементов сравнения и второго сумматора по модулю (2 - 1) соответственно объединены и являются восьмыми информационными входами блока, втбрые входы пятого элемента сравнения являются девятыми информационными входами блока, информационные входы первой -.третьей групп элементов И являются соответственно десятыми -двенадцатыми информационными входами блока, пятые выходы первого дешифратора соединены с вторьми входами шестого элемента сравнения, шестые - девятые выходы первого дешифратора являются одноименными выходами блока, шина нулевого потенциала соединена с десятыми выходами блока, десятые - двенадцатые и тринадцатый - шестнадцатый выходы первого дешифратора являются соответственно одиннадцатыми - семнадцатыми выходами блока, выходы первого - пятого триггеров являются соответственно восемнадцатым - двадцать вторым выходами блока.

26 25

QB3

101

8S

в6

102103

VU2.

| Путинцев Н | |||

| Д | |||

| Аппаратный конт роль управляющих цифровых вычислительных машин, - М.: Советское радио, 1966, с | |||

| Шланговое соединение | 0 |

|

SU88A1 |

| Патент США I 3533067, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-07-23—Публикация

1986-12-29—Подача