112921

Изобретение относится к вычисительной технике и может быть ис- i ользовано в системах передачи и ранения дискретной информации.

Цель изобретения - повьшение на- 5 ежности функционирования.

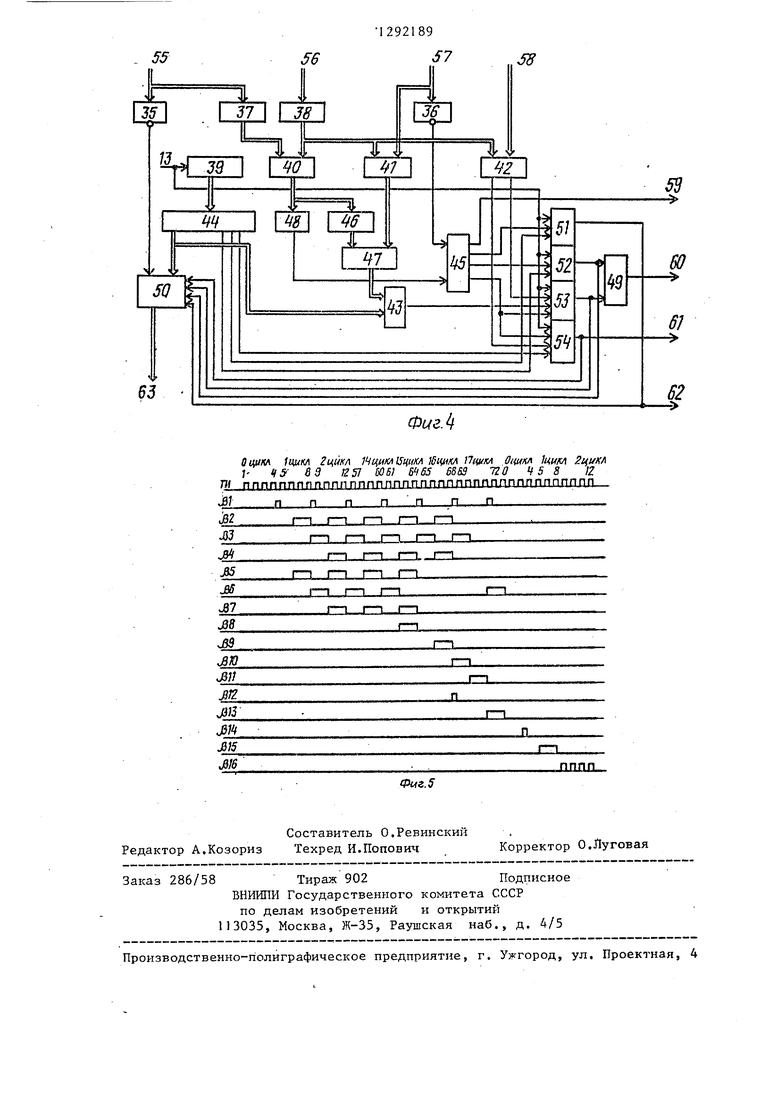

На фиг. приведена блок-схема стройства на фиг. 2-4 - функциональные схемы соответственно формиователя проверочных символов, блока справления ошибки и блока управле- ия; на фиг. 5 - временные диаграм- ы работы устройства.

Устройство для декодирования с

оррекцией ошибок содержит входной регистр 1, первый 2 и второй 3 формирователи проверочного символа, буерные регистры 4-7 .с первого по четвертьй, сумматор 8, блок 9 исправления ошибок., блок 10 ключей и блок 20 11 управления. Устройство имеет так , же информационный 12 и тактовый 13 входы и выход 14.

Входной регистр 1 является регистром сдвига с числом разрядов - ()-т, где m - степень неприводимого многочлена в поле GF (2) . Выходы разрядов с первого по тп-й являются первыми выходами регистра 1, выходы разрядов с (2 +3)-го по ( 30 +3) 1пЗ-го - его вторыми выходами, а выход последнего разряда - третьим выходом регистра 1.

Формирователи 2 и 3 служат для формирования соответственно первого 5 и второго проверочного символов и имеют одинаковое выполнение. Каждый из них (фиг. 2) содержит буферные регистры 15-18 с первого по четвертый, вычитатель 19, сумматор 20 и 40 преобразователь 21 кода. Один из входов вычислителя соединен с шиной 22 источника логической единицы. На фиг. 2 обо-значены также информационные и управляющие входы 23 и 24 45 и выходы 25 формирователя.

Блок 9 исправления ошибок (фиг.З) выполнен на первом 26 и втором 27 буферных регистрах, вычитателе 28, преобразователе 29 кода и сумматоре 50 30. На фиг. 3 обозначены первые 3 и вторые 32 информационные входы, управляющие входы 33 и выход 34.

Блок 10. ключей представляет собой, например, четыре двухвходовых 55 элемента И, выходы которых объединены на элементе или.

Блок 11 управления (фиг. 4) содержит первый 35 и второй 36 элемен9 2

ты И-НЕ, первый 37 и второй 38 буферные регистры, счетчик 39, первый 40 и второй 41 вычитатели, .первый 42 и второй 43 элементы сравнения, первый 44 и второй 45 дешифраторы, преобразователь 46 кода, сумматор 47, первый 48 и второй 49 элементы ИЛИ, генератор 50 управляющих импульсов, элементы И 51-54 с первого по четвертый. На фиг. 4, кроме того, обозначены первый 55, второй 56, . третий 57 и четвертый 58 входы и выходы 59-63 с первого по пятый.

Сумматор 8, а также сумматоры 20, 30 и 47 соответствующих блоков представляют собой сумматоры по модулю .

Вычитатели 19, 28, 40 и 41 являются вычитателями по модулю 2 -1. Вьгаи- татель 19 в каждом формирователе 2 и 3 выполнен на сумматоре с входом принудительного вычитания единицы, который соединен с шиной 22.

Преобразователи 21, 29 и 46 кода |0су111ествляют над входной величиной . преобразования 1©с, е GF(2 ) - примитивньй элемент;© - суммирование в поле GF(2).

Первый и второй выходы первого элемента 42 сравнения в блоке 11 управления (фиг. 4) являются выходами соответственно неравенства и равенства входных величин. Выход второго элемента 43 сравнения является выходом равенства входных величин.

Первые выходы первого дешифратора 44 соответствуют значениям сигналов на-выходах счетчика 39, лежащим в пределах от нуля до включительно. Второй, третий и четвертый вы- ходы первого дешифратора 44 соответствуют значениям на выходах счетчи 1 1n ,

ка 39, равным 2-1,2 и 2 +1.

Выходы второго дешифратора 45 с первого по четвертый соответствуют значениям О, 1, 2 и 3 (в двоичном коде) на его входах.

Генератор 50 представляет собой распределитель импульсов и узел логических элементов, обеспечиваюшз й формирование управляюших имг ульсов в требуемой последовательности.

На фиг. 5 изображены тактовые импульсы (ТИ) по циклам и соответствующие управляющие сигналы Ь для случая, когда .

Принцип действия устройства декодирования с коррекцушй оишбки за- клзочается в следующем.

Информация, подлежащая декоди- рованию, разбита на блоки по 2 го- разрядных информационных символов и два проверочных символа в каждом блоке, являющихся показателями степени примитивного элемента(3(,eGF(2 )- корня неприводимого многочлена f (х) степени та.

Обозначим информационные символы К;, ,...,2 -1, проверочные символы , ,.

Первый проверочный символ

d, --i:ai oi ©o6V..©to 2 -S 0) itO

где © и § - суммирование в поле

GF(2). Вве/,ем функцию ср (Z) такую.

4Toot.u(Z) l®o6 . ТогдаЫ- / (1®Л о ° . . ®а- ci и в общем слу- 4aeoi° (X- - @ci oc - - или, переходя к показателям степеней а; К;+С|)(а-., -К;). Обозначим ..,-К; , тогда а; К;+ср(Ь ) , и

а,,К..,+ср(Ь-.,), откуда Ъ,,..,-К;.+cf(b..,). (2)

Уравнение (2) является итерационной формулой для получения первого проверочного символа.

Начальные условия:

ь,..к„-к,. (3)

Вычисления по формулам (2) и (3),

т.е. операхши сложения и вычитания, осуществляются по модулю (2-1). При нужно иметь в виду, что не определено в кольце по модулю (2 -1).

Поэтому (),

где а - любой элемент кольца.

При эт ом 0 и изымаются из суммы (.1) , для чего в блок 11 управления введена схема И-НЕ 35,

выдающая запрет на выдачу управляющих сигналов в генератор 50 управляющих импульсов.

Второй проверочный символ получают, из соотношения

ot

,

k;4..

11

K,m

ui ,. + i ;+ oi ®o6 ®

bo,;

Аналогично уравнению (2) получим ,..,-H-l-K;-i+Q(bl., )

4,-K;-KCf(b ,.,)

55 ®с. Ъ|:/ ©с.

,if

®oC

(5)

|0ткуда л, со,Ь. J K m; u э К n. (ю

начальные условия

Ь,,К,-К, -.(6)

Проверочные символы по формулам (1) и (4) формируются в кодирующем устройстве. Проверочные символы, формируемые в устройстве декодирования с коррекцией ощибок, обозначим

KjYYi - первый проверочный символ; , второй проверочный символ}

-

i t, от,, V-- К, + 1

причем .yL 2 UO

Проверочные символы, сформированные в кодирующем устройстве и принятые в устройстве декодирования с коррекцией ошибок, обозначим

Kjn, - первый проверочный символ; ,- второй проверочный символ. 1 . Если при передаче информации в устройство декодирования с коррекцией ощибок ошибок не было, то

25

Лч

2 2

GL

к,„;Т - к;.; 2- oi

(7)

i-O

30

При этом синдромы ошибок

2 m

5) fj

, м oi, ©ci 0j

2-2

35 5, /2..,@.п,„ .;

1-0

®Oi,

Обозначим oi°° 0 .

Тогда &, 00 ,.(8)

2. Если ошибка возникла в -м сим воле информационной части (,..., ), то

Л, V С К; 5, oi 6i- 2 ® об - 06 ©Ы. 0

,;

1 ,(S) ,

ui ,. + i ;+ oi ®o6 ®

bo,;

®с. Ъ|:/ ©с.

,if

®oC

|0ткуда л, со,Ь. J K m; u э К n. (ю)

Так как ошибка произошла в.информационной, части, то принятые про верочные символы не имеют ошибок.

Следовательно

5

или I

в этом случае К

, ЛТПr fjm

5, oi ©об .06

К-тм К,™,, Клго

®6i 2 й6 2

К,

®0б

)() &2+4( --

Тогда из выражений (9) и (11) на- ° так как ., , .

-Следовательно

ходим номер ошибочной позиции

U, СО, ,

4-й,

или

.:)й,-л,+с(к -й),

(12)

Исправление оиибки производится следующим образом.

По номеру ошибочной позиции из ,„ ,.. ч „

,20 символе (К,,п,,.). В этом случае синдвходного сдвигового регистра 1 (по-2 i

Исправление ошибки заключается в замене испорченного символа К „ на вновь сформированный (правильш-ш) проверочный символ К-т.

5. Ошибка во втором проверочном

г,ТП

зиция 2 +3) на регистр 26 блока 9 исправления ошибки записывается испорченный символ K:).5.

Из формулы (9)Ы oJ. «®oi.

ром по первому проверочному символ S, 0, а по второму

25 5, ot

©06

М

рК.К. (16

откуда к-о

.

(13)

или

К;, Л,+0 (К;,-й,).

Данный алгоритм и реализует блок 9.

3. Если ошибка происходит на (2 -1)-й позиции (2 -1), то

. ,(52--,) или

(

с ,i ,г % + i Х з Sj oi @uL -Slo ®oi ©

Р ..; ,.

0

50

Устройство работает следующим

,, причем так как образом.

ошибка - в информационной части. Следовательно

Д, 00, Д, i . (14)

Исправление ошибк й аналогично п. 2. 4. Ошибка в первом проверочном

СИМВОЛЕ (Kjw).

На вход 12 устройства поступаю блоки кодовых слов по 72 разряда каждом (64 разряда информационных 8 проверочных) в сопровождении та товых импульсов (ТИ).

Первые 4 такта следует нулевой цикл, в течение которого заполняю

в этом случае

, ЛТПr fjmI

5, oi ©об .06 );

К-тм К,™,, КлгоМ о п

®6i 2 й6 2 ©б6 ©

К,

®0б

,.. ч „

U, СО, , , (15)

так как ,.

Исправление ошибки заключается в замене испорченного символа К „ на вновь сформированный (правильш-ш) проверочный символ К-т.

5. Ошибка во втором проверочном

2 i

ром по первому проверочному символу S, 0, а по второму

25 5, ot

©06

М

рК.К. (16)

Следовательно А, 00, К m

Исправление ошибки 30 К

-

-.т/- t тл

) 2

так как .

Все варианты возможных одиночных ошибок сведены в таблицу.

Нет

Нет Нет

5-й ( 0,. .,,

) Да Да

Нет

образом.

На вход 12 устройства поступают блоки кодовых слов по 72 разряда в каждом (64 разряда информационных, 8 проверочных) в сопровождении тактовых импульсов (ТИ).

Первые 4 такта следует нулевой цикл, в течение которого заполняют

7 . 1

ся первые 4 разряда входного регистра . Затем следует 1-й цикл (5-8 такты), в котором, если информационный символ не равен 2 -1 (15), производится запись на регистры 15 формирователей 2 и 3 первого символа информации по сигналу i, и его церепись на регистры 16 - по сигналам р и р„ соответственно. Если информационный символ равен 15 (1111), то регистры 15 обнуляются и элемент И-НЕ 35 блока 11 управления выдает запрет (О) на генератор 50 упраБЛяюп5их сигналов, запрещающий выдачу управляющих сигна- лов на регистры 16-18 формирователя 2.

В этом случае формирователь 3 работает в режиме вычитания 1 (формула (5)) с шины 22 вычитате- ля 19.

Б следующем, втором,, цикле (9- 12-й такты) производится запись на регистры 15 второго информационного символа по сигналу /3), вычитание из содержимого К регистров 16, содержимого К, регистров 15 на вычита телях 19, сложение полученных результатов с нулем регистров 17 на сумматорах 20 и запись результатов на регистры 18 по сигналам рз и 1Ь 6. : Далее по ,. сигналам р2 и /35 производится передача второго информационного символа К на регистры ,16 и одновременно по сигналам ,/34 и (Ь7 - передача содержимого региртров 18 с преобразованием его по форму- лeci преобразователях 21 на регистры 17.

Третий цикл аналогичен второму, за исключением того, что при сложении на сумматорах 20 оба операнда в общем случае отличны от нуля.

Остальные циклы (4-15-й) аналогичны третьему. При этом в 15-м цИк ле на регистр 18 формирователя 3 по сигналу р6 записывается сформиро ванньй второй проверочный символ

-

К,, которьш по сигналу 8 переписывается на регистр 5.

В 16-м цикле по сигналу Ю на регистр 18 формирователя 2 записывается сформированный первый провероч нь1й символ К,и , который по сигналу 59 переписывается на регистр 4 и складывается с содержимым регистра 5. на сумматоре .8. Результат сложения записывается на регистр 7 по сигналу р10.

0

5

O 5

0

0

5

898

В 17-м цикле на регистр 15 формирователя 2 ПО сигналу |31 поступает первый проверочный символ К, , который суммируется с содержимым (Kig) регистра 17 на сумматоре 20. Результат суммы по сигналу 3 3 записывается на регистр 18 и затем по сигналу (Ы 1 - на регистр 6.

В 18-м цикле (нулевой цикл следующего блока информации) на регистр 15 формирователя 3 по сигналу /31 записьшается второй проверочный символ К|, который суммируется с содержимым (К|-) регистра 17 на сумматоре 20. Результат суммы й. по сигигшу 6 записывается на регистр 18.

В 16-м и 17-м циклах сигнал (Я блокируется блоком 11 управления на .форг шрователь 3, а в 18-м цикле - на формирователь 2,i

В 17-м цикле по сигналу И 12 первый проверочный символ К, с регистра 1 переписывается на регистр 37 блока 11, а в 18-м K,g цикле содержимое (2 регистра 18 формирователя 3 переписывается на регистр 38 блока 1 1 по сигналу /513.

Если ошибка произошла в -5 -м символе информационной части (,..., 14), то в соответствии с формулой (12) на вычитателе 40 осуществляется получение разности , а па вычитателе 41 - разности ,. С вы- читателя 40 разность поступает на преобразователь 46,рсущест- вляющий преобразование су (К)- й) , результат которого суммируется с результатом вычитателя 41 на суммато- . ре 47. Если содержимое (и,) регистра 6 не равно 00 (1111), то выход та И-НЕ 36 равен 1, а если , т.е. выход вычитателя 40 не равен

О, то выход элемента ИЛИ 48 равен 1, и на дешифраторе 45 возбуждается четвертый выход.

Далее, если элемент 42 сравнения выдает сигнал на первом выходе (,g), то ошибка произошла позиции (-) 0,. .., 14) :-и элемент И 53 открывается по сигналам с дешифратора 45- и элемента 42 сравнения. При совпадении номера позиции (выходы сумматора 47) и номера цикла с дешифратора 44 элемент 43 сравнения выдает сигнал на элемент И 53, открывая его и разрешая выдачу управляющих сигналов с генератора 50 управляющих импульсов на блок 9 исправления ошибки, а через элемент ИЛИ 49

91

выдает сигнал на второй выход 6.0 блока 115 открывая второй ключ блока 10.

По сигналу р 14 на регистр 26 блока 9 переписываются сигналы с ()х разрядов регистра 1 (т.е. К), имеюаше ошибки, и в соответствии с формулой (3) на вы тателе 28 из ошибочного символа К вычитается содержимое (д,) регистра 6. Полученный результат преобразуется в преобразователе 29 (q(,), складывается с й на сумматоре 30 и по сигналу и 15 записывается на регистр 27.

В следующем цикле с помощью серии импульсов |3 1 6 через второй ключ блока 10 передается исправленный символ на выход 14 устройства,

На временной диаграмме (фиг. 5) показаны сигналы 514 и Й15

Аналогично происходит исправление ошибки на 15-й позиции . При 3TOMU2 K|g, сигналы на выходах вычи- тателя 40 и элемента ИЛИ 48 равны О, дешифратор 45 выдает сигнал на третьем выходе И, при наличии сигнала на втором выходе дешифратора 44 элемент 52 И разрешает вьщачу управляющих сигналов с генератора 50 на блок 9 исправления ошибки и в следую щем цикле по второму выходу 60 блока 11 выдает сигнал на второй ключ блока 10.

Если ошибка произошла на 16-й позиции (в принятом первом проверочном символе К ), то дешифратор 45 выдает сигнал на четвертом выходе, так как Д, схэ и ,, но злемент 42 сравнения выдает сигнал по второ,.

му выходу и при наличии сигнала на третьем выходе дешифратора 44 элемент И 54 разрешает выдачу сиг нала управления с генератора 50 управляющих импульсов на регистр 4 для последовательной передачи его содержимого в следующем цикле через третий ключ блока 10 на выход 14 устройства.

Если ошибка произошла на 17-й позиции (в принятом втором проверочном символе K,.j) , то дешифратор 45 выдает сигнал на втором выходе, так как Л ,. схэ и , и при наличии сигнала на четвертом вьпсоде дешифратора 44, элемент И 5) разрешает выдачу сигнала управления с генератора 50 на регистр 7 для последовательной передачи его содерf5

20

25

218910

жимого следующем цикле через четвертый ключ блока 10 на выход 14 устройства.

Если ошибки не было, то дешифра- 5 тор 45 выдает сигнал на первом выходе и разрешает выдачу управляющих импульсов на первь1й ключ блока 10 для последовательной передачи информации с регистра 1 на выход 14

10 . устройства.

1

Устройство декодирования с коррекцией ошибок позволяет декодировать кодовые слова, имеющие информационную часть, равную 2 т-разряд- ных символов при двух- т-разрядных проверочных символах, имеющих один неисправньш и-разрядный символ, что позволяет без добавочной избыточности использовать это устройство в вычислительных машинах, имеющих, как правило, длину,слов, равную степени 2 (8, 16, 24, 32, 64 и,т.д.). При этом применение степенных кодов позволяет избавиться от операций умножения и деления в поле GF(2), заменяя их операциями сложения и вычитания по модулю и преобразования кода, что позволяет упростить устройство, повьшзая тем самым надежность его в работе и обеспечивая более удобную его микроминиатюризацию.

Формула изобретения

35

1 . Устройство для декодирования с коррекцией О1пибок, содержащее входной регистр, информационный вход которого является информационным входом устройства, первые выходы подклю- чены к соответствующим информационным входам первого формирователя проверочного символа, первый и второй буферные регистры, первые выходы

45 первого буферного регистра подключены к соответствующем первым входам сумматорм, и блок ключей, отличающееся тем, что,с целью по- вьшзения надежности функционирования,

50 в него введены второй формирователь проверочного скивопа, . третий и четвертый буферные регистры, блок исправления ошибок и блок управления, первые информационные входы второго

55 формирователя проверочного символа и первые входы блока управления под- ключены к соответствующим и первым выходам входного регистра, выходы первого формирователя проверочного

30

40

,

символа соединены с соответствую- -v щими информационными входами первого и.третьего буферных регистров, выходы второго формирователя проверочного символа соединены с соответ- ствующими информационными входами второго буферного регистра и вторыми входами блока управления, выходы т ретьего буферного регистра подключены к соответствующим первым инфор- мационным входам блока исправления ошибок и третьим входам блока управления, четвертые входы которого подключены к соответствующим первым выходам первого буферного регистра, пятый вход блока управления является тактовым входом устройства, выходы второго буферного регистра соединены с соответствующими вторыми входами сумматора, выходы которого под- ключены к соответствующим информационным входам четвертого буферного регистра, вторые выходы входного регистра соединены с соответствующи ш вторыми ипфopмaциoнны ш входами бло ка исправления ошибок, третий выход входного регистра, выход блока исправления ошибок второй выход первого и выход четвертого буферных регистров подключены к соответству- ющим первым входам блока ключей, первый - четвертый выходы блока управления соединены с соответствующими вторыми входами блока ключей, выход которого является выходом уст- ройства, пятые выходы блока управления подключены к соответствующим управляющим входам входного и буферных регистров, формирователей проверочного символа и блока исправления оши- , бок,

2, Устройство по п, 1, отличающееся тем, что формирователь проверочного символа выполнен на буферных регистрах, вычитателе, сумматоре и преобразователе кода, информационные входы первого буферного регистра являются информационными входами формирователя, выходы первого буферного регистра подключены к соответствующим первым входам вы- читателя и информационным входам второго буферного регистра, выходы которого соединены с соответствуюа им вторыми входами вычитателя, третий вход которого подключен к шине источника логической единицы, выходы вычитателя соединены с соответствующими пepвы lи входами сумматора,

- 5 JO 5203035 40

4550и 55

ходы преобразователя кода подключены к информационным входам третьего буферного регистра, выходы которого соединены с соответствующими вторыми входами сумматора, выходы которого подключены к соответствующим информационным входам четвертого буферного регистра, выходы которого соединены с соответствующими входами преобразователя кода и являются выходами формирователя, управляющие входы буферных регистров являются соответствующими управляющими входами формирователя,

3.Устройство по п, 1, о т л и- чающееся тем, что блок исправления ошибок выполнен на буферных регистрах, вычитателе, преобразователе кода и сумматоре, первые входы.которого объединены с соответствующими первыми-входами вычитателя и 51ВЛЯЮТСЯ cooтвeтcтвyющи п первыми информационными входам блока, информационные входы первого буферного регистра являются вторым информационными входами блока, выходы первого буферного регистра подключены

к соответствуюпщм вторым входам вычитателя, выходы которого через преобразователь кода подключены к соответствующим вторым входам сумматора, выходы которого соединены с соответствующими информационными входами второго буферного регистра, выход которого является выходом блока, управляющие входы буферных регистров являются соответствующими входами блока.

4.Устройство по п. 1, о т л н- чающееся тем, что блок управления выполнен на буферных регистрах, вычитателях, сумматоре, счетчике, генераторе управляющих импульсов, преобразователе кода, дешифраторах, элементах сравнения, элементах ИЛИ, элементах И и элементах И- НЕ, входы первого элемента И-НЕ объединены с соответствующим входами первого буферного регистра и являются первыми входами блока, выходы первого буферного регистра подключены к соответствующим первым входам первого вычитателя, выходы которого соединены со вxoдa ni первого элемента ШШ и через преобразователь кода - с соответств аощими первыми входам- сумматора ,входы второго буферного регистра являются соответству- ющим вторыми входами блока, выходы

1312

второго буферного регистра подключены к соответствующим вторым входам первого выЧитателя, первым входам первого элемента сравнения и первым входам второго вычитателя, вторые входы которого объединены с соответствующими входами второго элемента И-НЕ и являются третьими входами, блока, вторые входы первого элемента сравнения являются соответствующими четвертыми входами блока, вход счет- чика объединен с первыми входами.эле jMeHTOB И и является пятым входом блока, выходы счетчика подключены к соответствующим входам первого дешифратора, первые выходы которого соединены с соответствующими первыми входами генератора управляющих импульсов и второго элемента сравнения выходы второго вычитателя подключены к соответствующим вторым входам сумматора, выходы которого соединены с соответствующими вторыми входами второго элемента сравнения, выход перво го элемента ИЛИ соединен с первым входом второго дешифратора, выходы, первого и второго элементов И-НЕ подключены к вторым входам соответственно генератора управляющих импульсов и второго дешифратора, первый выход

/о

21

5 0 30

J5

5

8914

которого является первым выходом блока, второй и третий выходы второго дешифратора подключены к вторым входам соответственно первого и второго элементов И, четвертьш выход второго дешифратора соединен с вторыми входами третьего и четвертого элементов И, выходы второго и третьего элементов И подключены к входам второго элемента ИЛИ, выход которого является вторым выходом блока, второй, третий и четвертый выходы первого део1ифратора подключены к третьим входам соответственно второго, четвертого и первого элементов И, выход второго элемента сравнения соединен с третьим входом третьего элемента И, первый и второй выходы первого элемента сравнения соединены с четвертыми входами соответственно третьего и четвертого элементов И, выходы четвертого и первого элементов И являются соответственно третьим и четвертым выходами блока, выходы элемента И с первого по четвертый подключены к соответствующим третьим входам генератора управляющих импульсов , выходы которого

являются пяты- и выходами бло- 1 ка.

55

56

щ

-IL

oS2

ЁБ

Ош/хл 2и,икл Пиимицнхл 16цихл Оцикл /«йвд 1- 45 63 K5J HOSl 68В9 720 f 5 8 рдппррппппгцглппппппаппппппппппрпппппп

-П , п

JL

D

Л.

Л.

л.

Составитель О.Ревинский Редактор А.Козориз Техред И.Попович Корректор О.Луговая

.м м V. . « -«-w-- v -B - .-- -

Заказ 286/58 Тираж 902Подписное

ВНИИПР1 Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская иаб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

67

S8

ФцгЛ

Л.

л.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Устройство для кодирования | 1985 |

|

SU1275782A1 |

| Устройство для кодирования | 1987 |

|

SU1462494A1 |

| Устройство для кодирования | 1987 |

|

SU1496010A2 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Устройство для контроля информации на четность | 1985 |

|

SU1339898A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

Изобретение относится к вычислительной технике. Его использование в системах передачи и хранения дискретной информации позволяет повысить надежность их функционирова- ния. Устройство содержит входной регистр 1, формирователи 2 и 3 проверочного символа, буферные регист- . ры 4 и 5, сумматор 8 и блок 10 ключей. Введение буферных регистров 6 и 7, блока 9 исправления ошибок и блока 11 управления обеспечивает работу устройства в случае, когда декодируемые слова имеют информационную часть, равную 2 го-разрядных символов и два т-разрядных проверочных символа, и один из 2 +2 символов искажен. При этом исправление ошибок не требует применения операций умножения и деления в поле GF

| Патент США № 3629824, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство декодирования сКОРРЕКциЕй ОшибОК | 1978 |

|

SU794728A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-23—Публикация

1985-09-19—Подача