(54) ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНЫЙ КЛЮЧ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналоговой памяти | 1986 |

|

SU1377916A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1327293A1 |

| Электрический аналоговый накопитель | 1975 |

|

SU525164A1 |

| Аналоговый ключ | 1984 |

|

SU1241455A1 |

| Двухтактный инвертор | 1982 |

|

SU1099364A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Импульсный источник питания с бестрансформаторным входом | 1986 |

|

SU1543392A1 |

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| Ключ | 1979 |

|

SU864567A1 |

| ИНВЕРТОР | 1994 |

|

RU2066513C1 |

1

Изобретет е отнгх:ится к аналого-цифровой вычислитзльной технике и может использоваться в автоматике и измерительной Технике.

Известен последовательно-параллельный 5 ключ для цифро-аналоговых преобразователей (ЦАП), содержащий инвертор, согласующий и корректирующий блоки и ключевые транзисторы одного типа проводимсюти, эмиттеры которых объединены и подключе- Ю ны к выходу ключа, коллекторы - к полю сам источника опорного напряжения, а базы к выходу согласующего блока Ц.

Известен также последовательно-парал- |5 лельный ключ для цифро-аналогового преобразователя, вход которого подключен к первому входу и через инвертор ко второму входу согласующего блока и входу корректирующего блока, содержащего конденсате- JQ ры, два выхода которого подключень( к третьему и четвертому входам согласующего блока, выходы согласующего блока подключены к базам ключевых транзисторов, эмиттеры которых объединены и подключе- 25

ны к выходу ключа, а коллекторы - к полюсам источника опорного напряжения 2}.

Недостатки известных последоватет нопараллельных ключей - низкое быстродействие и точность.

Цель изобретения - повышение 6biCTj)i действия и точности.

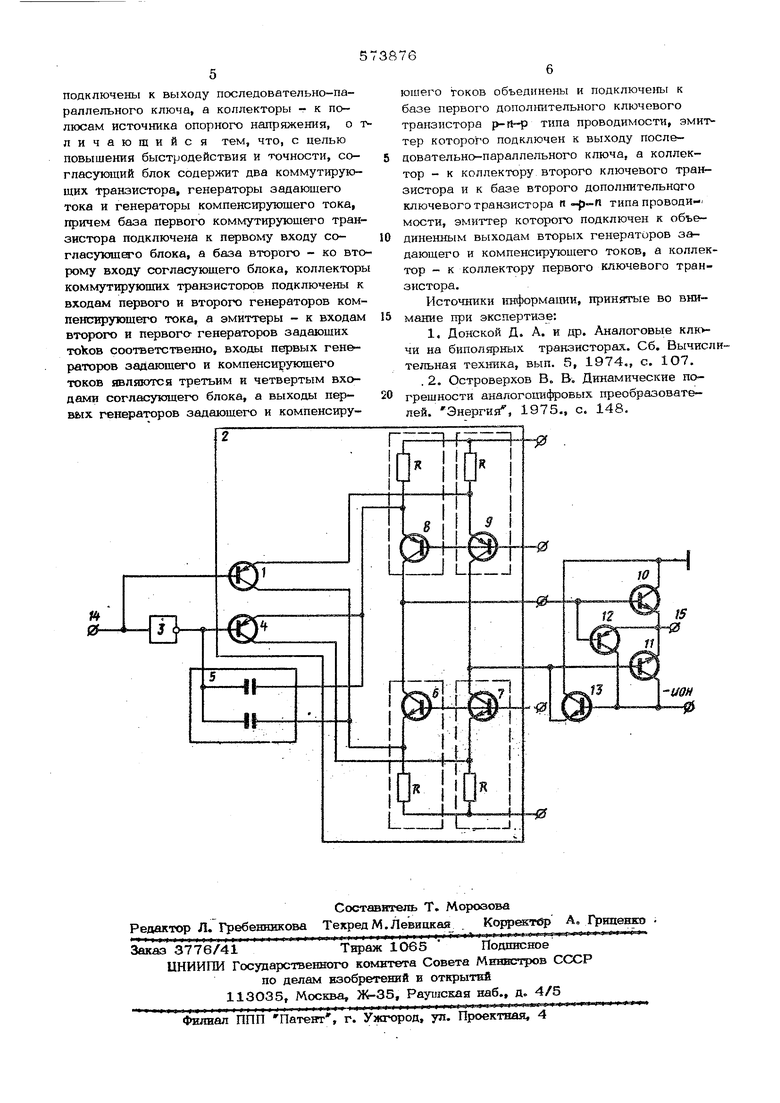

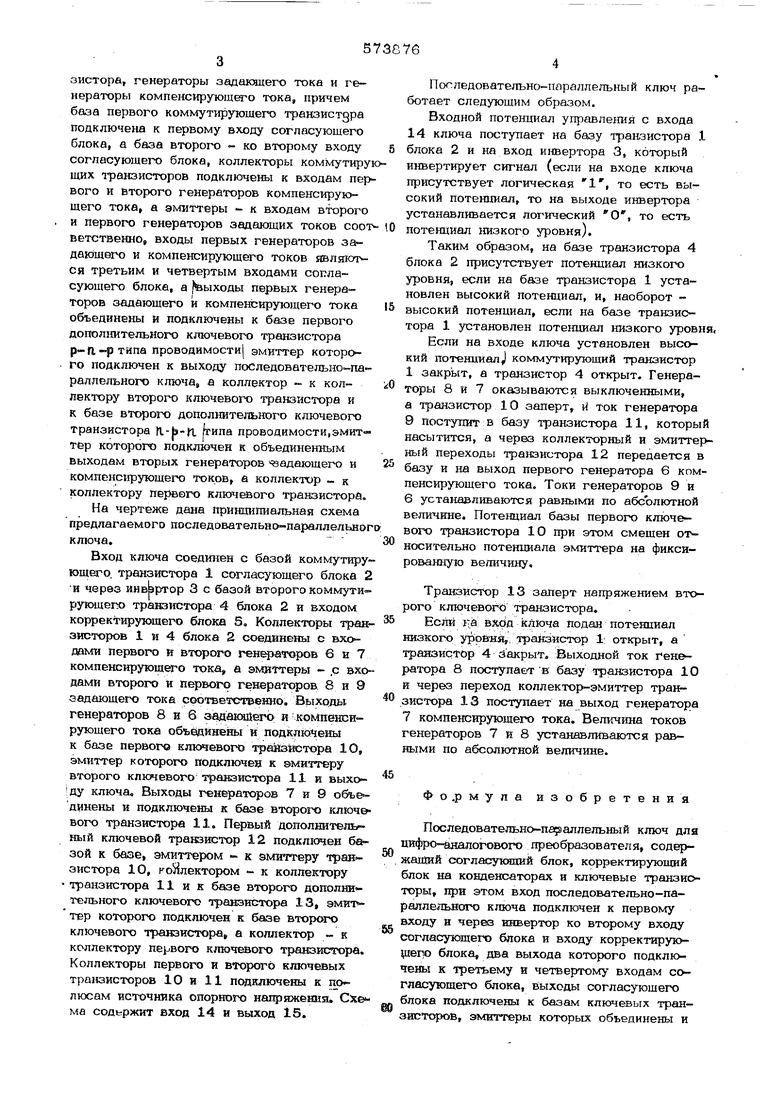

Это достигается тем, что в последовательно-параллельном ключе для цифро-аналогового преобр азователя, содержащем согласующий блок, корректирующий, блок на конденсаторах и ключевые транзисторы, при этом вход последовательно-параллельного ключа подключен к п эвому входу и черет инвертор ко второму входу согласующего блока и входу корректирующего блока, два выхода которого подключены к третьему и четвертому входам согласующего блока, выходы согласующего блока подключены к базам ключевых транзисторюв эмиттеры которых объединены и ггодключены к выходу Последовательно-параллельного ключа, ковпекторы - к полюсам источника ortcpHoro яааряження, согласующий блок содержат Два коммутирующих транаистора, генераторы задакящего тока и ге- нераторь компенсирующего тока, причем база первого коммутируюшего транзистдра подключена к первому входу согласующего блока, а база второго - ко второму входу согласующего блока, коллекторы коммутирую щих ipaHBHCTopoB подключены к входам первого и второго генераторов компенсирующего тока, а эмиттеры - к входам второго и первого генераторов задающих токов соответственно, входы первых генераторов задающего и компенсирующего токов $шляют ся третьим и четвертым входами согласующего блока, а ыходы первых генераторов задающего и компенсирующего тока объединены и подключены к базе первого дополнительного ключевого транзистора р„1г ртипа проводимости) эмиттер которого подключен к выходу последовательно-параллельного ключа, а коллектор к коллектору второго ключевого транзистора и к базе второго допол}П1тельного ключевого транзистора fl-b-Jt типа проводимости,эмит Tfep которого подключен к объединенным Выходам вторых генераторов «адающего и компенс|грующего токов, а коллектор - к коллектору первого ключевого транзнсторй. На чертеже дана принципиальная схема предлагаемого последовательно-параллельног ключа. Вход ключа соединен с базой коммутиру ющего, транзистора 1 согласующего блока 2 и через инвЬртор 3 с базой второго коммути- рующепо транзистора 4 блока 2 и входом корректирующего блока 5, Коллекторы тран зисторов 1 и 4 блока 2 соединены с входами первого н второго генераторов 6 и 7 компенсирующего тока а эмиттеры - .с вхо дами второго и первого генераторов 8 и 9 задающего тока соответственно. Выходы генераторов 8 и 6 эадакийегр икомпенсирующего тока объёдИне)вы и подключены к базе первого ключевого траИзжзтора 10, эмиттер которого подключен к эмиттеру второго ключевоготравэистсра 11 и выхо ду ключа, Выходы генераторов 7 и 9 объединены и подключены к базе второго ключе вого транзистора 11. Первый дополнитеш/ный ключевой транзистор 12 подключен базой к базе, эмитте|Х)м - к эмиггтеру транзистора 10, коллектором - к коллектору транзистора 11 и к базе второго дополнительного ключевого транзистора 13, эмит тер которого подключен к базе второтю ключевого транзистора, а коллектор - к коллектору nejjBoro ключевого траизистора. Коллекторы первого и второго ключевых транзисторов 10 н 11 подключены к по люсам источника опорного напряженна. Схе ма содержит вход 14 и выход 15. Последовательно-параллельный ключ работает следующим образом. Входной потенциал управления с входа 14 ключа поступает на базу транзистора 1 блока 2 и на вход инвертора 3, который инвертирует сигнал (если на входе ключа присутствует логическая I, то есть высокий потенциал, то на выходе инвертора устанавливается логический О, то есть потенциал низкого уровня). Таким образом, на базе транзистора 4 блока 2 присутствует потенциал низкого уровня, если на базе транзистора 1 установлен высокий потенциал, и, наоборот высокий потенциал, если на базе транзистора 1 установлен потенциал низкого уровня. Если на входе ключа установлен высокий потенциал J коммутирующий транзистор 1 закрыт, а транзистор 4 открыт. Генераторы 8 и 7 оказываются выключенными, а транзистор 10 заперт, ri ток генератора 9 поступит в базу транзистора 11, который насытится, а через коллекторный и эмиттериь Й переходы транзистора 12 передается в базу и на выход первого генератора 6 компенсирующего тока. Токи генераторов 9 и 6устанавливаются равными по абсолютной величине. Потенциал базы первого ключевого транзистора 10 при этом смещен относительно потенциала эмиттера на фиксированную величину. Транзистор 13 заперт напряжением второго ключевого транзистора. Если эта вход ключа подан потенциал низкого уррвий,, трайзистхэр 1: открыт, а транзистор 4 закрыт. Выходной ток генератора 8 поступает в базу транзистора 10 и через переход коллектор-эмиттер транзистора 13 поступает на выход генератора 7компенсирующего тока. Величина токов генераторов 7 R 8 устанавливаются равными по абсолютной величине. Фо.рмула изобретения Последовательно-параллельный ключ для цифро-аналогового преобразователя, содержаишй оэгласукиций блок, корректирующий блок на конденсаторах и ключевые транзисторы, при этом вход последовательно-параллельного ключа подключен к первому входу н через инвертор ко второму входу согласующего блока и входу корректирующег о блока, два выхода которого подключены к третьему и четвертому входам согласующего блока, выходы согласующего блока подключены к базам ключевых транзисторов, эмиттеры которых объединены и

Авторы

Даты

1977-09-25—Публикация

1976-04-12—Подача