Изобретение относится к области вычислительной техникиИ касается многоканальных систем обработки и передачи данных.

Известен аналого-цифровой многоканальный преобразователь с адаптивной коммутацией каналов, содержащий коммутатор, преобразователи и блоки памяти 11 . В этом устройстве коммутируется и обрабатывается тот сигнал, который имеет наибольшую вепичину откгюнения текущего значения от предсказываемого. Недостатком этого устройст ва является наличие в каждом канале аналогового преобразователя погрешности aifпроксимации, обладающего всеми недостат ками, присущими аналоговым схемам.

Известен аналого-цифровой преобразователь, содержащий коммутатор, подключенный адресным входом к запоминающему -устройств ву . Аналоговый выход коммутатора соединены со входом сравнивающего устройства и аналого-цифрового преобразователя. Второй вход сравнивающего устройства через и11фро-а 1алоговый преобразователь подключен к информационному выходу запоминающего устройства. Е-ыход аналого-цифрового

2

преобразователя связан с буферной памятью и запоминающим устройством, а выход схемы сравнения через ключ соединен со входом коммутатора и установкой в начальное состояние АЦ-преоР|разователя 2 .

Недостатком известного устройства является низкая пропускная способность, обусловленная непроизводительными затратами времени на опрос сигналов, заведомо невышедших за предсказываемые пределы, в течение которого дорогостоящий аналого-цифровой преобразователь простаивает.

Цель изобретения - повышение пропускной способности преобразователя при незначительных дополнительных затратах оборудо вания.

Это достигается тем, что в аналого-цифровой преобразователь, содержащий коммутатор, соединенный с первым входом экстраполятора и через преобразователь anafloi Koa с буферной памятью и входом запоминающего устройства, выход которого через регистр и цифро-аналоговый преобразователь подключен к второму входу экстранолятора, введены реверсивный счетчик, два элемента сборки.

блок выделения заявок и по одному счетчику и элементу совпадения на каждый входной канал, причем выходы реверсивного счетчика через магистральные шины подключены к параллельным входам счетчиков и соответствуюшим входам запоминающего устройства, выходы счетчиков через соответствующие апе менты совпадений соединены с информационными входами блока выделения заявок, уттрав ляюишй вход которого через первый элемент сборки подключен к пе.ому выходу экстр полятора, вычитающему входу реверсивного счетчика и к выходу конец преобразования преобразователя аналог-код, входы второго элемента сборки подключены соответственно к второму выходу экстраполятора, суммиру ющему входу реверсивного счетчика и к перк вому выходу экстраполятора, а выход второго элемента сборки соединен с входом запоминающего устройства, выход запоминающего устройства подключен к информационным входам реверсивного счетчика, адресный выгход блока.выделения заявок соединен с адресными входами коммутатора и запоминакк щего устройства, а управляющий выход этого же блока - с соответствующими входами всех счетчиков,.

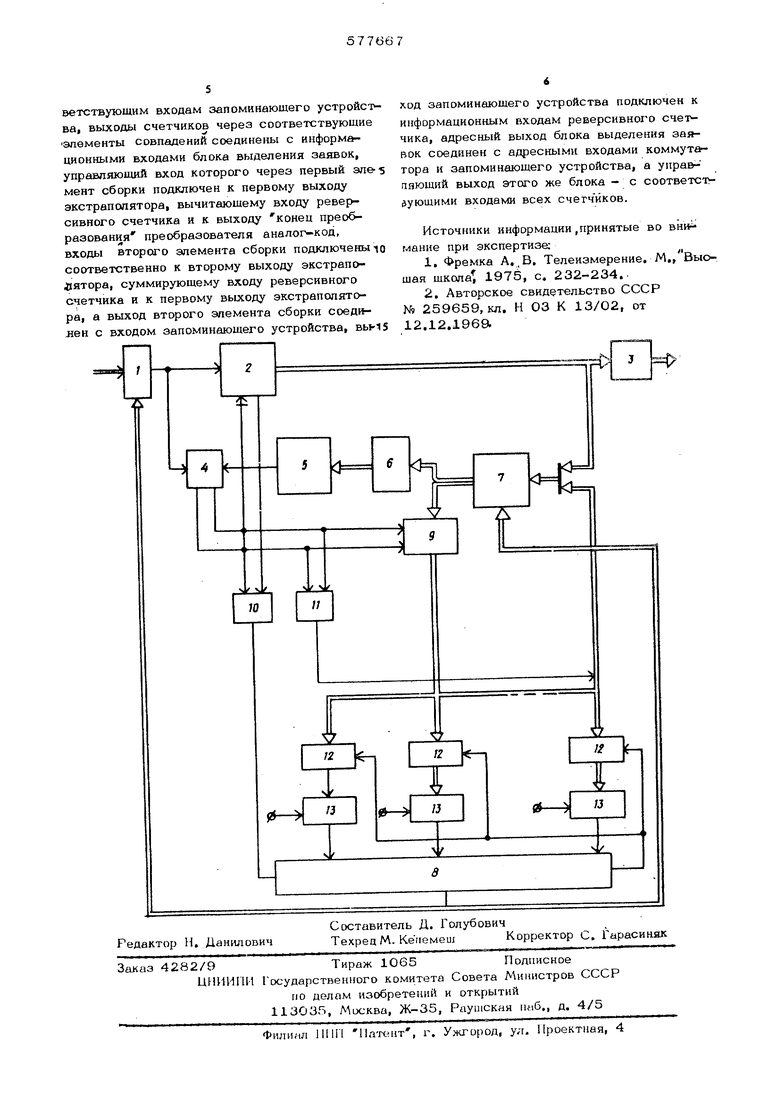

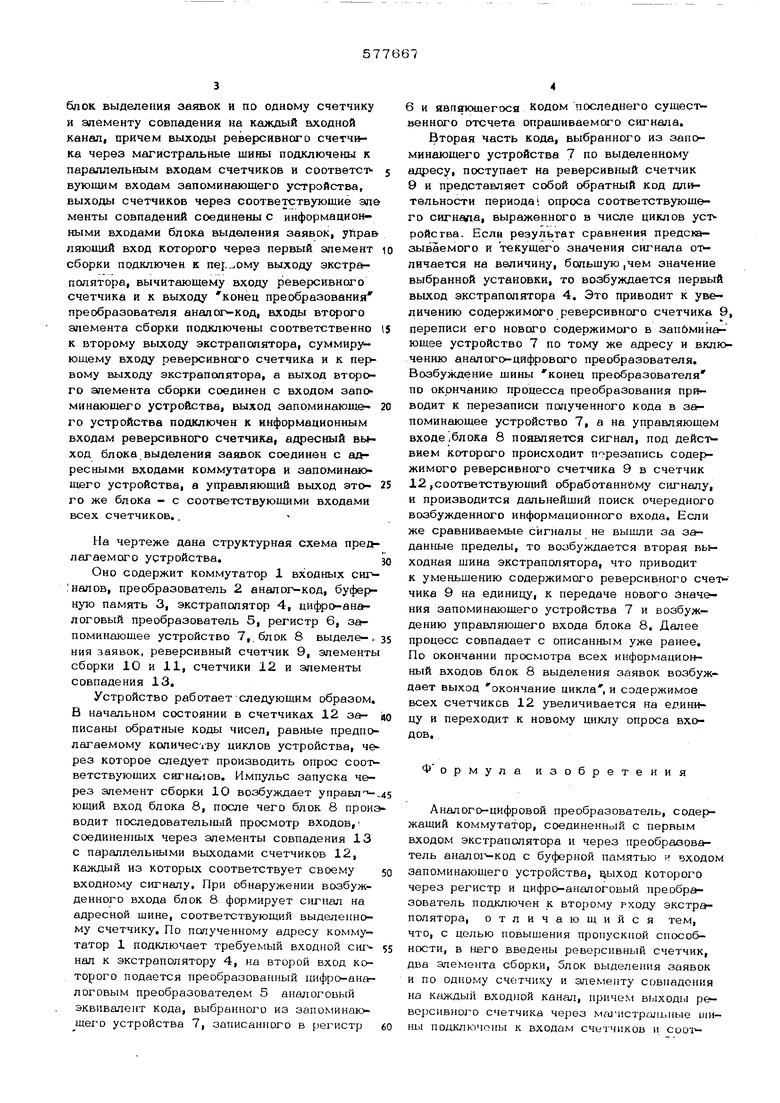

На чертеже дана структурная схема предлагаемого устройства.

Оно содержит коммутатор 1 входных сиг:налов, преобразователь 2 аналог-код, буферную память 3, экстрапопятор 4, ци(|ро-аналоговый преобразователь 5, регистр 6, запоминающее устройство 7,. блок 8 выделе-. ния заявок, реверсивный счетчик 9, элементы сборки 10 и 11, счетчики 12 и элементы совпадения 13.

Устройство работает следующим образом. В начальном состоянии в счетчиках 12 записаны обратные коды чисел, равные предполагаемому количес ву циклов устройства, через которое следует производить опрос соответствующих снгнвгюв. Импульс запуска через элемент сборки 1О возбуждает управл ющий вход блока 8, поспе чего блок 8 прои водит последовательный просмотр входов,соединенных через элементы совпадения 13 с параллельными выходами счетчиков 12, каждый из которых соответствует своему входному сигналу. При обнаружении возбужденного входа блок 8 формирует сигнал на адресной шине, соответствующий выделенному счетчику. По полученному адресу коммутатор 1 подключает требуемый входной сигнал к экстраполятору 4, на второй вход которого подается преобразова 1ный цифро-аналоговым преобразователем 5 аналоговый эквивалент кода, выбранного из запоминаю щего устройства 7, записанного в регистр

6 и явпшощегося кодом последнего сущес-гвенного отсчета опращиваемого сигнала.

Вторая часть кода, выбранного из запоминающего устройства 7 по выделенному адресу, поступает на реверсивный счетчик 9 и представляет собой обратный код длительности периода опроса соответствующего сигнала, выраженного в числе циклов устройства. Если результат сравнения предсказываемого и текущего значения от личается на величину, большую ,чем значение выбранной установки, то возбуждается первы выход экстраполятора 4, Это приводит к увеличению содержимого реверсивного счетчика переписи его нового содержимого в запбминающее устройство 7 по тому же адресу и вклчению аналого-цифрового преобразователя. Возбуждение шины конец преобразователя по окончанию процесса преобразования приводит к перезаписи полученного кода в запоминающее устройство 7, а на управляющем входе,блока 8 появляется сигнал, под дейст вием которого происходит перезапись содержимого реверсивного счетчика 9 в счетчик 12 ,соответствующий обработанному сигналу, и производится дальнейший поиск очередного возбужденного информационного входа. Если же сравниваемые сигналы не вышли за заданные пределы, то возбуждается вторая выходная шина экстраполятора, что приводит к уменьшению содержимого реверсивного сче чика 9 на единицу, к передаче нового значения запоминающего устройства 7 и возбуждению управляющего входа блока 8. Далее процесс совпадает с описанным уже ранее. По окончании просмотра всех информационный входов блок 8 выделения заявок возбуждает выход окончание цикла , и содержимое всех счетчиков 12 увеличивается на единицу и переходит к новому циклу опроса входов.

Ф о

рмула изобретения

Аналого-цифровой преобразователь, содержащий коммутатор, соединенно1й с первым входом экстраполятора и через преобразователь анало -код с буферной памятью к входом запоминающего устройства, ыход KOTopoi o через регистр и цифро-анопоговый преобразователь подключен к второму рходу экстраполятора, отличающийся тем, что, с целью повышения пропускной способности, в него введены реверсивный счетчик, два элемента сборки, блок выделения заявок и по одному счетчиху и элементу совпадения на к;1ждый входной канал, причем выходы реверсивнодо счетчика через мшнстральные шины подключены к входам счетчиков и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1976 |

|

SU627503A1 |

| Устройство обработки информации | 1979 |

|

SU822350A1 |

| Устройство для регистрации аналоговой информации | 1982 |

|

SU1164548A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРОЯТНОСТНЫХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU432512A1 |

| Устройство для ввода информации | 1983 |

|

SU1124274A1 |

| Многоканальный преобразователь угол-фаза-код | 1983 |

|

SU1120385A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Устройство для передачи телеизмерений с адаптивной коммутацией | 1984 |

|

SU1267459A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ МНОГОЭЛЕМЕНТНОГО ПРИЕМНИКА | 1992 |

|

RU2025905C1 |

Авторы

Даты

1977-10-25—Публикация

1976-07-01—Подача