Изобретение относится к вычислительной и цифровой измерительной технике.

Цель изобретения - повышение точности аналого-цифрового преобразования .

Известные аналого-цифровое преобразователи следящего типа являются относительно простыми устройствами, большинство из которых используют в цепи обратной связи ЦАП параллельного действия, построенный на основе классического двоичного кода. Наличие в таких ЦАП разрядов, имеющих отклонения от требуемых значений, при-, водит к тому, что выходная характе- ристика может иметь разрывы и носит сложный скачкообразный характер. В этом случае для целой области значений выходного аналогового сигнала может не существовать входных входов, Т.е. сигналы с зтими значениями вообще не могут появиться на выходе ДАЛ. Применение такого ЦАП в АЦП приведет к тому, что появятся области значений входного сигнала, которые не могут быть уравновешены компенсирующим сигналом ЦАП с точностью до младщего разряда.

рекции и самопроверки. Сущность само- 25 - сравнение аналоговых сигналов

А, и Ад, на его входах, причем сигна Y на его выходе 21 соединенном с пе вым входом блока 15 управления, под чиняется следующему соотношению:

проверки заключается в определении m переходных кодовых комбинаций, причем переходная кодовая комбинация х-го разряда соответствует вьгходноМу сШалоговому сигналу ЦАП меньшему реального веса i-ro разряда на величину младшего кванта.

При этом, если в процессе аналого- цифрового преобразования выявлять переходные кодовые комбинаций в счетчике, управляющем ЦАП, а затем корректировать состояние счетчика, то скачки выходной характеристики ЦАП значительно (теоретически полностью) уменьшены.

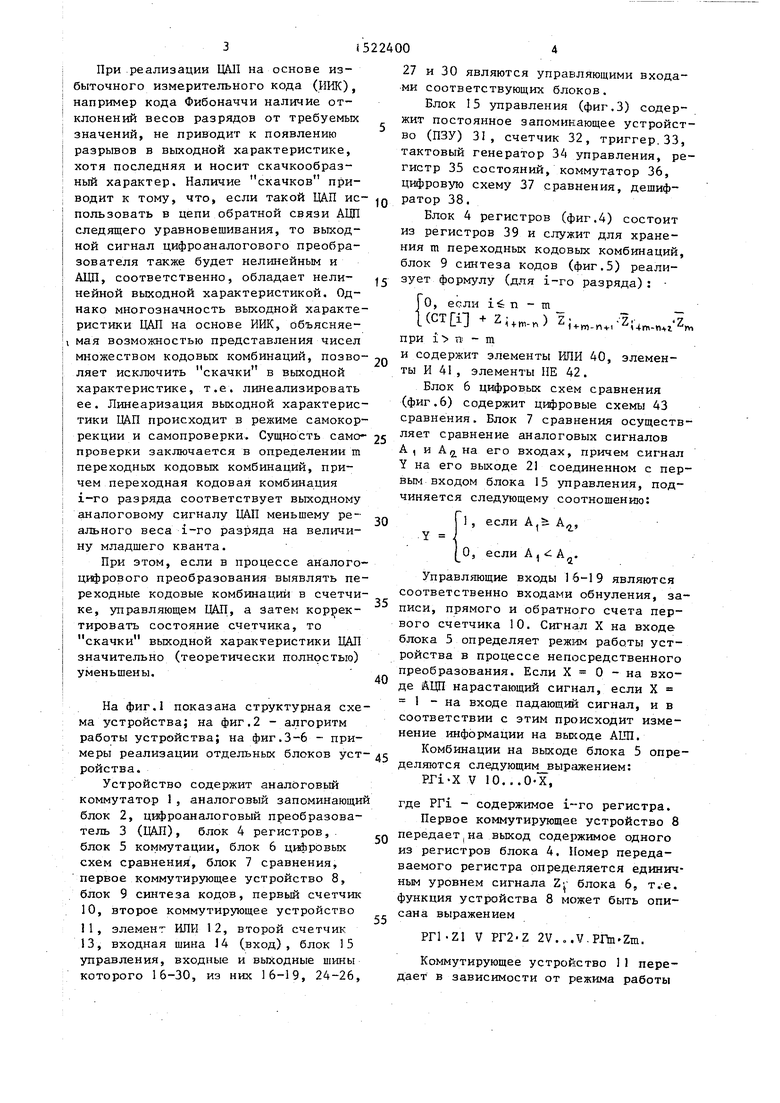

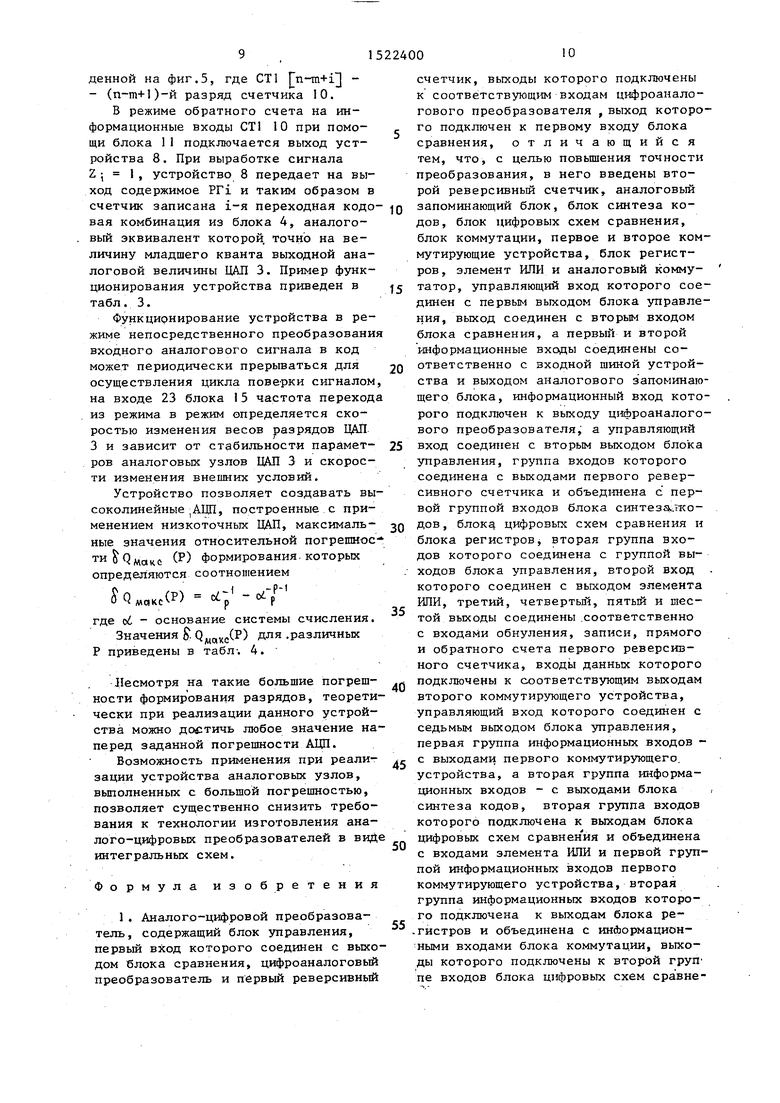

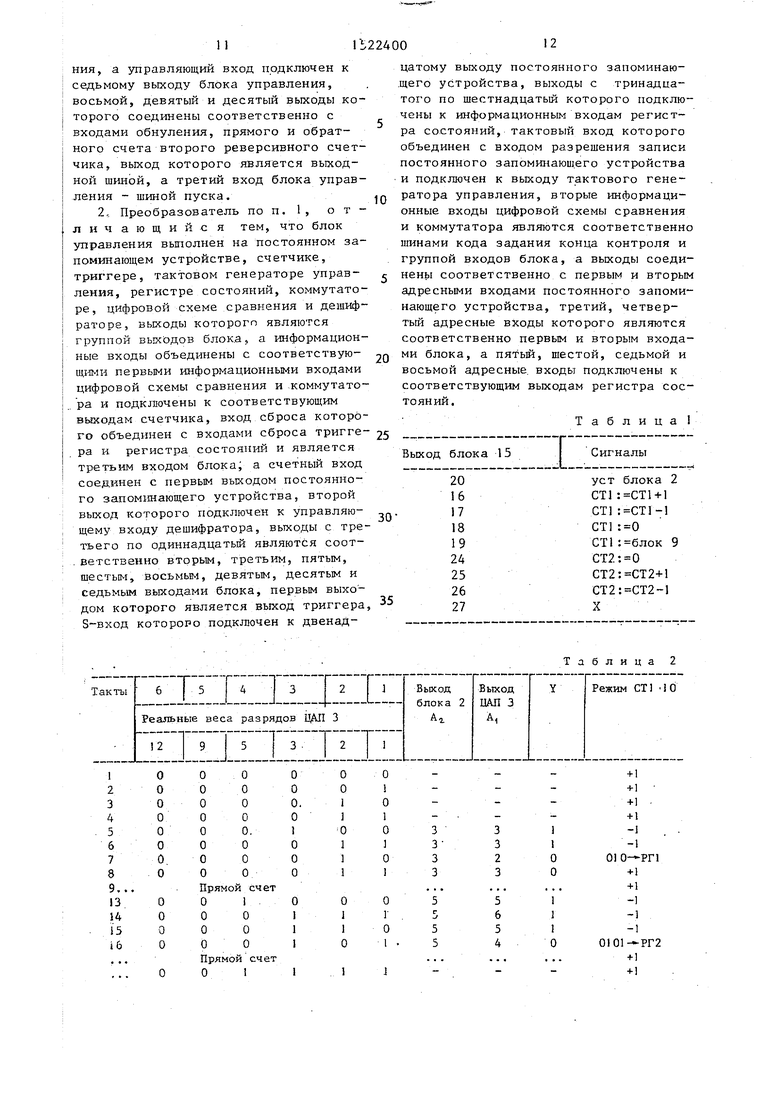

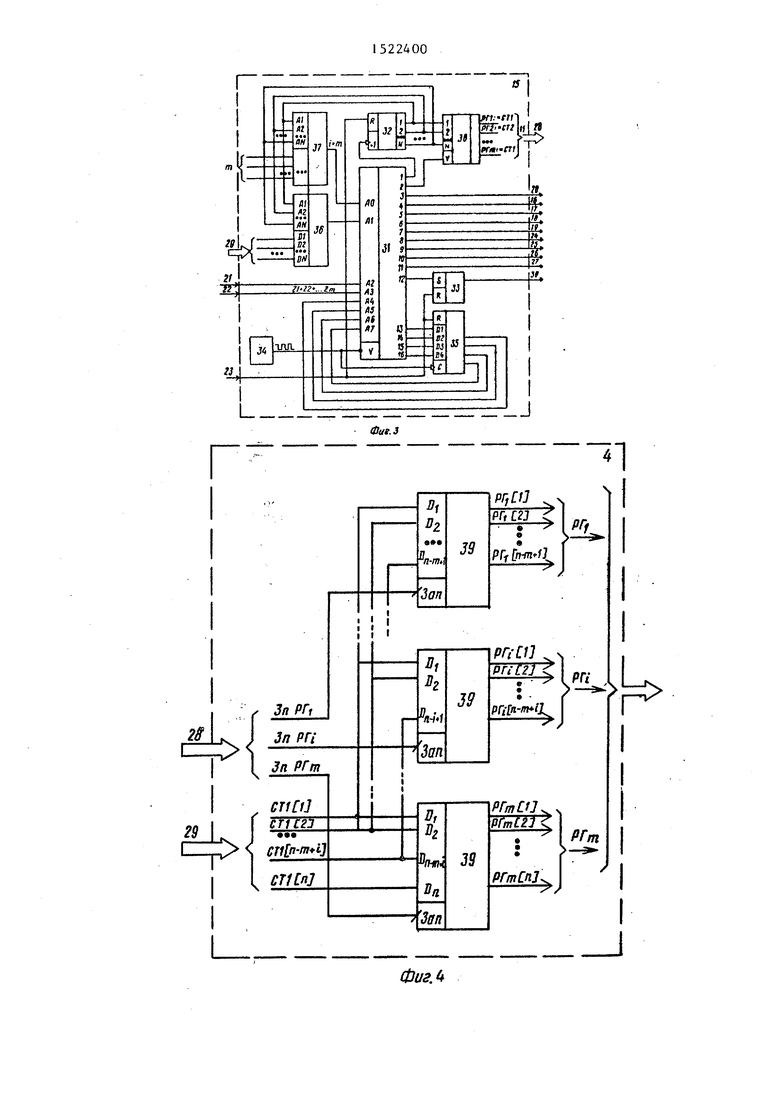

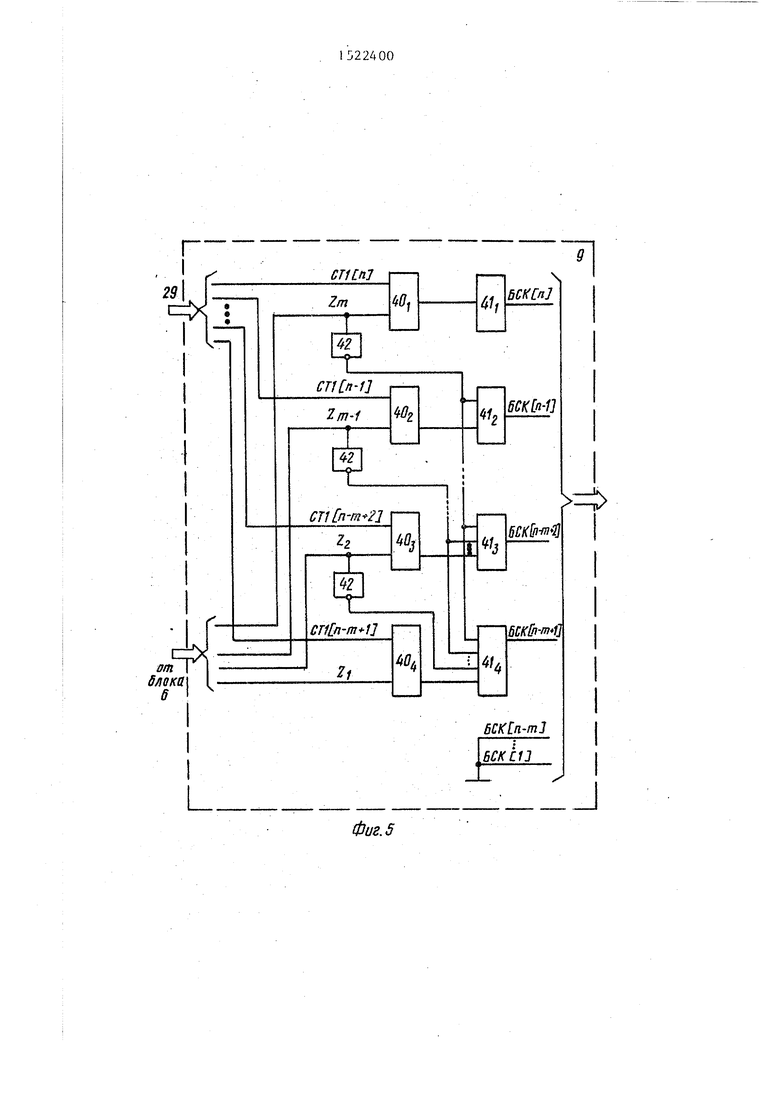

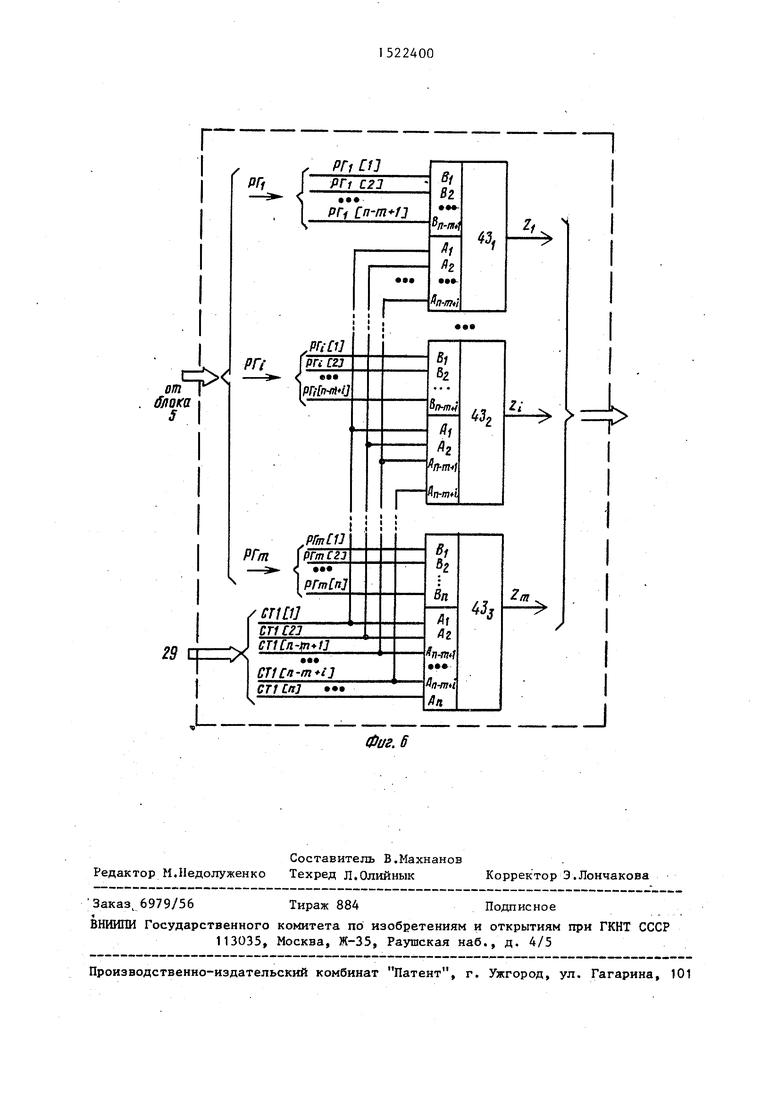

На фиг.1 показана структурная схема устройства; на фиг.2 - алгоритм работы устройства; на фиг.3-6 - примеры реализации отдельных блоков уст ройства.

Устройство содержит аналоговый коммутатор 1, аналоговый запоминающи блок 2, цифроаналоговый преобразователь 3 (ЦАП), блок 4 регистров,. блок 5 коммутации, блок 6 циЬровых схем сравнения, блок 7 сравнения, первое коммутирующее устройство 8, блок 9 синтеза кодов, первьй счетчик 10, второе коммутирующее устройство И, элемент ИЛИ 12, второй счетчик 13, входная шина 14 (вход), блок 15 управления, входные и выходные шины которого 16-30, из них 16-19, 24-26,

- сравнение аналоговых сигналов

А, и Ад, на его входах, причем сигнал Y на его выходе 21 соединенном с первым входом блока 15 управления, подчиняется следующему соотношению:

Y

если А , i А .

Управляющие входы 16-19 являются соответственно входами обнуления, записи, прямого и обратного счета первого счетчика 10. Сигнал X на входе блока 5 определяет реж работы устройства в процессе непосредственного преобразования. Если X О - на входе АЦП нарастающий сигнал, если X 1 - на входе падающий сигнал, и в соответствии с этим происходит изменение информации на вьосоде А1Ш.

Комбинации на выходе блока 5 определяются следующим выражением:

PPi-X V 10...О Х,

где Pri - содержимое г--го регистра.

Первое коммутирующее устройство 8 передает на выход содержимое одного из регистров блока 4. Номер передаваемого регистра определяется единичным уровнем сигнала блока 6, т. е. функция устройства 8 может быть описана выражением

Pn-Zl V Pr2 Z 2V...V.PIln Zm.

Коммутирующее устройство 1 1 передает в зависимости от режима работы

1522400

устройства На вход счетчика 10 содер- рядов от требуемых значений для старших разрядов будут большими, а для младших - малыми. При этом определение кодов реальных весов разрядов, или для данного случая переходньк кодовьк комбинаций должно производиться только для группы старших разрядов .

10 При таком подходе для определения переходных кодовых комбинаций только старших разрядов необходимо приьшне- ние счетчика, работающего в фибонач- чиевой системе счиления. Такие счет- t5 чики существуют, но являются довольно сложными устройствами. Поэтому для того, чтобы в качестве счетчика 10 можно было иметь обычньй двоичньа счетчик, предложено определить пере- РГ(1) содержимое i-ro регистра бло- 20 ходные кодовые комбинации для всех

ка 4;разрядов, веса которых отличны от

CT(i) - содержимое группы из (п - m + степени двойки. При этом для 1-кода + i) младших разрядов счетчи- Фибоначчи с младшими разрядами ... ка 10;8; 5; 3; 2; 1, для которого приводятп - число разрядов первого счет- 25 ся все дальнейшие примеры, определе- чика 10, определяемое разряд- ние переходных кодовых комбинаций

жимое одного из регистров блока 4 (при X 0) или блока 9 (при X 1).

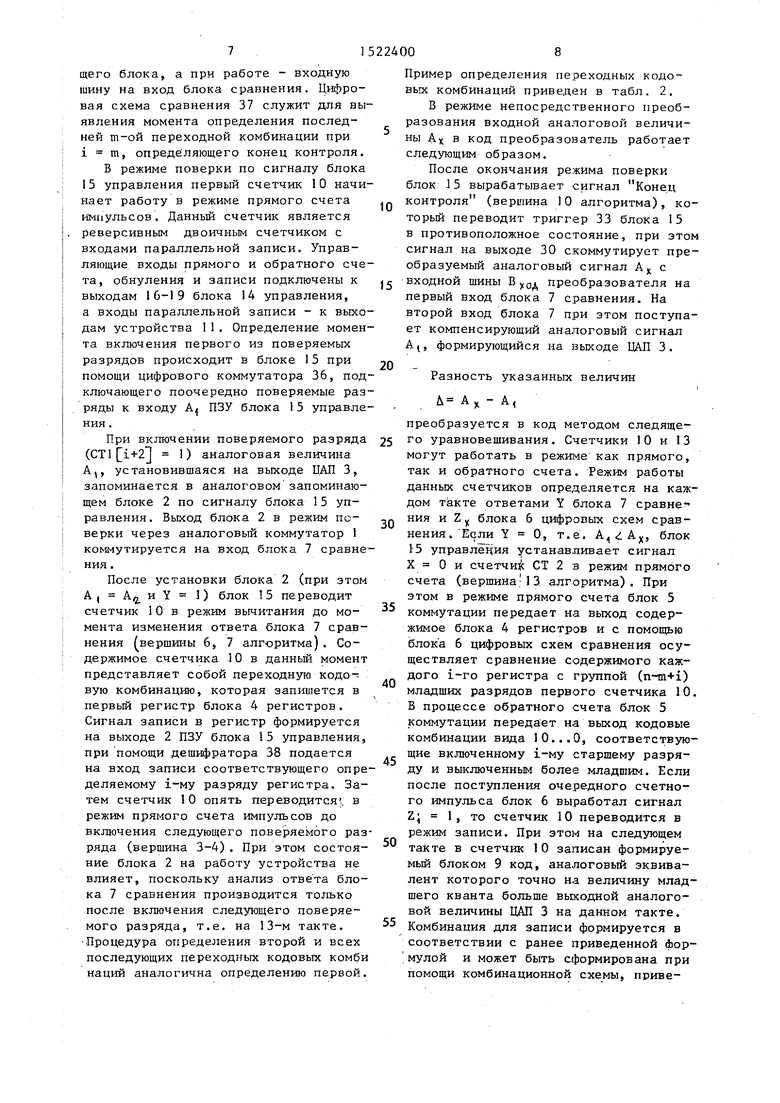

Блок 9 формирует кодовую комбинацию, записьгеаемую в счетчик 10 в режиме прямого счета, после выявления на выходе первого счетчика 10 переходной кодовой комбинации.

Комбинация для записи формируется по содержимому счетчика 10 и выходным сигналом Z , блока 6. Выходные сигналы блока 6 формируются следующим образом:

1, если СТ1 (i) РГ (i),

Z, О, если СТ1 (i) / РГ (i), где i 1,2,,..,т;

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1197078A1 |

| Устройство цифро-аналогового преобразования | 1985 |

|

SU1312739A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221755A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Применение самокоррекции, основанной на использовании избыточного измерительного кода (ИИК), обеспечивает высокую точность преобразователя. Сущность самокоррекции заключается в определении переходных кодовых комбинаций, которые затем выявляются в процессе аналого-цифрового преобразования в счетчике, управляющем ЦАП, для корректировки состояния счетчика. Самокоррекция осуществляется при помощи цифроаналогового преобразователя, блока регистров, аналогового запоминающего блока, блока сравнения и блока управления. Введение блока цифровых схем сравнения, блока синтеза кодов, первого коммутирующего устройства, второго коммутирующего устройства и блока коммутации позволяет осуществить преобразование аналоговых величин в цифровые по методу следящего уравновешивания. 1 з.п. ф-лы, 6 ил., 4 табл.

костью цифроаналогового преобразователя 3; m - количество переходных кододолжно начинаться с 3-го разряда.

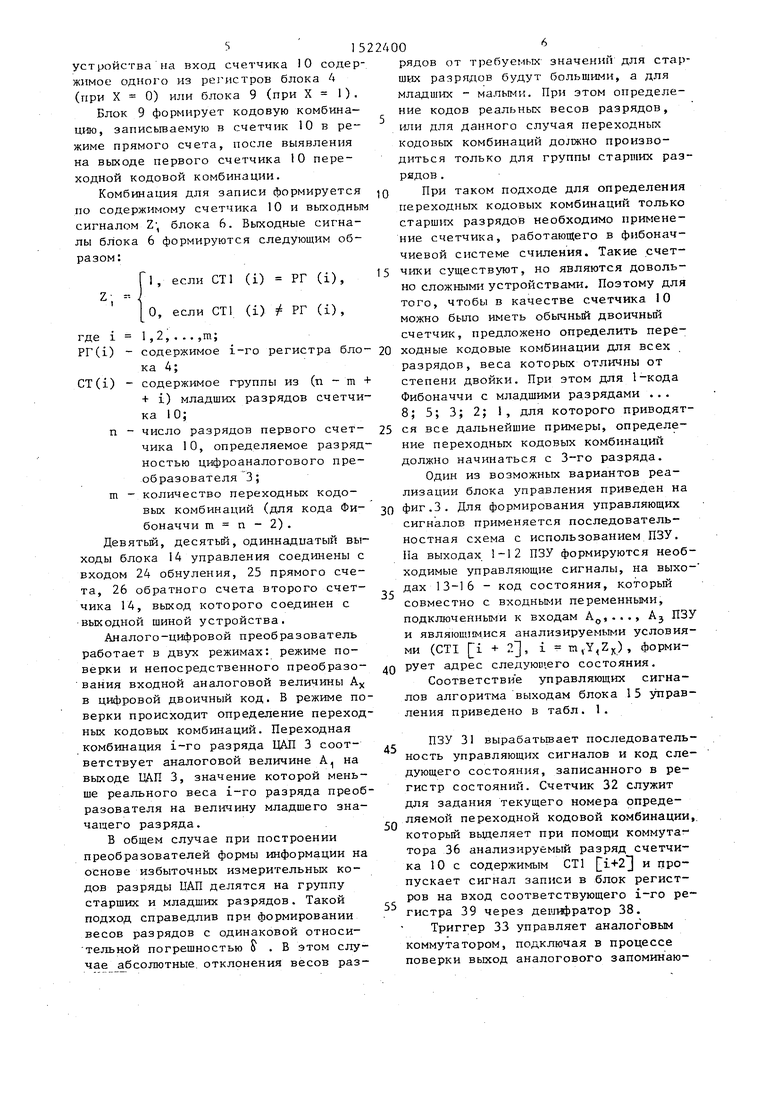

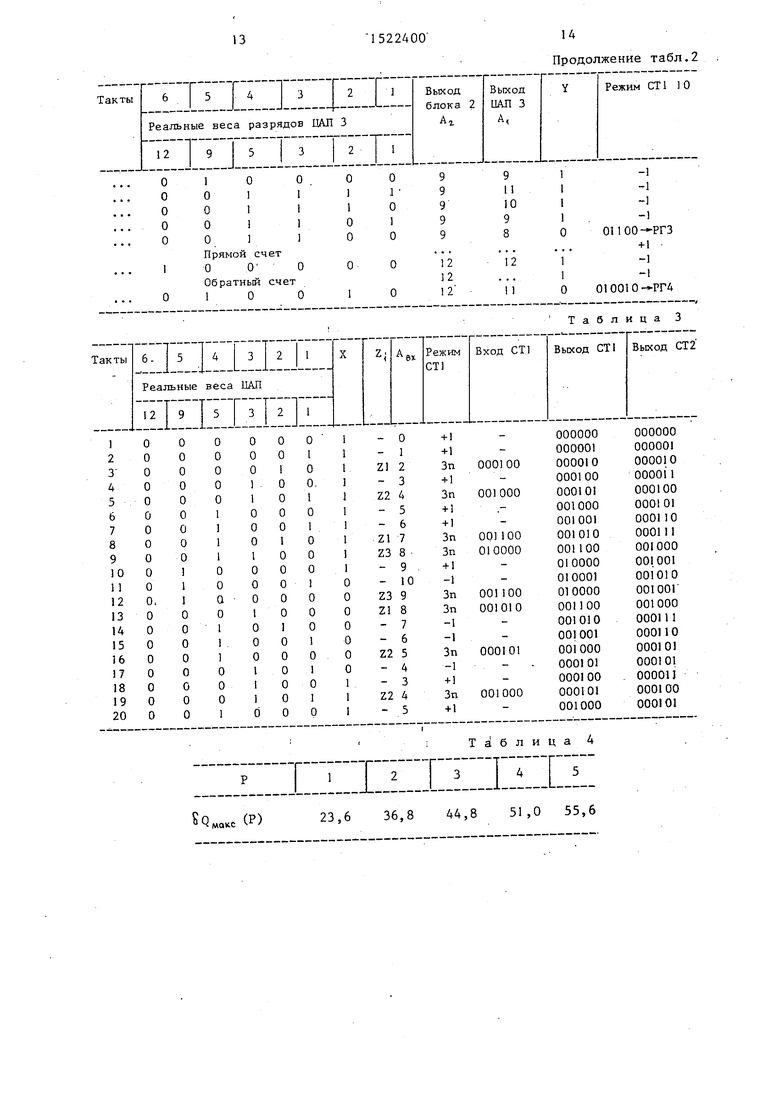

Один из возможных вариантов реализации блока управления приведен на вых комбинаций (для кода Фи- зо Фиг.З. Для формирования управляющих боначчи m п - 2).сигналов применяется последовательДевятьй, десятый, одиннадцатый вы- ностная схема с использованием ПЗУ. ходы блока 14 управления соединены с входом 24 обнуления, 25 прямого счеila выходах. 1-12 ПЗУ формируются необ ходимые управляющие сигналы, на выходах 13-16 - код состояния, который совместно с входными переменными, подключенными к входам А, .. ., Aj ПЗУ и являющимися анализируемыми условиями (CTI i + ., i Tn,), формита, 26 обратного счета второго счетчика 14, выход которого соединен с выходной шиной устройства.

Аналого-цифровой преобразователь работает в двух режимах: режиме по45

верки и непосредственного преобразо- д рует адрес следующего состояния.

вания входной аналоговой величины А Соответствий управляющих сигна- в цифровой двоичный код. В режиме по- лов алгоритма выходам блока 15 управ- верки происходит определение переход- ления приведено в табл. 1. ных кодовых комбинаций. Переходная комбинация i-ro разряда ЦАП 3 соответствует аналоговой величине А;, на выходе 1ДЛ.П 3, значение которой меньше реального веса i-ro разряда преобразователя на величину младшего значащего разряда.

В общем случае при построении преобразователей формы информации на основе избыточных измерительных кодов разряды ПАП делятся на группу старших и младших разрядов. Такой подход справедлив при формировании весов разрядов с одинаковой относи тельной погрешностью S . В этом случае абсолютные, отклонения весов разПЗУ 31 вырабатьшает последовательность управляющих сигналов и код следующего состояния, записанного в регистр состояний. Счетчик 32 служит для задания текущего номера опреде- ляемой переходной кодовой комбинации,. который вьщеляет при помощи коммутатора 36 анализируемый разряд счетчика 1 О с содержимым СТ1 i+2 и пропускает сигнал записи в блок регистров на вход соответствующего i-ro регистра 39 через деши5)ратор 38.

Триггер 33 управляет аналоговым коммутатором, подключая в процессе поверки выход аналогового запоминаю ностная схема с использованием ПЗУ.

35

ila выходах. 1-12 ПЗУ формируются необходимые управляющие сигналы, на выходах 13-16 - код состояния, который совместно с входными переменными, подключенными к входам А, .. ., Aj ПЗУ и являющимися анализируемыми условиями (CTI i + ., i Tn,), форми5

Соответствий управляющих сигна- лов алгоритма выходам блока 15 управ- ления приведено в табл. 1.

ПЗУ 31 вырабатьшает последовательность управляющих сигналов и код следующего состояния, записанного в регистр состояний. Счетчик 32 служит для задания текущего номера опреде- ляемой переходной кодовой комбинации,. который вьщеляет при помощи коммутатора 36 анализируемый разряд счетчика 1 О с содержимым СТ1 i+2 и пропускает сигнал записи в блок регистров на вход соответствующего i-ro регистра 39 через деши5)ратор 38.

Триггер 33 управляет аналоговым коммутатором, подключая в процессе поверки выход аналогового запоминающего блока, а при работе - входную шину на вход блока сравнения. Цифровая схема сравнения 37 служит для выявления момента определения последней т-ой переходной комбинации при i т, опреде ляющего конец контроля.

В режиме поверки по сигналу блока 5 управления первый счетчик 10 начинает работу в режиме прямого счета импульсов. Данный счетчик является реверсивным двоичным счетчиком с входами параллельной записи. Управляющие входы прямого и обратного счета, обнуления и записи подключены к выходам 16-19 блока 14 управления, а входы параллельной записи - к выходам устройства I1. Определение момента включения первого из поверяемых разрядов происходит в блоке I5 при помощи цифрового коммутатора 36, подключающего поочередно поверяемые разряды к входу А ПЗУ блока 15 управления .

При включении поверяемого разряда ( 1) аналоговая величина А,, установившаяся на выходе ЦАП 3, запоминается в аналоговом запоминающем блоке 2 по сигналу блока 15 управления. Выход блока 2 в режим поверки через аналоговый коммутатор 1 коммутируется на вход блока 7 сравнения .

После установки блока 2 (при этом А , А и Y ) блок 15 переводит счетчик 10 в режим вычитания до момента изменения ответа блока 7 сравнения вершины 6, 7 алгоритма). Содержимое счетчика 10 в данный момент представляет собой переходную кодовую комбинацию, которая запишется в первый регистр блока 4 регистров. Сигнал записи в регистр формируется на выходе 2 ПЗУ блока 15 управления, при помощи дешифратора 38 подается на вход записи соответствующего определяемому i-му разряду регистра. Затем счетчик 0 опять переводится ., в режим прямого счета импульсов до включения следующего поверяемого разряда (верщина 3-4). При этом состояние блока 2 на работу устройства не

влияет, поскольку анализ ответа блока 7 сравнения производится только после включения следующего поверяемого разряда, т.е. на 13-м такте. Процедура определения второй и всех последующих переходных кодовых комби наций аналогична определению первой.

Пример определения переходных кодовых комбинаций приведен в табл. 2,

В режиме непосредственного преобразования входной аналоговой величины АХ в код преобразователь работает следующим образом.

После окончания режима поверки блок J5 вырабатывает сигнал Конец контроля (вершина 10 алгоритма), который переводит триггер 33 блока 15 в противоположное состояние, при этом сигнал на выходе 30 скоммутирует преобразуемый аналоговый сигнал А с входной шины преобразователя на первый вход блока 7 сравнения. На второй вход блока 7 при этом поступает компенсирующий аналоговый сигнал А,, формирующийся на вькоде ЦАП 3.

5

0

0

5

Разность указанных величин А - А

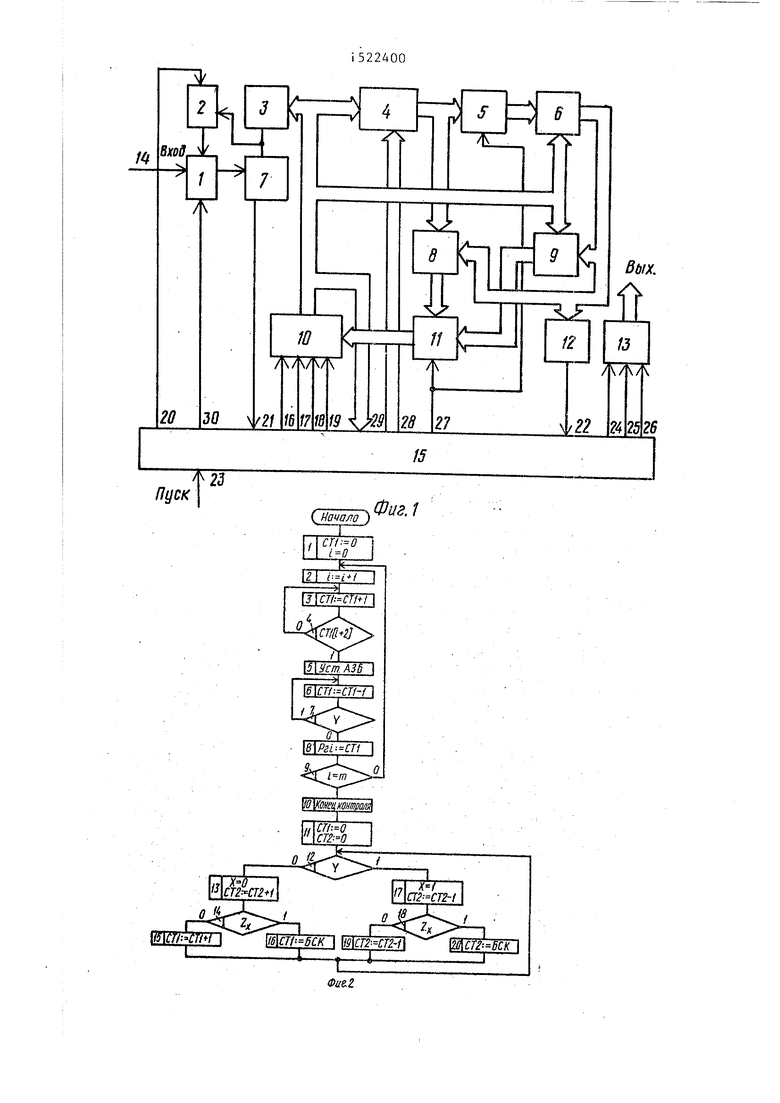

преобразуется в код методом следящего уравновешивания. Счетчики 10 и 13 могут работать в режи1У1е как прямого, так и обратного счета. Режим работы данных счетчиков определяется на каждом такте ответами Y блока 7 сравне ния и Z блока 6 цифровых схем сравнения. Если Y О, т.е. А,гА, блок 1-5 управлё ция устанавливает сигнал X О и счетчи СТ 2 в режим прямого счета (вершина;13 алгоритма). При этом в режиме прямого счета блок 5 коммутации передает на выход содержимое блока 4 регистров и с помощью блока 6 цифровых схем сравнения осуществляет сравнение содержимого каждого i-ro регистра с гр5гппой (n-m+i) младших разрядов первого счетчика 10. В процессе обратного счета блок 5 коммутации передает на выход кодовые комбинации вида 10...О, соответствующие включенному i-му старшему разряду и выключенным более младшим. Если после поступления очередного счетного импульса блок 6 выработал сигнал Z; 1, то счетчик 10 переводится в режим записи. При этом на следующем такте в счетчик 10 записан формируемый блоком 9 код, аналоговый эквивалент которого точно на величину младшего кванта больше вькодной аналоговой величины ЦАП 3 на данном такте. Комбинация для записи формируется в со.ответствии с ранее приведенной фор- мулой и может быть сформирована при помощи комбинационной схемы, приве0

5

0

денной на фиг.5, где СТ1 n-m+i - - (п-т+1)-й разряд счетчика 10.

В режиме обратного счета на информационные входы СТ1 10 при помощи блока 11 подключается выход устройства 8. При выработке сигнала Z ; 1, устройство 8 передает на выход содержимое РГ1 и таким образом в счетчик записана i-я переходная кодо вая комбинация из блока 4, аналоговый эквивалент которой, точно на величину младшего кванта выходной аналоговой величины ЦАП 3. Пример функционирования устройства приведен в табл. 3.

Функционирование устройства в режиме непосредственного преобразовани входного аналогового сигнала в код может периодически прерываться для осуществления цикла поверки сигналом на входе 23 блока I5 частота переход из режима в режим определяется скоростью изменения весов разрядов ЦАП 3 и зависит от стабильности параметров аналоговых узлов ЦАП 3 и скорости изменения внешних условий.

Устройство позволяет создавать высоколинейные , АЦП, построенные с применением низкоточных ЦАП, максимальные значения относительной погрешнос (3,(i (Р) формирования, которых определяются соотношением

ЬмоксСР) р где oi - основание системы счисления.

для .различных 4.

Значения 8- РМПКС Р приведены в табл-.

Д1есмотря на такие большие погрешности формирования разрядов, теоретически при реализации данного устройства можно достичь любое значение наперед заданной погрешности АЦП.

Возможность применения при реализации устройства аналоговых узлов, вьтолненных с большой погрешностью, позволяет сушественно снизить требования к технологии изготовления аналого-цифровых преобразователей в виде интегральных схем.

Формула изобретения

5

Q

0

5

0

5

0

5

0

5

счетчик, выходы которого подключены к соответствующим входам цифроанало- гового преобразователя , выход которого подключен к первому входу блока сравнения, отличающийся тем, что, с целью повьш1ения точности преобразования, в него введены второй реверсивный счетчик, аналоговый запоминающий блок, блок синтеза кодов, блок цифровых схем сравнения, блок коммутации, первое и второе коммутирующие устройства, блок регистров, элемент ИЛИ и аналоговый коммутатор, управляющий вход которого соединен с первым выходом блока управления, выход соединен с вторым входом блока сравнения, а первый и второй информационные входы соединены соответственно с входной шиной устройства и выходом аналогового запоминающего блока, информационный вход которого подключен к выходу цифроаналого- вого преобразователя, а управляющий вход соединен с вторьм выходом блока управления, группа входов которого соединена с выходами первого реверсивного счетчика и объединена с первой группой входов блока синтеза..тко- дов, блок цифровых схем сравнения и блока регистров, вторая группа входов которого соединена с группой выходов блока управления, второй вход которого соединен с выходом элемента ИПИ, третий, четвертьп, пятый и шестой выходы соединены .соответственно с входами обнуления, записи, прямого и обратного счета первого реверсивного счетчика, входы данных которого подключены к соответствующим выходам второго коммутирующего устройства, управляющий вход которого соединен с седьмым выходом блока управления, первая группа информационных входов - с выходами первого коммутирующего, устройства, а вторая группа информационных входов - с выходами блока синтеза кодов, вторая группа входов которого подключена к выходам блока цифровых схем сравнен ия и объединена с входами элемента ИЛИ и первой группой информационных входов первого коммутирующего устройства, вторая группа информационных входов которого подключена к выходам блока ре- -гистров и объединена с информацион- ными входами блока коммутации, выходы которого подключены к второй груп пе входов блока цифровых схем сравне

ния, a управляющий вход подключен к седьмому выходу блока управления, восьмой, девятый и десятый выходы которого соединены соответственно с входами обнуления, прямого и обратного счета второго реверсивного счетчика, выход которого является выходной шиной, а третий вход блока управления - шиной пуска.

2, Преобразователь по п. 1, отличающийся тем, что блок управления выполнен на постоянном запоминающем устройстве, счетчике, триггере, тактовом генераторе управления, регистре состояний, коммутаторе, цифровой схеме сравнения и дешифраторе, выходы которого являются группой вькьдов блока, а информационные входы объединены с соответствующими первыми информационными входами цифровой схемы сравнения и коммутато- ра и подключены к соответствующим выходам счетчика, вход сброса которого объединен с входами сброса тригге- ра и регистра состояний и является третьим входом блока; а счетньш вход соединен с первым выходом постоянного запоминающего устройства, второй выход которого подключен к управляющему входу дешифратора, выходы с третьего по одиннадцатьм являются соот- . ветственно вторым, третьим, пятым, шестым. Восьмым, девятым, десятым и седьмь1м выходами блока, первым выходом которого является выход триггера S-вход которого подктаочен к двенад

5

0

цатому выходу постоянного запоминающего устройства, выходы с тринадцатого по шестнадцатью которого подключены к информационным входам регистра состояний, тактовый вход которого объединен с входом разрешения записи постоянного запоминающего устройства и подключен к выходу тактового генератора управления, вторые информационные входы цифровой схемы сравнения и коммутатора являются соответственно шинами кода задания конца контроля и группой входов блока, а выходы соеди- нень соответственно с первым и вторым адресными входами постоянного запоминающего устройства, третий, четвертый адресные входы которого являются соответственно первым и вторым входами блока, а пятьй, щестой, седьмой и восьмой адресные, входы подключены к соответствующим выходам регистра состояний.

Таблица

Таблица 2

Продолжение табл.2

t2J fJgcK I

{ Иачало) Г

Е

{J CTI-CTf i I

,4

ПГ

шг2 - ст2 П

1

Фиг.1

I

Г

fn.-ftt ffT crt In Я

tr f4c

ir«M.mJ

Фиг.З

л

ь

рг

ФигЛ

29

BCKLn-m

век си

J

Фиг. 5

..

блока I S

prf

29

1

4

J

Фиг. В

| Аналого-цифровой преобразователь | 1979 |

|

SU783979A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразование информации в аналого-цифровых вычислительных устройствах и системах/Под ред | |||

| Г.М.Петрова, 1973, с | |||

| Переносная печь-плита | 1920 |

|

SU184A1 |

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| ,(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВА-ТЕЛЬ | |||

Авторы

Даты

1989-11-15—Публикация

1987-10-05—Подача