2.Устройство по п. 1, отличающееся тем, что, селектор амплитуды содержит первый и второй узлы анализа, первый элемент ИЛИ, триггер и формирователь импульсов, вход которого и входы узлов анализа являются тактовым и информационными входами селектора соответственно, выход формирователя импульсов соединен со входом триггера и является управлякяцим выходом селектора, неинвертирующий и инвертирующий выходы триггера подключены соответственно к первы управляющим входам узлов анализа, вторым и третьим управлякнцим входам второго и первого узлов анализа, выходы которых соединены с соответствующими входами первого элемента ИЛИ, выход которого является информационным выходом селектора.

3.Устройство по п. 1, о т л ичающееся тем, что узел анализа содержит первый, второй и третий ключи, элемент памяти и диференцирующий элемент, управляющий вход первого ключа, вход дифференцирующего элемента, управляющий вход третьего ключа, управляющий вход первого ключа являются управляющими с первого по третий и информационным входами узла соответственно, выход первого ключа соединен со входом элемента памяти, выход которого подключен

к информационному входу третьего ключа, выход которого является выходом узла, выход дифференцирующего элемента подключен к управляняцему входу второго ключа, выход которого соединен с информационным входом третьего ключа.,

4.Устройство по п. 1,о т л и-чающееся тем, что блок управления содержит регистр заявок, второ элемент ИЛИ, первую группу элементов И, регистр управления и функциональный преобразователь, информационные входы регистра заявок являются входами группы блока, одни входы сброса объединены с первым входом функционального преобразователя и подсоединены к первому выходу функционального преобразователя, второй выход которого подключен к одним входам элементов И первой .группы, выходы регистра заявок подключены.

к другим входам элементов И первой группы, выходы которых соединены

со входами регистра управления, выходы которого подключены к другим входам сброса регистра заявок, ко входам шифратора и ко входам элемента ИЛИ, выход которого соединен со вторым входом функционального преобразователя, третий вход которого, третий и четвертый выходы и выходы шифратора являются входом, первым и вторым выходами и выходами группы блока соответственно.

5.Устройство по п. 1, о т л и.чающееся тем, что регистр заявок содержит элементы И второй

группы, триггеры группы, выходы которых являются выходами регистра, входы установки в 1 триггеров группы, одни и другие входы элементов И являются информационными, одними и другими входами сброса регистра соответственно.

6.Устройство по п. 4, о т л ич а ю щ е ее я тем, что функциональньй преобризователь содержит третий и четвертый элементы ИЛИ, с первого по третий элементы задержки, первый и второй элементы НЕ,

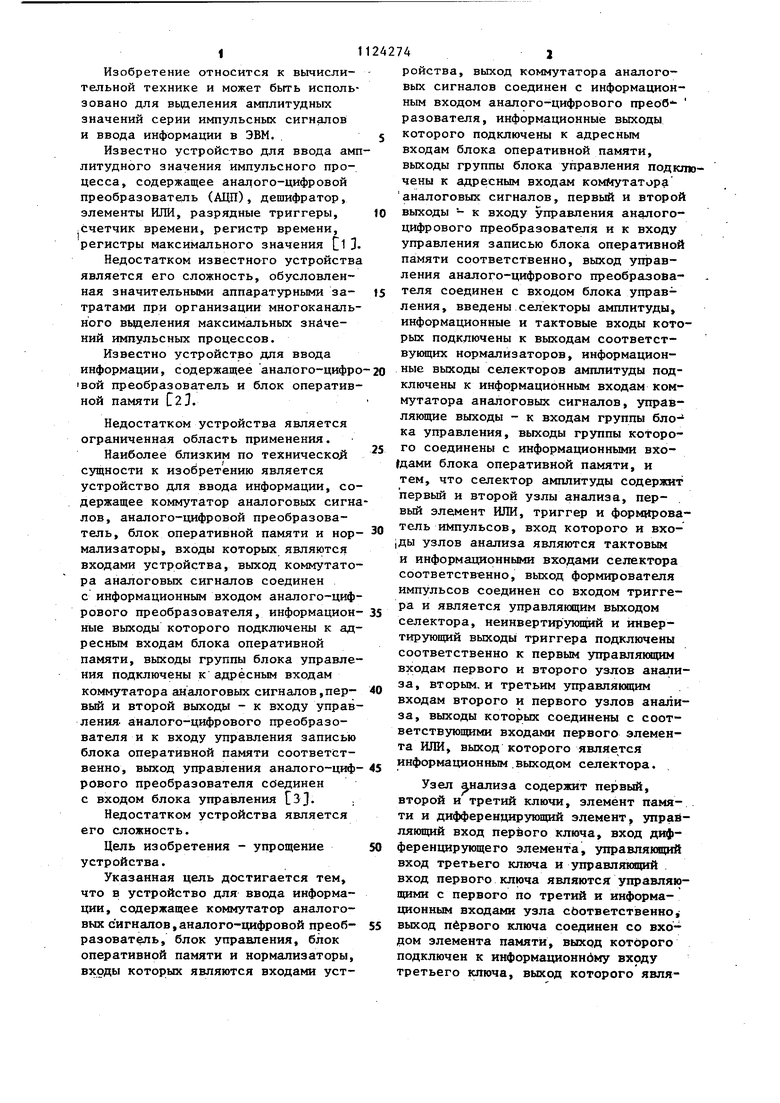

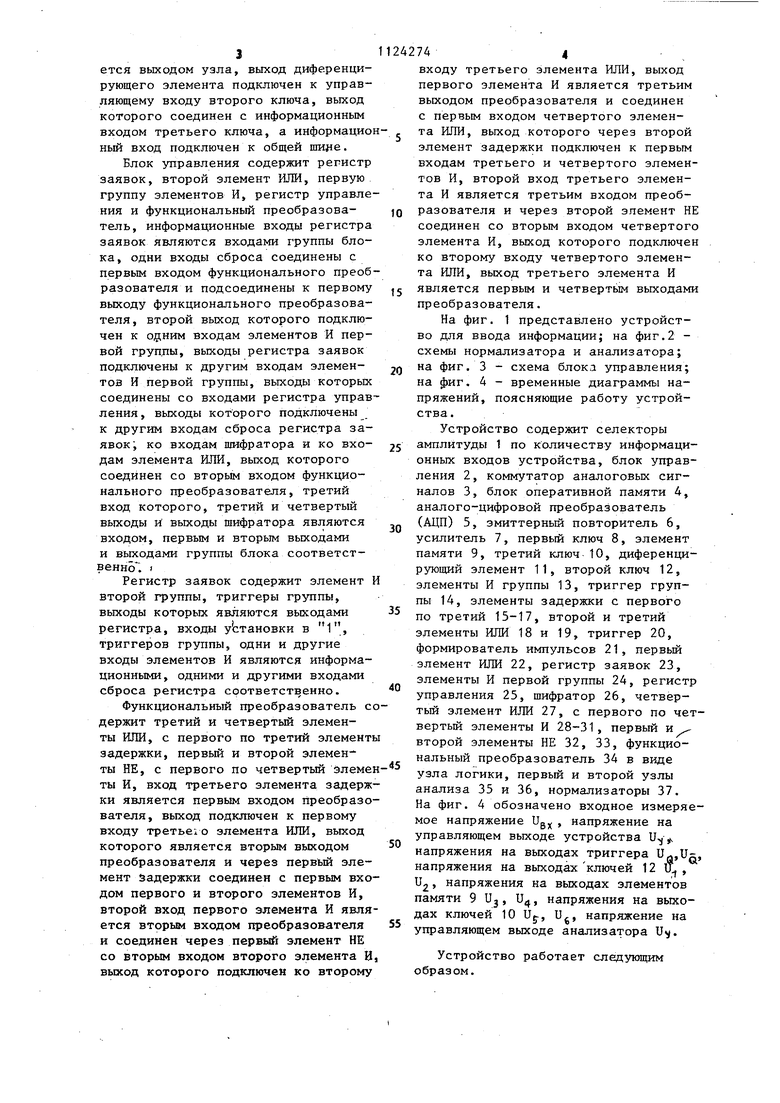

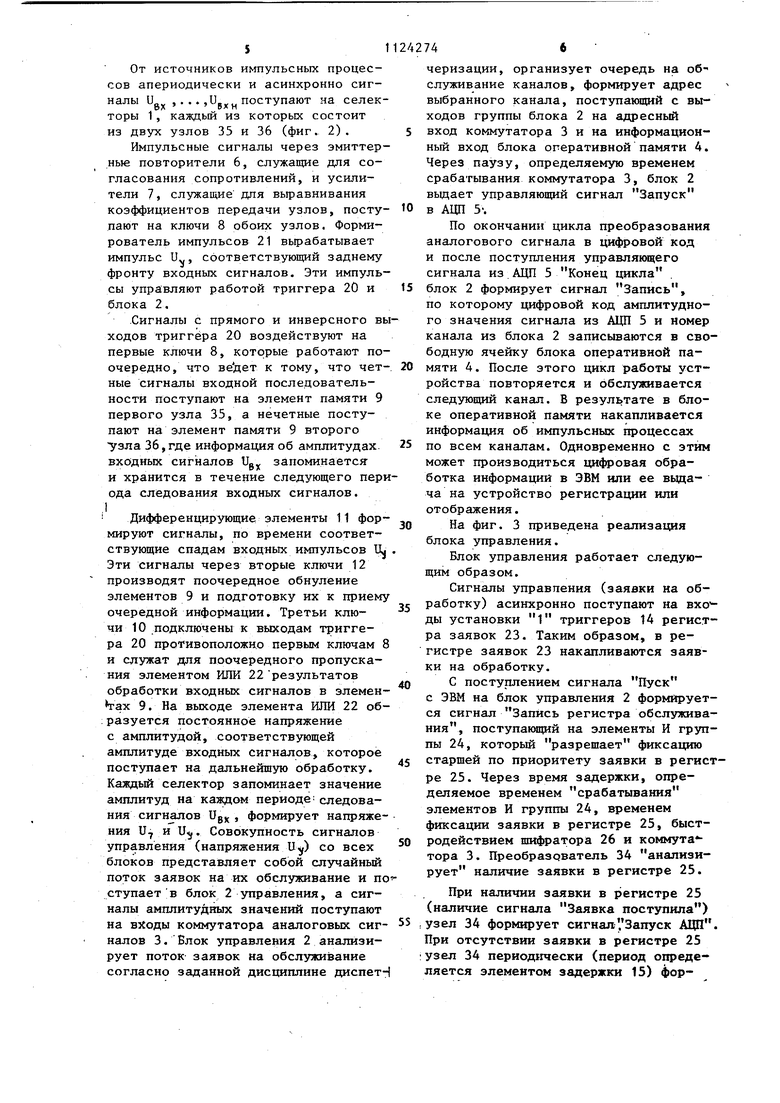

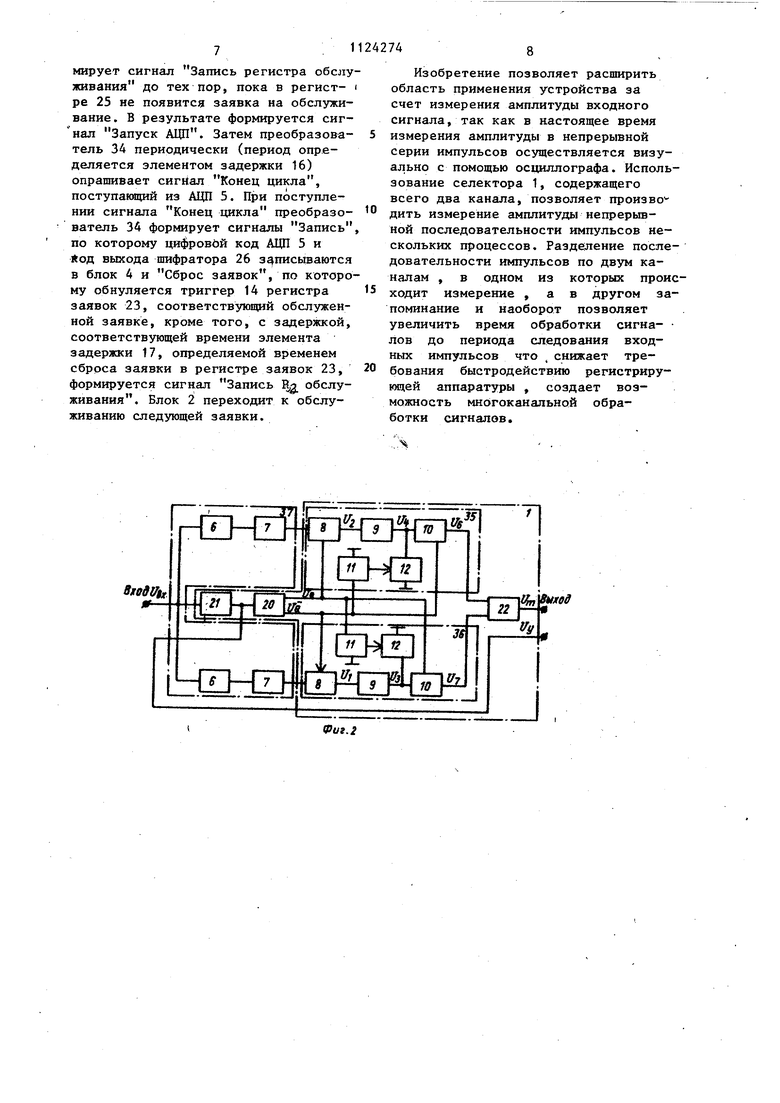

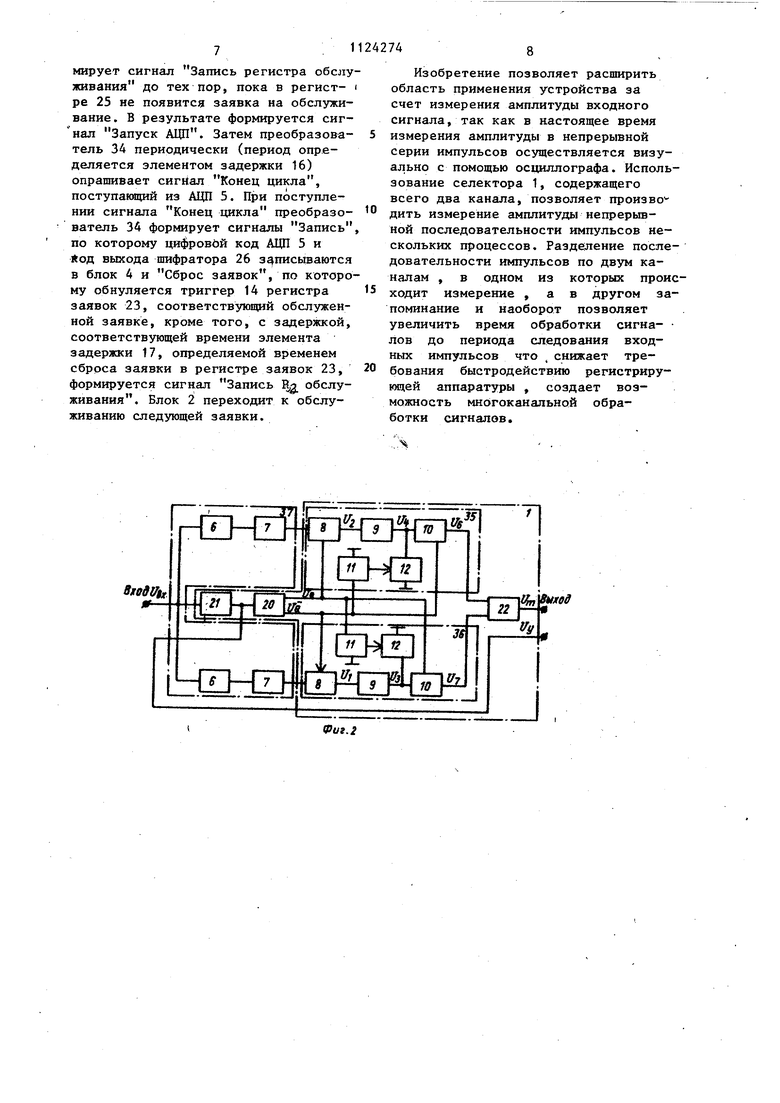

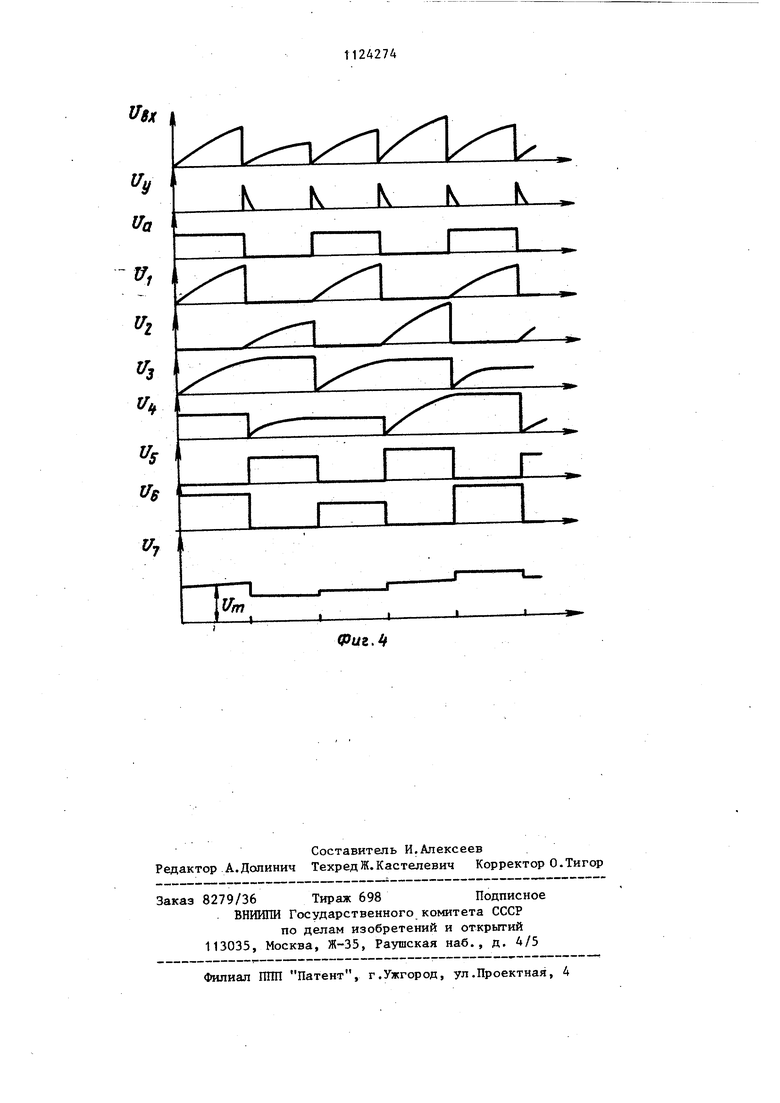

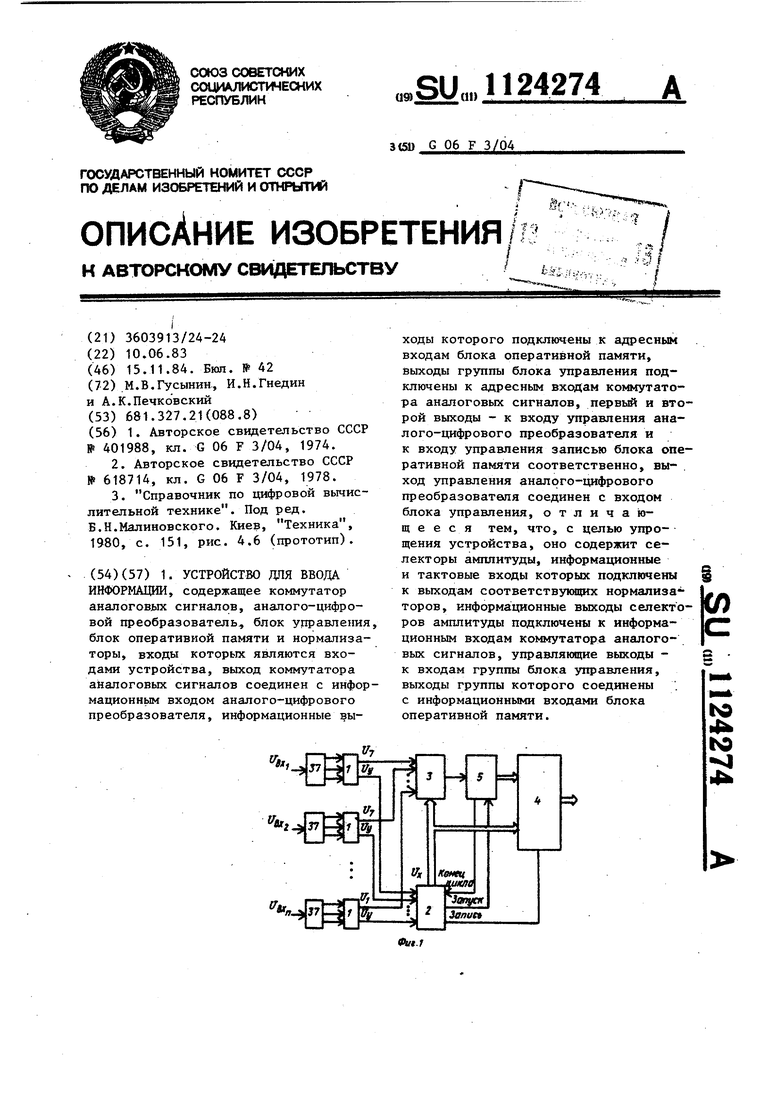

с первого по четвертый элементы И, вход третьего элемента задержки является первьм входом преобразователя, выход подключен к первому входу третьего элемента ИЖ, выход которого является вторым выходом преобразователя и через первьй элемент задержки соединен с первым входом первого и второго элементов И, второй вход первого элемента И является вторым входом преобразователя и соединен через первый элемент НЕ со вторым входом второго элемента И, выход которого подключен ко второму входу третьего элемента ИЛИ, выход первого элемента И является третьим выхоом преобразователя и соединен с первым входом четвертого элемента ИЛИ, выход которого через второй элемент задержки подключен к первым входам третьего и четвертого элементов И, второй вход третьего элемента И является третьим входом преобазователя и через второй элемент НЕ соединен со вторым входом четвертого элемента И, выход которого подключен ко второму входу четвертого йлемент-а ИЛИ, выход третьего элемента И вляется первым и четвертым выходами реобразователя.: Изобретение относится к вычислительной технике и может быть использовано для вьщеления амплитудных значений серии импульсных сигналов и ввода информации в ЭВМ. Известно устройство для ввода амп литудного значения импульсного процесса, содержащее аналого-цифровой преобразователь (АЦП), дешифратор, элементы ИЛИ, разрядные триггеры, счетчик времени, регистр времени, регистры максимального значения Cl3 Недостатком известного устройства является его сложность, обусловленная значительными аппаратурными затратами при организации многоканального ввделения максимальных знйчений имп ульсных процессов. Известно устройство для ввода информации, содержащее аналого-цифро 1ВОЙ преобразователь и блок оператив ной памяти С23. Недостатком устройства является ограниченная область применения. Наиболее близким по технической сзоцности к изобретению является устройство для ввода информации, со держащее коммутатор аналоговых сигн лов, аналого-цифровой преобразователь, блок оперативной памяти и нор мализаторы, входы которых являются входами устройства, выход коммутато ра аналоговых сигналов соединен с информационным входом аналого-циф рового преобразователя, информацион ные выходы которого подключены к ад ресным входам блока оперативной памяти, выходы группы блока управле ния подключены к адресным входам коммутатора аналоговых сигналов,первый и второй выходы - к входу управ ления- аналого-цифрового преобразователя и к входу управления записью блока оперативной памяти соответственно, выход управления аналого-циф рового преобразователя соединен с входом блока управления ГЗ. ; Недостатком устройства является его сложность. Цель изобретения - упрощение устройства. Указанная цель достигается тем, что в устройство для ввода информации, содержащее коммутатор аналоговых сигналов,аналого-цифровой преобразователь, блок управления, блок оперативной памяти и нормализаторы, входы которых являются входами уст42ройства, выход коммутатора аналоговых сигналов соединен с информационным входом аналого-цифрового прейбразователя, информационные выходы которого подключены к адресным входам блока оперативной памяти, выходы группы блока управления подключены к адресным входам коммутатора аналоговых сигналов, первый и второй выходы - к входу управления аналогоцифрового преобразователя и к входу управления записью блока оперативной памяти соответственно, выход управления аналого-цифрового преобразойателя соединен с входом блока управления, введены селекторы амплитуды, информационные и тактовые входы которых подключены к выходам соответствующих нормализаторов, информационные выходы селекторов амплитуды подключены к информационным входам коммутатора аналоговых сигналов, управляющие выходы - к входам группы блока управления, выходы группы которого соединены с информационными входами блока оперативной памяти, и тем, что селектор амплитуды содержит первый и второй узлы анализа, первый элемент ИЛИ, триггер и формкрователь импульсов, вход которого и вхоДы узлов анализа являются тактовым и информационными входами селектора соответственно, выход формирователя импульсов соединен со входом триггера и является управляющим выходом селектора, неинвертирующий и инвертирующий выходы триггера подключены соответственно к первым управляющим входам первого и второго узлов анализа, вторым, и третьим управлякяцим входам второго и первого узлов анализа, выходы которых соединены с соответствующими входами первого элемента ИЛИ, выход которого является информационным.выходом селектора. Узел анализа содержит первый, второй и третий ключи, злемент памяти и дифференцирующий элемент, управляющий вход первого ключа, вход дифференцирующего элемента, управляющий вход третьего ключа и управляющий вход первого ключа являются управляющими с первого по третий и информационным входами узла сбответственно, выход первого ключа соединен со входом элемента памяти, выход которого подключен к информационнбму входу третьего ключа, выход которого явля3ется выходом узла, выход диференцирующего элемента подключен к управляющему входу второго ключа, выход которого соединен с информационным входом третьего ключа, а информацио ный вход подключен к общей шиле. Блок управления содержит регистр заявок, второй элемент ИЛИ, первую группу элементов И, регистр управле ния и функциональный преобразователь, информационные входы регистра заявок являются входами группы блока, одни входы сброса соединены с первым входом функционального преоб разователя и подсоединены к первому выходу функционального преобразователя, второй выход которого подключен к одним входам элементов И первой группы, выходы регистра заявок подключены к другим входам элементов И первой группы, выходы которых соединены со входами регистра управ ления, выходы которого подключены к другим входам сброса регистра заявок; ко входам шифратора и ко входам элемента ИЛИ, выход которого соединен со вторьм входом функционального преобразователя, третий вход которого, третий и четвертый выходы и выходы шифратора являются входом, первым и вторым выходами и выходами группы блока соответственно. I Регистр заявок содержит элемент второй группы, триггеры группы, выходы которых являются выходами регистра, входы установки в 1, триггеров группы, одни и другие входы элементов И являются информационными, одними и другими входами сброса регистра соответственно. Функциональный преобразователь с держит третий и четвертый элементы РШИ, с первого по третий элемент задержки, первый и второй элемен ты НЕ, с первого по четвертый элеме ты И, вход третьего элемента задерж ки является первым входом преобразо вателя, виход подключен к первому входу третьего элемента ИЛИ, выход которого является вторым выходом преобразователя и через первый элемент Задержки соединен с первым вхо дом первого и второго элементов И, второй вход первого элемента И явля ется вторым входом преобразователя и соединен через первый элемент НЕ со вторым входом второго элемента И выход которого подключен ко второму 744 входу третьего элемента ИЛИ, выход первого элемента И является третьим выходом преобразователя и соединен с первым входом четвертого элемента ИЛИ, выход которого через второй элемент задержки подключен к первым входам третьего и четвертого элементов И, второй вход третьего элемента И является третьим входом преобразователя и через второй элемент НЕ соединен со вторым входом четвертого элемента И, выход которого подключен ко второму входу четвертого элемента ИЛИ, выход третьего элемента И является первым и четвертым выходами преобразователя. На фиг. 1 представлено устройство для ввода информации; на фиг.2 схемы нормализатора и анализатора; на фиг. 3 - схема блока управления; на фиг. 4 - временные диаграммы напряжений, поясняющие работу устройства. Устройство содержит селекторы амплитуды 1 по количеству информационных входов устройства, блок управления 2, коммутатор аналоговых сигналов 3, блок оперативной памяти 4, аналого-цифровой преобразователь (АЦП) 5, эмиттерный повторитель 6, усилитель 7, первый ключ 8, элемент памяти 9, третий ключ 10, диференцирующий элемент 11, второй ключ 12, элементы И группы 13, триггер группы 14, элементы задержки с первого по третий 15-17, второй и третий элементы ИЛИ 18 и 19, триггер 20, формирователь импульсов 21, первый элемент ИЛИ 22, регистр заявок 23, элементы И первой группы 24, регистр управления 25, шифратор 26, четвертый элемент ИЛИ 27, с первого по четвертый элементы И 28-31, первый к второй элементы НЕ 32, 33, функциональный преобразователь 34 в виде узла логики, первый и второй узлы анализа 35 и 36, нормализаторы 37. На фиг. 4 обозначено входное измеряемое напряжение Ug, напряжение на управляющем выходе устройства U,, напряжения на выходах триггера 1,11, напряжения на выходахключей 12 Ц, и, напряжения на выходах элементов памяти 9 Uj, и, напряжения на выходах ключей 10 Ug., и, напряжение на управляющем выходе анализатора U. Устройство работает следующим образом. $ От источников импульсных процессов апериодически и асинхронно сигналы Ugj ,,.. ,Ug поступают на селекторы 1, каждьй из которых состоит из двух узлов 35 и 36 (фиг. 2). Импульсные сигналы через эмиттерные повторители 6, служащие для согласования сопротивлений, и усилители 7, служащие для выравнивания коэффициентов передачи узлов, поступают на ключи 8 обоих узлов. Формирователь импульсов 21 вырабатывает импульс и,., соответствующий заднему фронту входных сигналов. Эти импульсы управляют работой триггера 20 и блока 2. .Сигналы с прямого и инверсного вы ходов триггера 20 воздействуют на первые ключи 8, которые работают поочередно, что ведет к тому, что четные сигналы входной последовательности поступают на элемент памяти 9 первого узла 35, а нечетные поступают на элемент памяти 9 второго узла 36, где информация об амплитудах, входных сигналов Ug запоминается и хранится в течение следующего пери ода следования входных сигналов. Дифференцирующие элементы 11 формируют сигналы, по времени соответствующие спадам входных импульсов U Эти сигналы через вторые ключи 12 производят поочередное обнуление элементов 9 и подготовку их к приему очередной информации. Третьи ключи 10 подключены к выходам триггера 20 противоположно первым ключам 8 и служат для поочередного пропускания элементом ИЛИ 22 результатов обработки входных сигналов в элементах 9. На выходе элемента ИЛИ 22 об;разуется постоянное напряжение с амплитудой, соответствующей амплитуде входных сигналов, которое поступает на дальнейшую обработку. Каждьй селектор запоминает значение амплитуд на каждом периоде следования сигналов Ugx, формирует напряжения и, и и,,. Совокупность сигналов управления (напряжения 11) со всех блоков представляет собой случайный поток заявок на их обслуживание и по ступаетв блок 2 управления, а сигналы амплитудных значений поступают на входы коммутатора аналоговых сигналов 3. Блок управления 2 анализирует поток заявок на обслуживание согласно заданной дисциплине диспет74черизации, организует очередь на обслуживание каналов, формирует адрес выбранного канала, поступающий с выходов группы блока 2 на адресный вход коммутатора 3 и на информационный вход блока оперативной памяти А. Через паузу, определяемую временем срабатывания коммутатора 3, блок 2 вьщает управляющий сигнал Запуск в АЦП 5-. По окончании цикла преобразования аналогового сигнала в цифровой код и после поступления управлякщего сигнала из АЦП 5 Конец цикла блок 2 формирует сигнал Запись, по которому цифровой код амплитудного значения сигнала из АЦП 5 и номер канала из блока 2 записываются в свободную ячейку блока оперативной памяти 4. После этого цикл работы устройства повторяется и обслуживается следующий канал. В результате в блоке оперативной памяти накапливается информация об импульсных процессах по всем каналам. Одновременно с этим может производиться цифровая обработка информации в ЭВМ или ее вьздача на устройство регистрации или отображения. На фиг. 3 приведена реализация блока управления. Блок управления работает следующим образом. Сигналы управления (заявки на обработку) асинхронно поступают на входы установки 1 триггеров 14 регистра заявок 23. Таким образом, в регистре заявок 23 накапливаются заявки на обработку. С поступлением сигнала Пуск с ЭВМ на блок управления 2 формируется сигнал Запись регистра обслуткивания, поступакяций на элементы И группы 24, который разрешает фиксацию старшей по приоритету заявки в регистре 25. Через время задержки, определяемое временем срабатывания элементов И группы 24, временем фиксации заявки в регистре 25, быстродействием шифратора 26 и коммута тора 3. Преобразователь 34 анализирует наличие заявки в регистре 25. При наличии заявки в регистре 25 (наличие сигнала Заявка поступила) узел 34 формирует сигналЗапуск АЦП. При отсутствии заявки в регистре 25 узел 34 периодически (период определяется элементом задержки 15) формирует сигнал Запись регистра обслуживания до тех пор, пока в регистре 25 не появится заявка на обслуживание. В результате формируется сигнал Запуск АЦП. Затем преобразователь 34 периодически (период определяется элементом задержки 16) опрашивает сигнал Конец цикла, поступающий из АЦП 5. поступлении сигнала Конец цикла преобразователь 34 формирует сигналы Запись по которому цифровой код АЦП 5 и Лод выхода шифратора 26 записываются в блок 4 и Сброс заявок, по которому обнуляется триггер 14 регистра заявок 23, соответствующий обслуженной заявке, кроме того, с задержкой, соответствующей времени элемента задержки 17, определяемой временем сброса заявки в регистре заявок 23, формируется сигнал Запись Ц обслуживания. Блок 2 переходит к обслуживанию следующей заявки.

Изобретение позволяет расширить область применения устройства за счет измерения амплитуды входного сигнала, так как в настоящее время измерения амплитуды в непрерывной серии импульсов ос5та1ествляется визуально с помощью осциллографа. Использование селектора 1, содержащего всего два канала, позволяет произво дить измерение амплитуды непрерывной последовательности импульсов нескольких процессов. Разделение последовательности импульсов по двум каналам , в одном из которых происходит измерение , а в другом запоминание и наоборот позволяет увеличить время обработки сигна- лов до периода следования входных импульсов что , снижает требования быстродействию регистрирующей аппаратуры , создает возможность многоканальной обработки сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006942C1 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 2007 |

|

RU2331098C1 |

| Устройство для ввода аналоговых сигналов | 1990 |

|

SU1742810A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| Устройство для считывания цветной графической информации | 1989 |

|

SU1695339A1 |

| Система телемеханики | 1982 |

|

SU1152015A1 |

1. УСТРОЙСТЮ ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее коммутатор аналоговых сигналов, аналого-цифровой преобразователь, блок управле1га блок оперативной памяти и нормализа торы, входы которых являются входами устройства, выход коммутатора аналоговых сигналов соединен с инфо мационным входом аналого-цифрового преобразователя, информационные выходы которого подключены к адресным входам блока оперативной памяти, выходы группы блока управления подключены к адресным входам коммутатора аналоговых сигналов, первый и второй выходы - к входу управления аналого-цифрового преобразователя и к входу управления записью блока оперативной памяти соответственно, выход управления аналого-цифрового преобразователя соединен с входом блока управления, отличающееся тем, что, с целью упрощения устройства, оно содержит селекторы амплитуды, информационные и тактовые входы которых подключены к выходам соответствукидих нормализа торов, кнформа:ционные выходы селекторов амплитуды подключены к информационным входам коммутатора аналоговых сигналов, управляющие выходы к входам группы блока управления, выходы группы которого соединены с информационными входами блока оперативной памяти.

Г7

fl Л

9tixed

iL.J

Жда П

г h- Пуск -TV t

и

i ш

(Pu6.3 .1 Гш ЛЛМ I ш |;g

./dх:П

X

Фиг.4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU401988A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Справочник по цифровой вычис лительной технике | |||

| Под ред | |||

| Б.Н.Малиновского | |||

| Киев, Техника, 1980, с | |||

| Двухколейная подвесная дорога | 1919 |

|

SU151A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-11-15—Публикация

1983-06-10—Подача