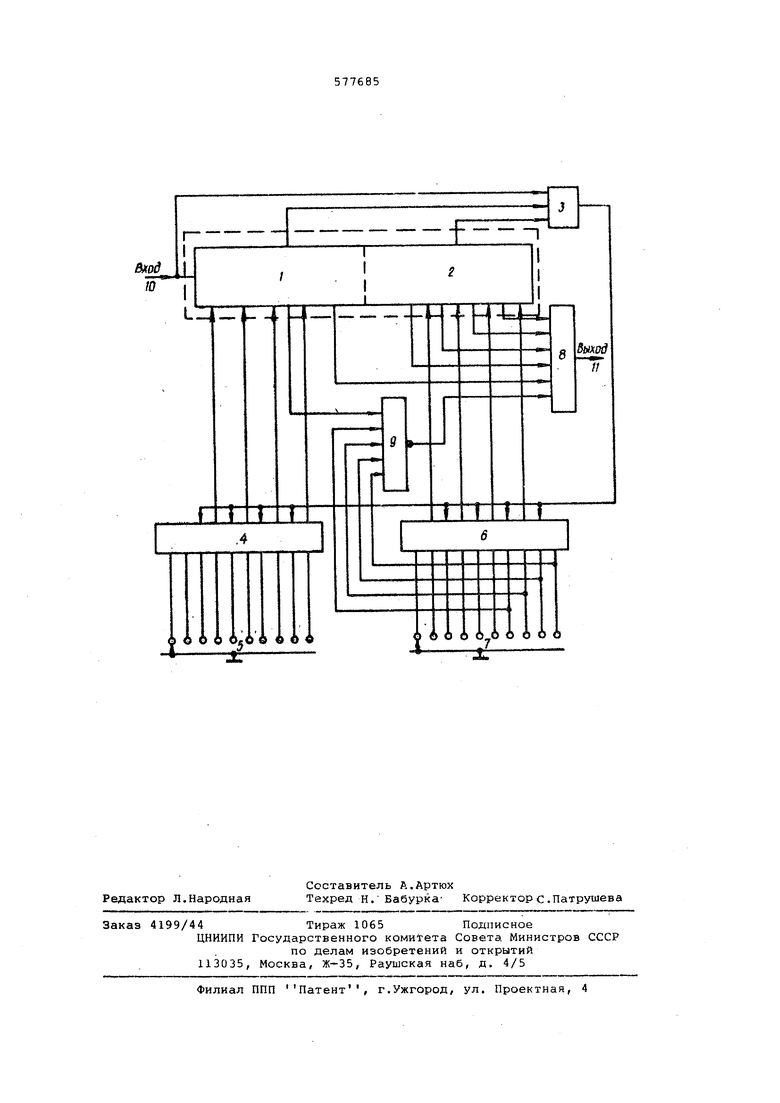

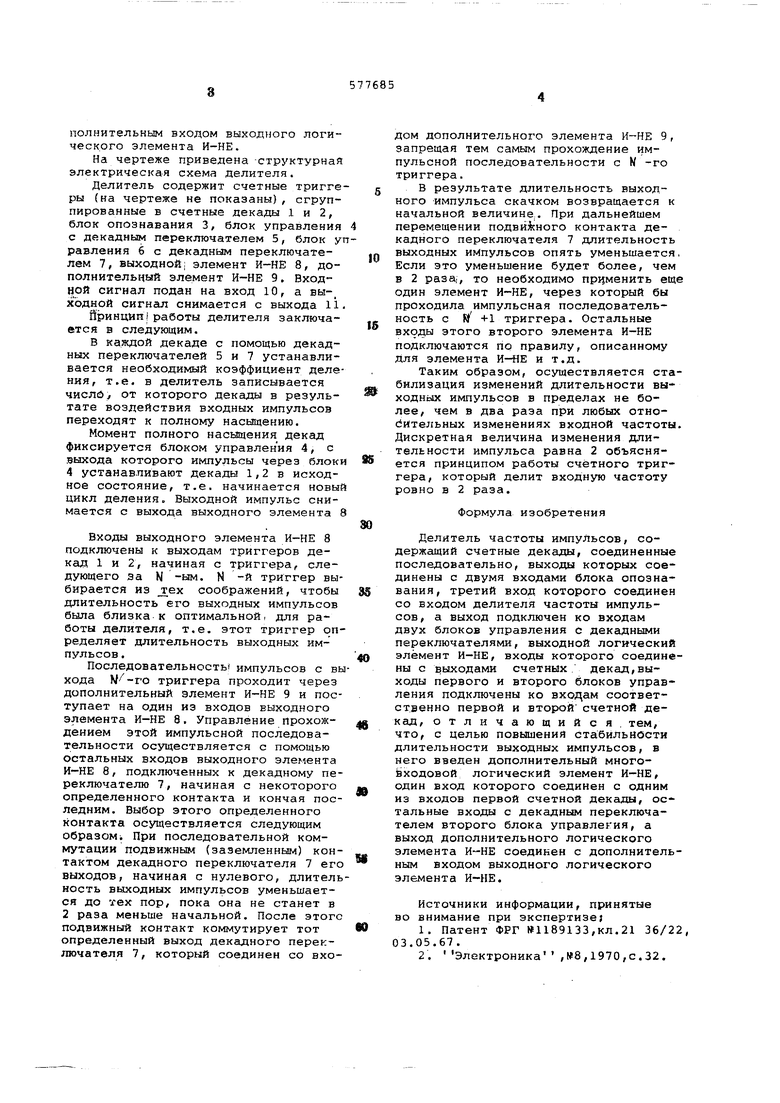

(54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ полнительным входом выходного логического элемента И-НЕ. На чертеже привалена -структурная электрическая схема делителя. Делитель содержит счетные тригге ры (на чертеже не показаны), сгруппированные в счетные декады 1 и 2, блок опознавания 3, блок управления с декадным переключателем 5, блок у равления 6 с декадным переключателем 7, выходной: элемент И-НЕ 8, дополнительный элемент И-НЕ 9. Входной сигнал подан на вход 10, а вы- ходнрй сигнал снимается с выхода 11 Йринцип работы делителя заключается в следующим. В каждой декаде с помощью декадных переключателей 5 и 7 устанавливается необходимый коэффициент деле ния, т.е. в делитель записывается числи от которого декады в результате воздействия входных импульсов переходят к полному насыщению. Момент полного насыщения декад фиксируется блоком управления 4, с выхода которого импульсы через блок 4 устанавливают декады 1,2 в исходное состояние, т.е. начинается новы цикл деления. Выходной импульс снимается о выхода выходного элемента Входы выходного элемента И-НЕ 8 подключены к выходам триггеров декад 1 и 2, начиная с триггера, следующего за N -ым. N -и триггер вы бирается из jrex соображений, чтобы длительность его выходных импульсов была близка к оптимальной, для работы делителя, т.е. этот триггер оп ределяет длительность выходных импульсов. Последовательность импульсов с вы хода Ы-ro триггера проходит через дополнительный элемент И-НЕ 9 и пос тупает на один из входов выходного элемента И-НЕ 8. Управление прохождением этой импульсной последовательности осуществляется с помощью остальных входов выходного элемента И-НЕ 8, подключенных к декадному переключателю 7, начиная с некоторого определенного контакта и кончая последним. Выбор этого определенного контакта осуществляется следующим образомi При последовательной коммутации подвижным (заземленным) контактом декадного переключателя 7 его выходов, начиная с нулевого, длитель ность выходных импульсов уменьшается до тех пор, пока она не станет в 2 раза меньше начальной. После этого подвижный контакт коммутирует тот определенный выход декадного переключателя 7, который соединен со вкодом дополнительного элемента И-НЕ 9, запрещая тем самым прохождение импульсной последовательности с N -го триггера. В результате длительность выходного импульса скачком возвращается к начальной величине. При дальнейшем перемещении подвй сного контакта декадного переключателя 7 длительность выходных импульсов опять уменьшается, Если это уменьшение будет более, чем в 2 раза,, то необходимо применить еще один элемент И-НЕ, через который бы проходила импульсная последовательность с W -1-1 триггера. Остальные входы этого второго элемента И-НЕ подключаются по правилу, описанному для элемента И-НЕ и т.д. Таким образом, осуществляется стабилизация изменений длительности выходных импульсов в пределах не более, чем в два раза при любых отнобительных изменениях входной частоты. Дискретная величина изменения длительности импульса равна 2 объясняется принципом работы счётного триггера/ который делит входную частоту ровно в 2 раза. Формула изобретения Делитель частоты импульсов, содержащий счетные декады, соединенные последовательно, выходы которых соединены с двумя входами блока опознавания, третий вход которого соединен со входом делителя частоты импульсов, а выход подключен ко входам двух блоков управления с декадными переключателями, выходной логический элемент И-НЕ, входы которого соединены с выходами счетных декад,выходы первого и второго блоков управления подключены ко входам соответственно первой и второй счетной декад, отличающийся, тем, что, с целью повышения стабильности длительности выходных импульсов, в него введен дополнительный многоёходовой логический элемент И-НЕ, один вход которого соединен с одним из входов первой счетной декады, остальные входы с декадным переключателем второго блока управления, а выход дополнительного логического элемента И-НЕ соединен с дополнительным входом выходного логического элемента И-НЕ. Источники информации, принятые во внимание при экспертизе; 1.Патент ФРГ 1189133,кл.21 36/22, 03.05.67. 2. Электроника ,№8,1970,с.32.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов | 1978 |

|

SU725242A2 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ИЗМЕНЯЕМЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1996 |

|

RU2134485C1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1117837A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Делитель частоты следования импульсов с программным управлением | 1982 |

|

SU1027831A1 |

| Делитель частоты следования импульсов | 1984 |

|

SU1181134A1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1983 |

|

SU1169170A1 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU843245A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

О О О OjcO е о о о

I

Выход

н

//

i

о о о о о о о

Авторы

Даты

1977-10-25—Публикация

1976-01-28—Подача