(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| Делитель частоты следованияиМпульСОВ C пЕРЕМЕННыМ КОэффициЕНТОМдЕлЕНия | 1979 |

|

SU834936A1 |

| Делитель частоты с переменным дробным коэффициентом деления | 1989 |

|

SU1746530A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1117837A1 |

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ИЗМЕНЯЕМЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1996 |

|

RU2134485C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Цифровой измеритель отношения временных интервалов | 1984 |

|

SU1188696A1 |

| Электронно-счетный измеритель частоты следования импульсов | 1973 |

|

SU479047A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

1

Изобретение относится к автоматике и вычислительной технике н может быть использовано в цифровых синтезаторах частоты, в делителях с переменным коэффициентом деления, работающих на высоких частотах.

Известно устройство для деления частоты следования импульсов с переменным коэффициентом деления, содержащее программируемый счетчик на А (счетчик циклов) счетчик на Р, Р + 1, счетчик на В и программируемый счетчик на N 1.

Недостаток известного устройства - значительное потребление мощности.

Наиболее близок к предлагаемому по технической сущности делитель частоты следования импульсов с переменным коэффициентом деления, содержащий п последовательно соединенных с.четных декад, блок опознования, триггер записи, счетчик циклов, триггер управления первой декадой, причем в качестве первой декады используется делитель 10/11, выход которого соединен со входом второй декады, со входом, счетчика циклов, со входом синхронизации триггера записи и триггера управления первой декадой; соответствующие выходы декад 2,...,п соединены со входами блока опознавания; выход блока опознавания соединен с информационным входом триггера записи; выход тригтера записи соединен со входом установки декад 2,...,п со входом установки счетчика циклов, входом R триггера управления первой декадой, выходы и второго разряда счетчика циклов соединены со входами схемы И-НЕ, выход которой соединен с информационным входом триггера управления первой декадой; выход триггера управления первой декадой соединен с входом управления Р первой декады 2.

Однако декады 2, 3,...,п, счетчик циклов, триггер записи, триггер управления, блрк опознавания должны быть выполнены на элементах с одинаковым быстродействием, что ведет к значительному потреблению мощности и малой загрузке схем по частоте.

Цель изобретения - уменьшение потребляемой мощности при сохранении быстродействия.

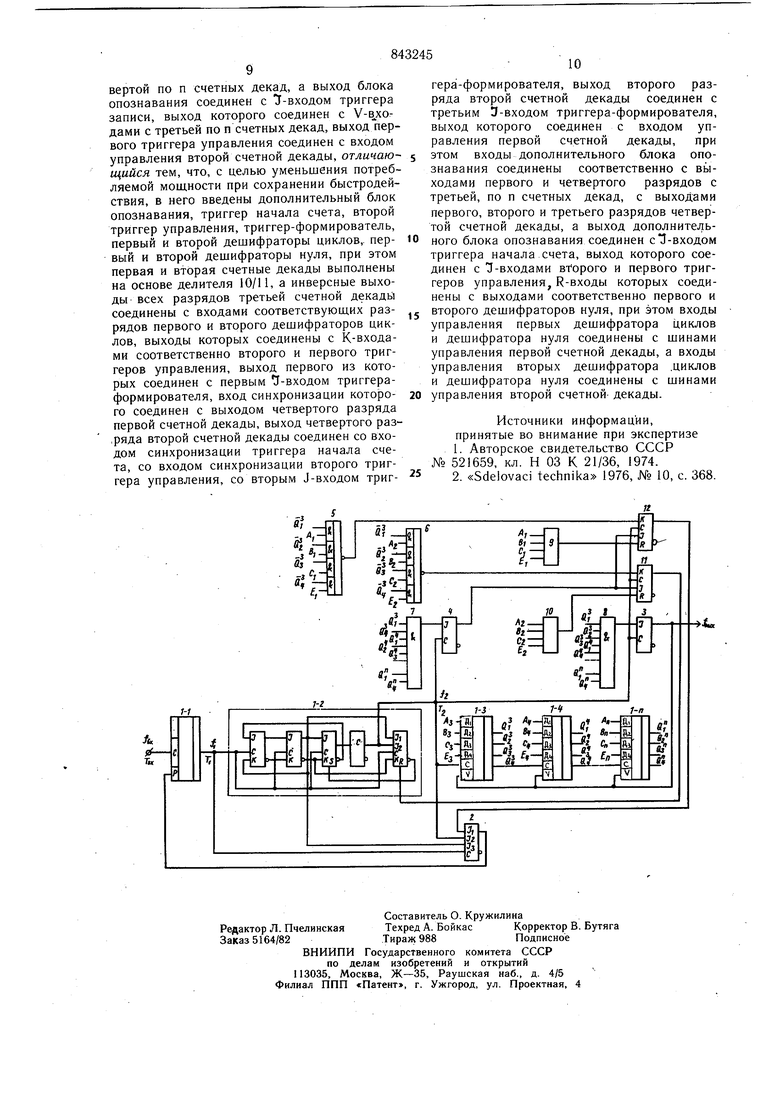

Поставленная цель достигается тем, что в делитель частоты следования импульсов с переменным коэффициентом деления, содержащий п последовательно соединенных счетных декад, триггера записи и первый триггер управления, входы синхронизации которого соединены со входами триггера записи и с выходом четвертого разряда второй счетной декады, блок опознавания, входы которого соединены с выходами первого, второго и третьего разрядов третьей с.чет.ной декады и первого и четвертого разрядов с четвертой по п счетных декад, а выход блока опознавания соединен с TJ-входом триггера записи, выход которого соединен с V-входами с третьей по п счетных декад, выход первого триггера управления соединен с входом управления второй счетной декады, введены дополнительный блок опознавания, триггер начала счета, второй триггер управления, триггер-формирователь, первый и второй дешифраторы циклов, первый и второй дешифраторы нуля, при этом первая и вторая счетные декады выполнены на основе делителя 10/11, а инверсные выходы всех разрядов третьей счетной декады соединены с входами соответствуюших разрядов первого и второго дешифраторов циклов, выходы которых соединены с К-входами соответственно второго и первого триггеров управления, выход первого из которых соединен с первым 3-входом триггера-формирователя, вход синхронизации которого соединен с выходом четвертого разряда первой счетной декады, выход четвертого разряда второй счетной декады соединен со входом синхронизации триггера начала счета, со входом синхронизации второго триггера управления, со вторым 7-входом триггера -формирователя, выход второго разряда второй счетной декады соединен с третьим Т-входом триггера-формирователя, выход которого соединен с входом управления первой счетной декады, при этом входы дополнительного блока опознавания соединены соответственно с выходами первого и четвертого разрядов с третьей по п счетных декад, с выходами первого, второго и третьего разрядов четвертой счетной декады, а выход дополнительного блока опознавания соединен с -входом триггера начала счета, выход которого соедиией с 0-входами второго и первого триггеров управления, R-входы которых соединены с выходами соответственно первого и второго дешифраторов нуля, при этом входы управления первых дешифратора циклов и дешифратора нуля соединены с шинами управления первой счетной декады, а входы управления вторых дешифратора циклов и дешифратора нуля соединены с шинами управления второй счетной декады. На чертеже представлена структурная схема устройства. Делитель содержит счетные декады 1 - 1,1-2, 1-3,...,-п, триггер-формирователь 2,триггер записи 3, триггер 4 начала счета, дешифраторы 5 и 6 циклов, блоки 7 и 8 опознавания, дешифраторы 9 и 10 нуля, и триггеры 11 и 12 управления. В качестве 8 счетных декад 1 - 1, 1-2 используются делители 10/11, третья счетная декада выполняет функции счетчика циклов, а в качестве декад 1-3,...,-п используются декады на основе двоично-десятичных счетчиков. Коэффициент деления такого устройства определяется формулой КАеА + KjlO +К.10...,-ь - коэффициент деления устройства;К.,,...,Кп-коэффициенты деления декад 1 -1,1-2,...,1-п соответственно. Коэффициент деления Kj связан с числом установки Подвыражениями K N,; K Q-Nj; K4 9-N,-, K, g-Nh, гдеЫ;.- число в двоично-десятичном коде, число N I может принимать значения О,....,9. Устройство работает следующим образом Входная последовательность импульсов с частотой и периодом Tg поступает на вход декады 1 - 1. С ее входа снимается сигнал типа Меандр с частотой следования f. или . Это позволяет без дополнительных соглашающих устройств сигнал с частотой f подать на вход декады 1-2 и на вход синхронизации триггера-формирователя 2, быстродействие которых в десять раз меньше быстродействия декады 1 - 1. С выхода декады 1-2 сигнал типа Меандр с частотой 2 -т или fj поступает на вход декадьг 1-3 на входы синхронизации триггеров 11 и 12 управления, триггера 3 записи, триггера 4 начала счета, на второй вход триггера-формирователя 2, Быстродействие декад 1-3, 1-4,..., 1-п триггеров 11 и 12 управления, триггера 3 записи, триггера 4 начала счета, дешифраторов 5 и 6 .циклов может быть в десять раз меньше быстродействия делителя 10/11. Под действием сигнала с частотой f 2.- я (делители 10/11 -имеют коэффициент деления 10) декады 1-3, 1-4,...,1-п периодически меняют свои состояния. Триггер 3 под действием импульсов, поступающих на его вход синхронизации формирует импульс записи, равный по длительности периоду Тг lOOTgjj. Импульс записи поступает на V-входы декад, 1-3, 1-4,...,1-п и записывает в них код чисел N.,N,, N соответственно. Если за период выходного сигналаделители 10/11 первой и второй счетных декад работают с коэффициентом деления 10, то общий коэффициент деления устройства будет кратным ста. Для того,чтобы получить коэффициенты деления KI и К в первой и второй декадах, отличные от нуля, необходимо, чтобы первая декада N циклов и вторая N г циклов имели коэффициент деления 11. Коэффициенты деления декад 1 - 1, 1-2 определяются управляющими сигналами, которые поступают на входы дешифраторов 5 и 6 циклов и дешифраторов 9 и 10 нулей. Количество циклов N., и NjC коэффициентом деления 11 для декад I - 1, 1-2 численно равно коэффициентам деления этих декад. Подсчет циклов с коэффициентом деления 11 как первой, так и второй декад осуществляет третья декада. Поскольку третья декада импульсом записи может быгь установлена в любое состояние от 0000 до 1001 в зависимости от коэффициент Kj, то переключение первых двух декад на счет с коэффициентом деления 11, а следовательно, и подсчет циклов осуществляются только после того, как с выхода третьей декады поступит по крайней мере один импульс переноса на вход декады I-4. Это необходимо для того, чтобы счет циклов начинался всегда с одного и того же состояния декады 1-3. Кроме того, для правильной и надежной работы устройства необходимо разнести во времени момент записи кодов чисел Nj, Ni,... декады 1-3, 1-4,...,1-п и момент начала счета циклов. На выходе блока опознавания 7 появляется логическая единица, когда декады 1-3, 1-4,...,1-п находятся в состонии 1001, 0111, 1001,...,1001 соответственно. Логическая единица с выхода блока опознавания 7 поступает на З-вход триггера 4 начала счета. Нулевым импульсом триггер 4 начала счета устанавливается в единичное состояние, декада 1-3 в состояние 0000. Логическая единица .с выхода триггера 4 поступает на -входы триггеров И и 12 управления. Первым импульсом триггер 4 устанавливается в нулевое состояние, декада 1-3 в состояние 1000, триггеры И и 12 в единичное состояние при условии, что на выходах дешифраторов 9 и 10 нуля присутствуют логические единицы. Логические единицы на выходах дешифраторов 9 и 10 присутствуют, если коэффициенты деления К., К2 отличны от нуля. Рассмотрим случай, когда К| О, Кд N. Для получения коэффициента деления К2 во второй декаде необходимо,чтобы вторая декада N циклов делила с коэффициентом деления 11. Тогда переключается только триггер 11 управления, поскольку триггер 12 управления заблокирован нулевым сигналом, который поступает с выхода дешифратора 9 нуля на R-вход триггера 12. С выхода триггера 11 управления логическая единица поступает на вход управления декады 1-2, давая тем самым разрешение на переключение ее на счет с К И. Поскольку триггер 11 переключается выходным сигналом декады 1-2,,а переключение декады 1-2 с одного коэффициента на другой происходит восьмым входным импульсом этой декады, то максимальное время tf, на переключение декады 1-2 с одного коэффициента на другой определяется выражениемt 7,5Т, Т., 10.Т. Задержка распространения t.cигнaлa переключения на вход управления второй декады относительно входного сигнала декады 1-2 определяется 1г„ ti+ -ri+T где г ti задержки распространения сигнала в декаде 1-2; f и- задержка переключения триггера И. Для нормальной работы необходимо, чтобы .Тьх Поскольку быстродействие декады 1-2 на порядок выше быстродействия триггера 11 управления, а триггер И переключается синхронно выходным сигналом декады I-2, то условие Т легко выполнимо. Декада 1-3 ведет подсчет циклов с коэффициентом деления М. Так как подсчет циклов начинается с момента, когда декада 1 - 3 находится в состоянии 1000, то при поступлении 1 цикла на вход декады I-3 на выходе дешифратора 6 циклов появляется логическая единица, которая поступает на К-вход триггера И управления. При поступлении еще одного цикла триггер 11 опрокидывается в нулевое состояние. Логический нуль с выхода триггера 11 управления поступает на вход управления второй декады и дает разрешение на переключение ее на счет с коэффициентом 10. В дальнейшем вторая декада имеет коэффициент деления 10 до завершения полного цикла счета. Таким образом, за период выходного сигнала устройства рторая декада N разделит с коэффициентом 11. Рассмотрим случай, когда Kj N|, N На выходе дешифраторов 9 и 10 присутствуют логические единицы, и триггеры 11 и 12 управления устанавливаются в единичное состояние. Логическая единица с выхода триггера 11 поступает на вход управления второй декады и дает разрешение на переключение ее на счет с коэффициентом деления 11. Логическая единица с выхода триггера 12 поступает на Т,-вход триггераформирователя 2. Последовательность импульсов с частотой f| поступает на вход второй декады и периодически меняет состояние этой декады. Седьмым импульсом декада 1-2 устанавливается в состояние 1101. При этом на К-входах триггера формирователя 2 присутствуют логические единицы. Восьмым импульсом триггер-формирователь 2 устанавливается в единичное состояние. Логическая единица с выхода триггера-формирователя 2 поступает на вход управления первой декады и дает разрешение на переключение ее на счет с коэффициентом деления 11. Время на переключение декады 1 - 1 с одного коэффициента на другой определяется как tf 7,5-Tg, и, следовательно, задержка переключения тг не должна превышать величины tf ,5-Твх .+ Г.уг , Т| -задержка сигнала в декаде 1 - 1; задержка переключения триггераформирователя 2; Tgj(- период входного сигнала первой декады. После поступления одиннадцати импульсов с частотой вход первой декады с выхода ее снимается импульс, который переводит триггер-формирователь 2 в нулевое состояние. Логический нуль с выхода триггера-формирователя 2 поступает на вход управления декады 1 - 1 и дает разрешение на переключение ее на счет с коэффициентом деления 10. Таким образом, за период выходного сигнала триггер-формирователь 2 N( раз дает разрешающий сигнал на вход управления декады 1 - 1 и декада 1 - 1 N, раз делит с коэффициентом деления И. После поступления N, - 1 цикла на вход декады 1-3 на К-входе триггера управления 12 появляется логическая единица. При поступлении еще одного цикла триггер 12 опрокидывается в нулевое состояние. Логиче кий нуль с выхода триггера 12 поступает на J| -вход триггера-формирователя 2 и запрещает переключать его в единичное состояние до завершения полного цикла счета. После поступления N цикла в нулевое состояние опрокидывается триггер 11. Логический нуль поступает на вход управления декады 1-2 и дает разрешение на переключение декады 1-2 на счет К Ю. В дальнейшем вторая декада, как и первая делит с К 10 до завершения полного цикла счета далее процесс повторяется.

В известном устройстве быстродействие первой декады, а следовательно, и быстродействие всего устройства повышено за счет применения в качестве первой декады делителя 10/11. Однако входной сигнал декады 1 -2 может иметь частоту десять и более мегагерц, что требует применения схем высокого быстродействия. Поскольку быстродействие декад 1-2, 1-3...1-п, счетчика циклов, триггера записи должно быть одинаково, то это приводит к значительному потреблению мощности и малой загрузке схем по частоте.

Формула изобретения

Делитель частоты следования импульсов с переменным коэффициентом деления, содержащий п-последовательно соединенных счетных декад, триггер записи и первый триггер управления, входы синхронизации которого соединены со входами триггера записи и с входом четвертого разряда второй счетной декады, блок опознавания, входы которого соединены с выходами первого, второго и третьего разрядов третьей счетной декады и первого и четвертого разрядов с четВ предлагаемом устройстве в качестве первых декад используются делители 10/11, выходной сигнал которых представляет собой Меандр. Это позволяет без дополнительных согласующих элементов соединить выход декады 1 - 1 со входом декады 1-2 и выход декады 1-2 со входом декады 1-3. При этом требование к быстродействию декады 1-2 снижено в десять раз,а декады 1-3, триггеров И и 12 управления и триггера начала счета, триггера записи в сто раз по сравнению с первой декадой. Делители 10/11 весь цикл работают в режиме счета с коэффициентом 10 или 11, что позволяет исключить цикл установки для первых двух декад, заменив его переключением делителей 10/11 с одного коэффициента деления на другой. Максимально допустимое время на переключение делителей с одного крэффициента на другой определяется т г it, 7,5.Т, вх | -максимально допустимое время переключения делителя с одного коэффициента на другой; -период входного сигнала данного делителя 10/11; - максимальная частота на входе делителя 10/11. Для правильной работы делителя необходимо, чтобы задержка распространения trц сигнала переключения не превышала максимально допустимого времени на переключения tt,,T.e. . Выполнение данного условия позволяет реализовать быстродействие делителя, 10/11 в составе устройства, равное быстродействию отдельно взятого делителя 10/11. Поскольку быстродействие отдельно взятого делителя 10/11 равно быстродействию триггера, то и быстродействие делителя 10/11 в составе устройства равно быстродействию отдельно взятого триггера. Таким образом, в устройстве используется минимальное количество элементов с высоким быстродействием, что значительно снижает потребляемую мощность устройства, сохранив быстродействие равное быстродействию триггера первой декады.

вертой по п счетных декад, а выход блока опознавания соединен с 7Г-входом триггера записи, выход которого соединен с V-в ходами с третьей по п счетных декад, выход первого триггера управления соединен с входом управления второй счетной декады, отличающийся тем, что, с целью уменьшения потребляемой мощности при сохранении быстродействия, в него введены дополнительный блок опознавания, триггер начала счета, второй триггер управления, триггер-формирователь, первый и второй дешифраторы циклов,, первый и второй дешифраторы нуля, при этом первая и вторая счетные декады выполнены на основе делителя 10/11, а инверсные выходы всех разрядов третьей счетной декады соединены с входами соответствующих разрядов первого и второго дешифраторов циклов, выходы которых соединены с К-входами соответственно второго и первого триггеров управления, выход первого из которых соединен с первым -входом триггераформирователя, вход синхронизации которого соединен с выходом четвертого разряда первой счетной декады, выход четвертого раз.ряда второй счетной декады соединен со входом синхронизации триггера начала счета, со входом синхронизации второго триггера управления, со вторым J-входом триг/fe nfГи

гера-формирователя, выход второго разряда второй счетной декады соединен с третьим D-входом триггера-формирователя, выход которого соединен с входом управления первой счетной декады, при

этом входы дополнительного блока опознавания соединены соответственно с выходами первого и четвертого разрядов с третьей, по п счетных декад, с выходами первого, второго и третьего разрядов четвертой счетной декады, а выход дополнительного блока опознавания соединен сТ-входом триггера начала счета, выход которого соединен с 3-входами Btoporo и первого триггеров управления, R-входы которых соединены с выходами соответственно первого и

второго дешифраторов нуля, при этом входы управления первых дешифратора циклов и дешифратора нуля соединены с шинами управления первой счетной декады, а входы управления вторых дешифратора .циклов и дешифратора нуля соединены с шинами

управления второй счетной- декады.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 521659, кл. Н 03 К 21/36, 1974. 2. «Sdelovaci technika 1976, № 10, с. 368.

Авторы

Даты

1981-06-30—Публикация

1979-05-07—Подача