декады счетчика импульсов и вторым входом элемента запрета, а второй выход - с первым входом элемента И, второй вход которого подключен к шине управления,а выход к первому входу элемента ИЛИ, в то рой вход которого соединен с выходом э: емента запрета, а выходс входом Делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь цифрового кода в частоту следования импульсов | 1980 |

|

SU869543A1 |

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Преобразователь интервала времени в цифровой код | 1983 |

|

SU1166310A1 |

| Преобразователь частоты в код | 1977 |

|

SU746922A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1117837A1 |

| Преобразователь код-временной интервал | 1986 |

|

SU1361721A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий регистр памяти, входы которого подключены к соответствующим шинам входного -кода, основной блок сравнения кодов, выЛолненный на А, декадных элементах сравнения, генератор импульсов, делитель частоты, выход которого соединен с выходной шиной. Счетчик импульсов, выполненный на /ь декадах, выход переноса каждой из которых, кроме младшей и старшей, подключен к счетному входу соответствующей последующей декады, а информационные выходы декад подключены в обратном порядке к первым входам соответствующих декадных элементов сравнения блока сравнения кодов, вторые входы которых подключены к соответствующим выходам регистра памяти, вход разрешения записи которого соединен с выходом переноса старшей декады счетчика импульсов, и элемент запрета, первый вход которого соединен с выходом старшего декадного элемента сравнения блока сравнения кодов, третий вход каждо%..-. ГЗ f ... Cf/ ---. / го декадного элемента сравнения которого, кроме младшего, соединен с выходом соответствующего предшествующего декадного элемента сравнения блока сравнения кодов, а третий вход младшего декадного элемента сравнения - с шиной установки логической 1, отличающийся тем, что, с целью расширения функциональных возможностей преобразователя, в него введены блок разделения импульсов, формирователь импульсов, элемент И, элемент ИЛИ и дополнительный блок сравнения кодов, выполненный на Л/декадных элементах сравнения, пер(О вые входы которых подключена к первым входам соответствующих декадных элементов сравнения основного блока сравнения кодов, вторые входы соединены с соответствующими дополнительными шинами входного кода, третий вход каждого, кроме младшего, соединен с выходом соответствующего предшествующего декадного элемента сравнения дополнительного блока сравнеО ния кодов, а третий вход младшего десо кадного элемента сравнения дополнительного -блока сравнения кодов подключен к шине установки логической 1 при этом выход старшего декадного элемента сравнения дополнительного блока сравнения кодов соединен с входом формирователя импульсов, выход которого соединен с входом сброса младшей декады и счетным входом второй декады счетчика импульсов, причем выход генератора импульсов соединен с входом блока разделения импульсов, первый выход которого соединен со счетным входом младшей

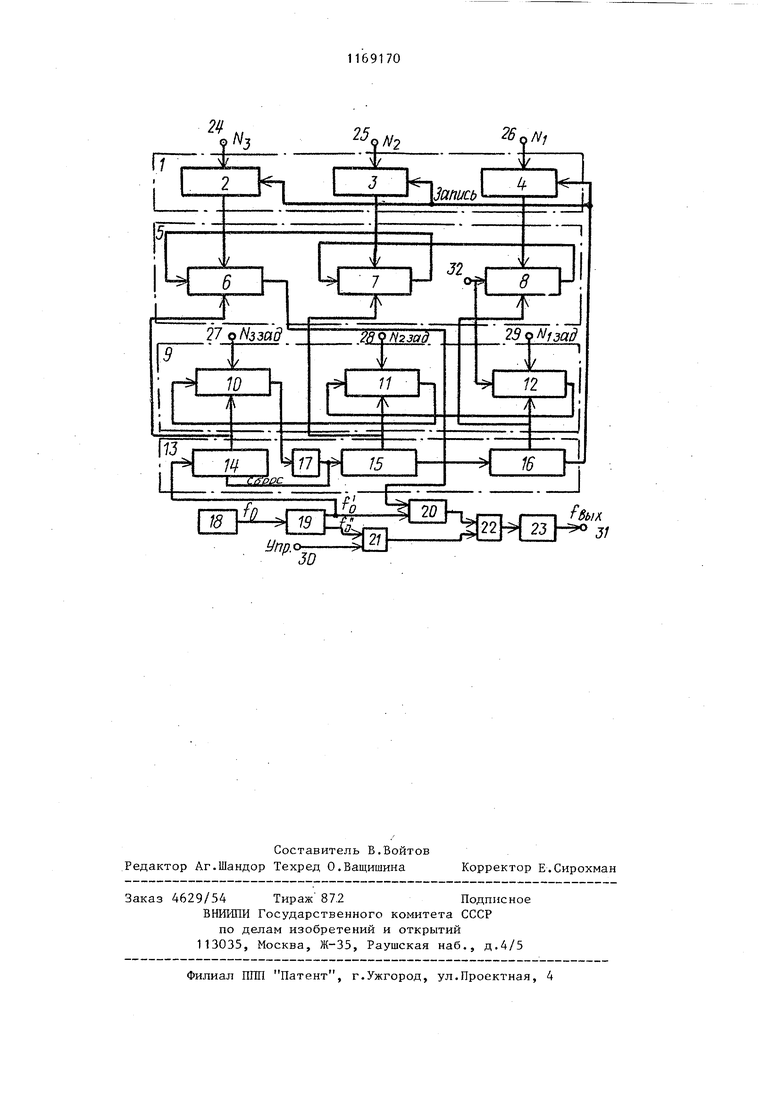

Изобретение относится к импульсной технике и может быть использовано, в частности в качестве выходного узла различных систем цифрового управления автоматики. Цель изобретения - расширение функциональных возможностей преобразователя . На чертеже изображена структурная электрическая схема преобразователя (для случая преобразования трехразрядного двоично-десятичного кода). Преобразователь содержит регистр 1 памяти, предназначенный для .хранения в двоично-десятичных ячейках 2-4 преобразуемого кода, блок 5 сравнения кодов, декадные элементы 6-8 сравнения которого выполнены, например, на элементах 2-2-2И-ЗИЛИ, допол нительный блок 9 сравнения кодов, состоящий из трех декадных элементов 10-12 сравнения, счетчик 13 импульсов, вьтолненный на трех декадах 14-16, формирователь 17 цмпульсов, генератор 18 импульсов, блок 19 разделения импульсов, элемент 20 запрета, элемент И 21, элемент ИЛИ 22, делитель 23 частоты, шины 24-26 вход ного кода, дополнительные шины 27-29 входного кода, шину 30 управления, выходную шину 31 и шину 32 установки логической 1. Преобразуемый трехразрядный двоично-десятичный код ,- 210 ,10 подается по шинам 24-26 на вход регистра 1 памяти, с выхода которого обратньш код подается на вторые входы блока 5 сравнения кодов, на первые входы которого подается код со счетчика 13 импульсов в обрат ном порядке (т.е. декады регистра 1 памяти и счетчика 13 импульсов подключены к блоку 5 сравнения кодов в обратном порядке). Обратный код с ко дового задатчика (, V10+N,0 10° по дополнительным шинам 27-29 входного кода подается на входы дополнительного блока 9 сравнения кодов аналогично основному блоку 5 сравнения кодов. При этом выход переноса декады 15 счетчика 13 импульсов подключен к счетному входу декады 16, выход переноса которой соединен с входом разрешения записи регистра 1 памяти, первый выход элемента 20 запрета соединен с выходом старшего декадного элемента 6 сравнения блока 5, третьи входы декадных элементов 6 и 7 сравнения соединены соответственно с выходами элементов 7 и 8, а третий вход элемента 8 - с шиной 32 установки логической 1. Третьи входы декадных элементов 10 и 11 сравнения дополнительного блока 9 сравнения кодов соединены соответственно с выходами элементов 11 и 12, а третий вход элемента 12 - с шиной 32 установки логической 1. Выход старшего декадного элемента 10 сравнения дополнительного блока 9 сравнения кодов соединен с входом формирователя 17 импульсов, выход которого соединен с входом сброса младшей декады 14 и со счетным входом декады 15 счетчика 13 импульсов. Выход генератора 18 импульсов соединен с входом блока 19 разделения импульсов, первый выход которого соединен со счетным входом младшей декады 14 счетчика 13 и вторым входом элемента 20 запрета, а второй выход - с первым входом элемента И 21, второй вход которого подключен к шине 30 управления, а выход - к первому входу элемента ИЛИ 22, второй вход которого соединен с выходом элемента 20 запрета, а выход - с входом делителя 23 частоты, выход которого соединен с выходной шиной 31. 3 Кажд,ая декада блока сравнения кодов работает следующим- образом. Если код Ng на первом входе любой, из декад блока сравнения кодов меньше кода Ыд на ее втором входе,. то на выходе этой декады действует сигнал логического О. Появление логической 1 на выходе декады зависит от величины сигнала на ее тре тьем входе. Если на третьем входе декады действует сигнал логического О, то логическая 1 появится на выходе этой декады при NO N.+1. Еели на третьем входе этой декады действует сигнал логической 1, то на ее выходе логическая 1 появится при Ng Нд. Элемент 20 запрета пропускает импульсы эталонной частоты f , если с выхода старшей декады блока 5 сравнения кодов на ее вход поступает логический О, и не пропускает импуль сы частоты f , если на выходе действует сигнал логической 1. Блок 19 разделения импульсов предназначен для формирования двух импульсных последовательностей, частоты которых равны по абсолютной величине частоте эталонного генератора /Ед/ и импульсы в которых сдвинуты один относительно другого на полпериода. Преобразователь работает следующим образом. В исходном состоянии код в счетчике 13 импульсов равен нулю. По мере поступления импульсов эталонной частоты fg на счетн ш вход младшей декады 14 счетчика 13 импульсов код в последней начинает нарастать. При увеличении кода в младшей декаде 14 счетчика импул|зсов до значения (N553 +1) на выходе старшего декадного эле мента 10 сравнения дополнительного блока 9 сравнения кодов появится сиг нал логической 1, по фронту которо го формирователь 17 импульсов сформирует импульс, поступающий на счетный вход второй декады 15 счетчика 13 импульсов и на вход сброса младшей декады 14 счетчика 13 импульсов, код в которой снова начинает нарастать от О до (N5331 + 1). Так будет про должаться до тех пор, пока код в средней декаде 15 счетчика 13 импуль сов не достигнет значения (Nj,;, +1), т.е. пока не появится логическая 1 на третьем входе старшего декадного элемента 10 сравнения дополнительно70. 4 го блока 9 сравнения кодов. этого сброс младшей декады 14 счетчика 13 импульсов происходит при достижении кодом этой декады величины N,,. . С приходом десятого импульса на счетный вход второй декады 15 счетчика 13 импульсов код в последней станет равным нулю, ка выходе второго декадного элемента 11 сравнения дополнительного блока 9 сравнения кодов появится логический О, и код в младшей декаде 14 счетчика 13 импульсов вновь нарастает от О ДО (заА Таким образом можно проследить работу младшей декады 14 счетчика 13 импульсов до его обнуления, т.е. до момента появления импульса переноса на выходе старшей декады 16 счетчика 13 импульсов. После этого все повторяется сначала. Промежуток времени Т между двумя импульсами переноса на выходе счетчика 13 импульсов представляет собой один цикл (период) преобразования. Длительность цикла преобразования определяется кодом, подаваемым на вход дополнительного блока 9 сравнения кодов с кодового задатчика по шинам 27-29 Т N Т ъол S где TO - период следования импульсов эталонной частоты, т.е. в промежуток времени от одного импульса переноса на выходе счетчика импульсов до другого на счетный вход этого счетчика поступает N,(Jд число импульсов эталонной частоты. Причем нужное количество импульсов обеспечивается благодаря управляемому сбросу первой декады 14 счетчика 13 импульсов. Управление сбросом осуществляется в результате поразрядного анализа кода в счетчике 13 импульсов и кода, поступающего с кодового задатчика. Вследствие этого младшая декада 14 счетчика 13 импульсов считает до (Nj,3,+1) или до Njjg. Результат поразрядного анализа кода, поступающего с кодового задатчика, определяетя выражением аА lX,)(N2,)+N,,,10(N2,c,)N,,,+(N, -f1)-N +N, V 00-N.,)(10-N,,). ) Таким образом, изменяя можно зменять время цикла преобразования.

Преобразование кода N в частоту следования импульсов заключается в пропускании через элемент 20 запрета за один цикл преобразования количества импульсов, равного величине преобразуемого кода N. Управление элементом 20 запрета осуществляется сигналами с выхода старшего декадного элемента 6 сравнения блока 5 сравнения кодов.

В начале каждого цикла преобразования код в счетчике 13 импульсов равен нулю. Если преобразуемый код не равен нулю (N,, , ), то на выходе всех декадных элементов срав11е шя блока 5 сравнения кодов действует сигнал логического О, который с выхода старшей декады 6 блока 5 сравнения кодов разрешает прохождение импульсов эталонной частоты f на выход элемента 20 згшрета. По мере поступления импульсов эталонной частоты (5 на вход младшей декады 14 счетчика 13 импульсов код в по следней начинает увеличиваться, и пр достижении им величины () на выходе старшего декадного элемента 6 сравнения блока 5 сравнения кодов появится сигнал логической 1 и будет запрещено прохождение импульсов эталонной частоты через элемент 20, т.е. за один просчет младшей декады 14 счетчика 13 импульсов на выход элмента 20 запрета пройдет (Nj+l) импульса. После сброса младшей декады 14 счетчика 13 импульсов на выходе старшей декады 6 появится сигнал логического О и вновь будет разрешено прохождение импульсов эталонной частоты f через элемент 20 запрета.

Таким образом, элемент 20 запрета будет пропускать пачки по () импульса, пока код во второй декаде 15 счетчика 13 импульсов не достигнет величины (. После этого на третьем входе старшего декадного элемента 6 сравнения блока 5 сравнения кодов появится сигнал логической 1 и через элемент 20 будут проходить пачки по N, импульса. Т.е. в зависимости от состояния предыдущих декад 7 и 8 старшая декада 6 блока 5 сравнения кодов таким образом управляет элементом 20 запрета, что через него проходят пачки по (Nj+1) или по Nj импульсов. Причем общее количество

импульсов, проходяш;ее за один цикл через элемент 20 запрета, равно по величине преобразуемому коду. Импульсом переноса счетчика 13 импульсов осуществляется запись преобразуемого кода в регистр 1 памяти и цикл преобразования повторяется. Порядок чередования пачек по () и по Nj импульсов представляет собой результат поразрядного анализа преобразуемого и текущего кодов в счетчике 13 импульсов и определяется выражением

(N + 1)(N2 + 1)(N,i+1)N, + + (N,+1)N2+N -.-NjdO-Np (10-N, ) (3)

Например, при преобразовании кода выражение (3) принимает вид N(36+2- 4).7.+ (3-5+2-5), т.е. через элемент 20 за один цикл преобразования сначала пройдут 6 пачек по 3 импульсов, затем 4 пачки по 2 импульса, и такое распределение повторится 7 раз. После этого пройдут 5 пачек по 3 импульса и 5 пачек по 2 импульса, такое распределение повторится 3 раза. В следунщем цикле преобразования для кода порядок расстановки импульсов точно такой же

Использование принципа поразрядного анализа позволяет равномерно распределить импульсы эталонной частоты f по всему периоду преобразования. На выход преобразователя эти импульсы поступают через делитель 23 эталонной частоты, применение которого позволяет улучшить расстановку импульсов выходной последовательности во времени.

Если на шине 30 управления действует сигнал логического О, то на вход делителя 23 эталонной частоты через элемент ИЛИ 22 проходят только импульсы с выхода элемента 20 запрета.

Частота на выходе преобразователя равна

г N N

9Ь1Х т. К Т . N К Ч о зад

где К - коэффициент деления делителя эталонной частоты; N - величина преобразуемого тока Если на шине управления элемента И 21 действует логическая 1, то импульсы частоты f через элемент И 21 и элемент ЙИ 22 начинают поступать на делитель 23 эталонной

7

частоты. В этом случае частота на вьсходе преобразиват€шя равна

f f о. + еых к

нотак как )f;;/ jf | /fj, то выражение (5) можно представить в следующем виде:

f fo ГЦ.

W-r видно из выражения (6), при величине преобразуемого кода

2f 5аА вых К

где д,(с максимально возможная частота на выходе преобразователя, т.е. все импульсы эталонной частоты проходят на делитель 23 эталонной частоты, и при кодах , на выход преобразователя будет поступать частота макс

Коэффициент деления К делителя эталонной частоты выбирают исходя из заданнойf Qi j. :

f,

4OVC

К

2f

1169170

У известного преобразователя частота изменяется от О до f, , причем

М U k С

значение f(j,aicc соответствует фиксированному коду (для случая преобразования трехразрядиого двоичнодесятичного кода).

У предлагаемого преобразователя выходная частота может изменяться как от О до fj.,,,,, так и от - ,о

Макс

0 „

-махе

Кроме того, в предлагаемом преобразователе максимальную выходную частоту можно получить при любом требуемом значении преобразуемого кода. Для этого .код N.. устанавливают

равным такой величине преобразуемого кода, при котором требуется получение максимальной частоты на выходе преобразователя.

0

Например, если | 1МГц, , N,,750 и на шине 30 управления дейW,

ствует логическая 1, то при-изменении преобразуемого кода от О до J 750 fj, будет изменяться от 4000 Гц до 8000 Гц. При .значениях преобразуемого кода 750 г N 999 выходная частота преобразователг также будет равна 8000 Гц.

| ГЕНЕРАТОР ИМПУЛЬСОВ С УПРАВЛЯЕМОЙ ЧАСТОТОЙ1 | 0 |

|

SU371673A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1980 |

|

SU869543A1 |

| Н 0.3 К 13/20, 10.04.80. | |||

Авторы

Даты

1985-07-23—Публикация

1983-05-03—Подача