Изобретение относится к импульсной технике и может быть использовано в различных цифровых устройствах.

Известен делитель частоты с изменяемым коэффициентом деления (см. книгу Горн Л.С., Хазанов Б.И. Схемотехника радиометров, М.: Атомиздат, 1977, стр. 213, рис. 49), содержащий счетчик, формирователь разностной последовательности импульсов, переключатели в количестве, равном количеству разрядов счетчика, элемент И и инвертор. Выход элемента И соединен через инвертор со входом обратной связи формирователя разностной последовательности импульсов, вход которого соединен со входной шиной, выход - со входом счетчика, выходы импульсных выходов разрядов которого через соответствующие переключатели соединены со входами элемента И.

Недостатком делителя является сложность схемной реализации, обусловленная необходимостью выполнения триггеров разрядов счетчика с дополнительными импульсными выходами, использования переключателей по количеству разрядов счетчика и привязки всех входов многовходового элемента И через соответствующие резисторы к шине питания.

Известен делитель частоты с изменяемым коэффициентом деления (см. авт. свид. СССР N 783996 от 11.01.79, МКИ: H 03 K 21/36, "Делитель частоты с изменяемым коэффициентом деления", автор Ю.В.Смирнов, опубл. в БИ N 44, 1980 г. ), который является прототипом и содержит счетчик импульсов в виде декадного счетчика и дешифраторы по числу счетных декад счетчика, узел сброса счетчика, коммутатор в виде декадного переключателя, каждая декада которого подключена к выходам соответствующего дешифратора, входы которого соединены с выходами соответствующей счетной декады счетчика. Входы сброса счетных декад счетчика соединены с выходом узла сброса декадного счетчика, вход первой счетной декады счетчика подключен к входу устройства. Узел сброса декадного счетчика содержит элемент И и элемент запрета, выход которого является выходом данного узла, запрещающий вход подключен к входу устройства, а управляющий вход - к выходу элемента И. Входы элемента И соединены с подвижными контактами декадного переключателя, а выход является выходом устройства.

Недостатками данного делителя частоты являются:

1) ограниченность функциональных возможностей, обусловленная отсутствием возможности одновременного использования полного объема счетчика (например, для деления частоты на максимально возможный для счетчика коэффициент) при установке декадным переключателем конкретного (не равного максимальному) значения коэффициента деления, поскольку счетчик принудительно возвращается в исходное нулевое состояние, не досчитав до переполнения;

2) сложность, обусловленная сложностью схем дешифраторов из-за необходимости дешифрации всех состояний счетчика для обеспечения возможности выбора всех возможных для него коэффициентов деления.

Задачей, решаемой предлагаемым техническим решением, является расширение функциональных возможностей делителя частоты путем обеспечения возможности одновременного использования полного объема счетчика при установке конкретного (не максимального) значения коэффициента деления и упрощение его путем упрощения схемы дешифрации всех его состояний.

Указанный технический результат достигается тем, что в делитель частоты с изменяемым коэффициентом деления, содержащий счетчик импульсов, счетный вход которого соединен с входной шиной, а выходы разрядов соединены с соответствующими входами дешифратора, выходы которого соединены с соответствующими входами коммутатора, и элемент И, выход которого соединен с выходной шиной, введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с шиной управления, второй вход - с выходом коммутатора, выход - с первым входом элемента И, второй вход которого соединен со входной шиной.

Указанная совокупность признаков позволяет расширить функциональные возможности делителя частоты путем обеспечения возможности работы его счетчика без принудительного обнуления, то есть в полном объеме с максимальным коэффициентом деления, в процессе деления частоты с выбранным значением коэффициентa деления и упростить его в целом путем упрощения схемы дешифрации всех состояний счетчика за счет изменения режима дешифрации состояний счетчика с помощью управляющего сигнала.

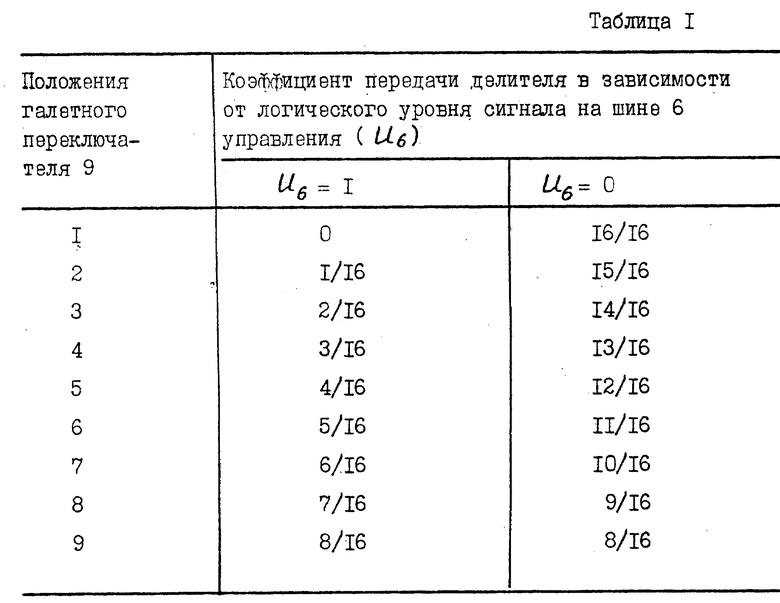

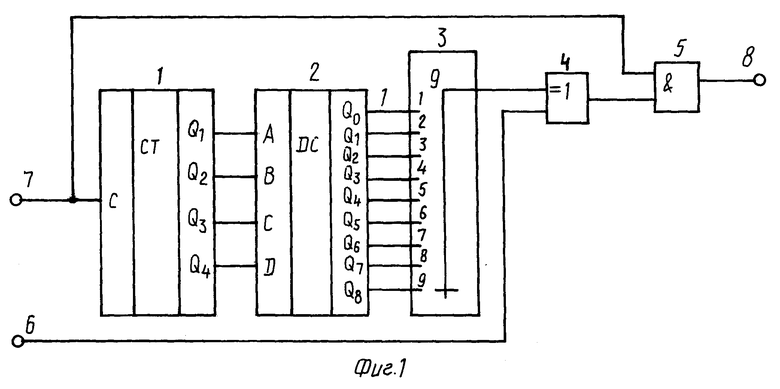

На фиг.1 приведена схема делителя частоты с изменяемым коэффициентом деления, выполненного на базе двоичного четырехразрядного счетчика; на фиг. 2 - схема варианта реализации дешифратора для случая использования в делителе указанного типа счетчика.

Делитель частоты содержит счетчик 1 импульсов, дешифратор 2, коммутатор 3, элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент 5 И. Входы дешифратора 2 подключены к выходам соответствующих разрядов счетчика 1, выходы соединены с соответствующими входами коммутатора 3, выход которого соединен со вторым входом элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с шиной 6 управления, а выход - с первым входом элемента 5 И. Второй вход элемента 5 И соединен со счетным входом счетчика 5 и с входной 7 шиной, а выход - с выходной 8 шиной.

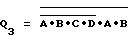

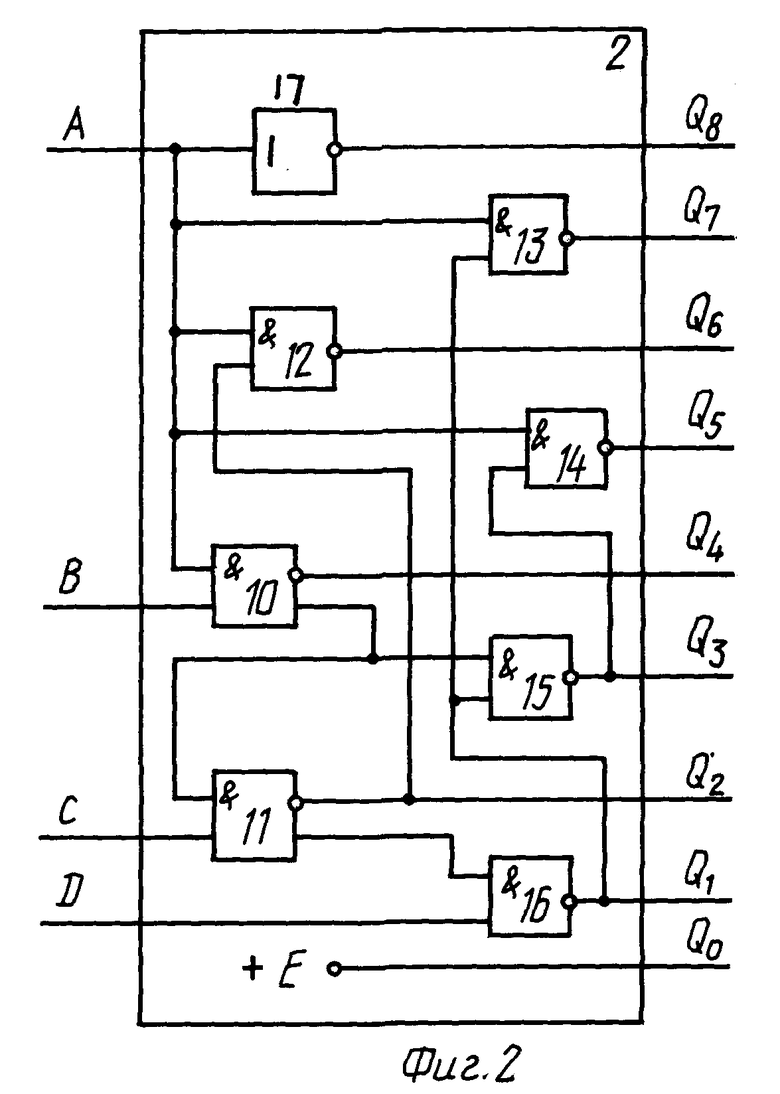

Схема дешифратора 2 зависит от типа используемого счетчика 1, в рассматриваемом случае он выполнен по схеме, приведенной на фиг.2, на элементах 10, 11 И с прямым и инверсным выходами, на элементах 12-16 И и инверторе 17. Логические функции, выполняемые дешифратором, 2 следующие:

Q0 = 1 -

-

-

-

-

-

-

Коммутатор 3 выполнен на галетном переключателе, может быть выполнен в виде электронного коммутатора.

Все функциональные элементы устройства могут быть реализованы на базе типовых логических элементов интегральных микросхем, например серий 564, 1564, 1533.

Делитель частоты с изменяемым коэффициентом деления работает следующим образом.

В исходном состоянии на входной 7 шине поддерживается уровень логического нуля (счетных импульсов нет), счетчик 1 находится в исходном нулевом состоянии (вход сброса счетчика 1 на фиг.1 не показан). Уровень логического нуля, поступающий со входной 7 шины на второй вход элемента 5 И, поддерживает на его выходе уровень логического нуля, независимо от уровня сигнала на первом входе. Поэтому на входах элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ могут быть любые сочетания уровней сигналов, следовательно, в исходном состоянии переключатель 9 коммутатора 3 может находиться в любом из положений, а на шине 6 управления может поддерживаться любой из двух логических уровней.

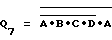

Рассмотрим работу делителя при установке конкретного коэффициента деления (коэффициента передачи), выбор которого осуществляется установкой переключателя 9 коммутатора 3 в нужное положение и подачей по шине 6 управления соответствующего сигнала (логического уровня). Состояния уровней сигнала на шине 6 управления и положения переключателя 9 коммутатора 3 для всех возможных значений коэффициента деления (коэффициента передачи) делителя при использовании в нем четырехразрядного двоичного счетчика 1, показанного на фиг. 1, приведены в таблице.

Допустим, что переключатель 9 коммутатора 3 установлен в положение 5, на шину 6 управления подан уровень логической единицы, а счетчик 1 переключается по фронту (по положительному перепаду) счетных импульсов.

При подаче по входной 7 шине счетных импульсов начинается их подсчет. Поскольку переключатель 9 коммутатора 3 установлен в положение 5, то в состояниях счетчика, соответствующих числам 3, 7, 11 и 15, на выходе коммутатора 3 появляется (в соответствии с выражением  ) уровень логического нуля, который поступает на второй вход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, на первом входе которого имеется уровень логической единицы. Поэтому на выходе элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ в указанных состояниях счетчика появляется уровень логической единицы, открывающий элемент 5 И по второму входу, на первый вход которого поступают счетные импульсы по входной 7 шине. В результате на выход элемента 5 И проходят третий, седьмой, одиннадцатый и пятнадцатый счетные импульсы, то есть четыре импульса из шестнадцати поступивших на счетный вход счетчика 1 до его обнуления (переполнения). При поступлении последующих импульсов указанный процесс выделения четырех импульсов из каждых шестнадцати циклически повторяется, то есть в рассматриваемом случае коэффициент передачи импульсов на выходную 8 шину равен 4/16 (коэффициент деления делителя равен четырем).

) уровень логического нуля, который поступает на второй вход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, на первом входе которого имеется уровень логической единицы. Поэтому на выходе элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ в указанных состояниях счетчика появляется уровень логической единицы, открывающий элемент 5 И по второму входу, на первый вход которого поступают счетные импульсы по входной 7 шине. В результате на выход элемента 5 И проходят третий, седьмой, одиннадцатый и пятнадцатый счетные импульсы, то есть четыре импульса из шестнадцати поступивших на счетный вход счетчика 1 до его обнуления (переполнения). При поступлении последующих импульсов указанный процесс выделения четырех импульсов из каждых шестнадцати циклически повторяется, то есть в рассматриваемом случае коэффициент передачи импульсов на выходную 8 шину равен 4/16 (коэффициент деления делителя равен четырем).

Если при выбранном положении (пятом) переключателя 9 коммутатора 3 на шину 6 управления подать уровень логического нуля, то уровень логической единицы на выходе элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ будет появляться во всех остальных состояниях счетчика 1, кроме указанных четырех, то есть на выход делителя пройдут двенадцать импульсов из каждых шестнадцати (коэффициент деления - 1,33).

При установке переключателя 9 коммутатора 3 в положение 9 уровень логического нуля на выходе коммутатора 3 будет появляться в нечетных состояниях счетчика (так как  ), поэтому при логической единице на шине 6 управления на выходе элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ уровень логической единицы будет появляться при нечетных состояниях счетчика 1 и через элемент 5 И на выходную 8 шину будут проходить нечетные счетные импульсы, то есть коэффициент передачи импульсов на выходную 8 шину равен 8/16 (коэффициент деления равен двум). При логическом нуле на шине 6 управления коэффициент деления делителя в рассматриваемом случае также будет равен двум, только на выходную 8 шину через элемент 5 И будут пропускаться все четные счетные импульсы.

), поэтому при логической единице на шине 6 управления на выходе элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ уровень логической единицы будет появляться при нечетных состояниях счетчика 1 и через элемент 5 И на выходную 8 шину будут проходить нечетные счетные импульсы, то есть коэффициент передачи импульсов на выходную 8 шину равен 8/16 (коэффициент деления равен двум). При логическом нуле на шине 6 управления коэффициент деления делителя в рассматриваемом случае также будет равен двум, только на выходную 8 шину через элемент 5 И будут пропускаться все четные счетные импульсы.

Аналогично работает делитель при других сочетаниях положений переключателя 9 и логических уровней сигнала на шине 6 управления (см. таблицу), то есть при выборе других возможных коэффициентов деления. При этом счетчик 1 делителя работает без принудительного сброса в исходное нулевое состояние, то есть в полном объеме, поэтому в процессе работы делителя с конкретным выбранным коэффициентом деления счетчик 1 может одновременно использоваться для деления счетных импульсов на максимальный для этого счетчика коэффициент деления (в данном случае - для деления на 16). При этом сигнал снимается с выхода старшего разряда счетчика 1.

При переключении счетчика 1 по срезу (по отрицательному перепаду) счетных импульсов делитель работает аналогично, только при этом на выход элемента 5 И пропускаются импульсы, следующие за импульсами, по срезу которых счетчик 1 переключается в состояния, выделяемые переключателем 9 и логическим уровнем сигнала на шине 6 управления.

Таким образом, предлагаемый делитель частоты с изменяемым коэффициентом деления может работать с любым возможным для счетчика 1 коэффициентом деления, при этом длительность выходных импульсов делителя равна длительности счетных импульсов, а необходимый коэффициент деления устанавливается с помощью коммутатора 3 и уровнем сигнала на шине 6 управления. Одновременно при выбранном коэффициенте деления делитель может применяться для деления частоты поступающих счетных импульсов на максимальный для счетчика 1 коэффициент деления (в нашем случае это 16, при этом снимается с выхода старшего разряда счетчика 1) или даже на некоторые другие коэффициенты деления (в нашем случае это 8, 4, 2) при снятии выходных сигналов с выходов других разрядов счетчика 1, поскольку счетчик 1 в процессе работы не сбрасывается принудительно в исходное нулевое состояние. В последних случаях длительность выходных сигналов делителя, снимаемых с выходов его разрядов, зависит от точки снятия сигнала, а скважность их равна двум.

Преимуществами заявляемого делителя частоты с изменяемым коэффициентом деления перед прототипом являются:

1) более широкие функциональные возможности, обусловленные возможностью одновременного использования делителя для деления с коэффициентом деления, устанавливаемым с помощью коммутатора 3, и уровнем сигнала на шине 6 управления, и с максимальным для счетчика 1 коэффициентом деления;

2) более простая схема, обусловленная в основном более простой схемой дешифрации всех состояний счетчика 1, достигнутой использованием элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ и шины 6 управления.

В целях подтверждения осуществимости заявляемого объекта и достигнутого технического результата в институте построен и испытан в диапазоне температур от минус 50 до плюс 50oC лабораторный макет, выполненный по схеме фиг. 1 на базе интегральных микросхем серии 564 и галетном переключателе типа ПГ2. Проведенные испытания показали осуществимость заявляемого делителя частоты с изменяемым коэффициентом деления и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| РЕЛЕ ВРЕМЕНИ | 1997 |

|

RU2119245C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1995 |

|

RU2106057C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1995 |

|

RU2102833C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

| ЭЛЕКТРОННЫЙ КОДОВЫЙ ЗАМОК | 2001 |

|

RU2187612C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

Изобретение относится к импульсной технике и может быть использовано в различных цифровых устройствах. Достигаемый технический результат - расширение функциональных возможностей и упрощение. Делитель частоты с изменяемым коэффициентом деления содержит счетчик 1 импульсов, дешифратор 2, коммутатор 3, элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент 5 И, шину 6 управления, входную 7 и выходную 8 шины. Технический результат достигнут введением элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, шины 6 управления и новых связей между функциональными элементами. 1 табл., 2 ил.

Делитель частоты с изменяемым коэффициентом деления, содержащий счетчик импульсов, счетный вход которого соединен с входной шиной, а выходы разрядов соединены с соответствующими входами дешифратора, выходы которого соединены с соответствующими входами коммутатора, и элемент И, выход которого соединен с выходной шиной, отличающийся тем, что в него введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с шиной управления, второй вход - с выходом коммутатора, выход - с первым входом элемента И, второй вход которого соединен с входной шиной.

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

| Делитель частоты следования им-пульСОВ C пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU839065A1 |

| Делитель частоты импульсов с регулируемым коэффициентом деления | 1981 |

|

SU978357A1 |

Авторы

Даты

1999-08-10—Публикация

1996-03-11—Подача