1

Изобретение относится к технике коммутации импульсных каналов.

По основному авт. св. № 434610 известио устройство временной асинхрониой коммутации импульсных сигналов, содержащее оперативный запоминающий блок, два выхода которого через дещифраторы подключены к управляющим входам электронных контактов п входных канальиых комплектов и к управляющим входам m выходных канальиых комплектов соответствеино, а между выходами электронных контактов входных канальных комплектов и входами оперативного запоминающего блока включены последовательно соединенные групповой компаратор, блок управления и блок смеиы временных каналов, дополнительный вход которого соединен с входами дешифраторов.

Однако известное устройство сложно, TdK как в нем количество ячеек памяти для хранения управляющих слов должно превышать количество коммутируемых каналов.

Цель изобретения - упрощение устройства путем уменьшения емкости запоминающего блока.

Для этого в устройство временной асинхронной коммутации импульсных сигналов, содержащее оперативный запоминающий блок, два выхода которого через дешифраторы подключены к управляю1цим входам электронных контактов п входных канальиых комплектов и к

управляющим входам m выходных канальных комплектов соответственно, а между выходами электронных контактов входных канальных комплектов и входами оперативного запоминающего блока включены последовательно соединенные групповой компаратор, блок управления и блок смены временных каналов, дополнительНый вход которого соединен с входами дёшнфраторов, введены ячейка памяти оперативного запомииающего блока, блок выдержки времени и блок распределеиия времеиных каналов, причем выход блока выдержки времени соединен с входом блока распределения временных каналов, выход которого подключен к первому входу ячейки памяти оперативного запомииающего блока, второй вход которой соединен с входом блока выдержки времени и с дополнительным входом блока смены временных каналов.

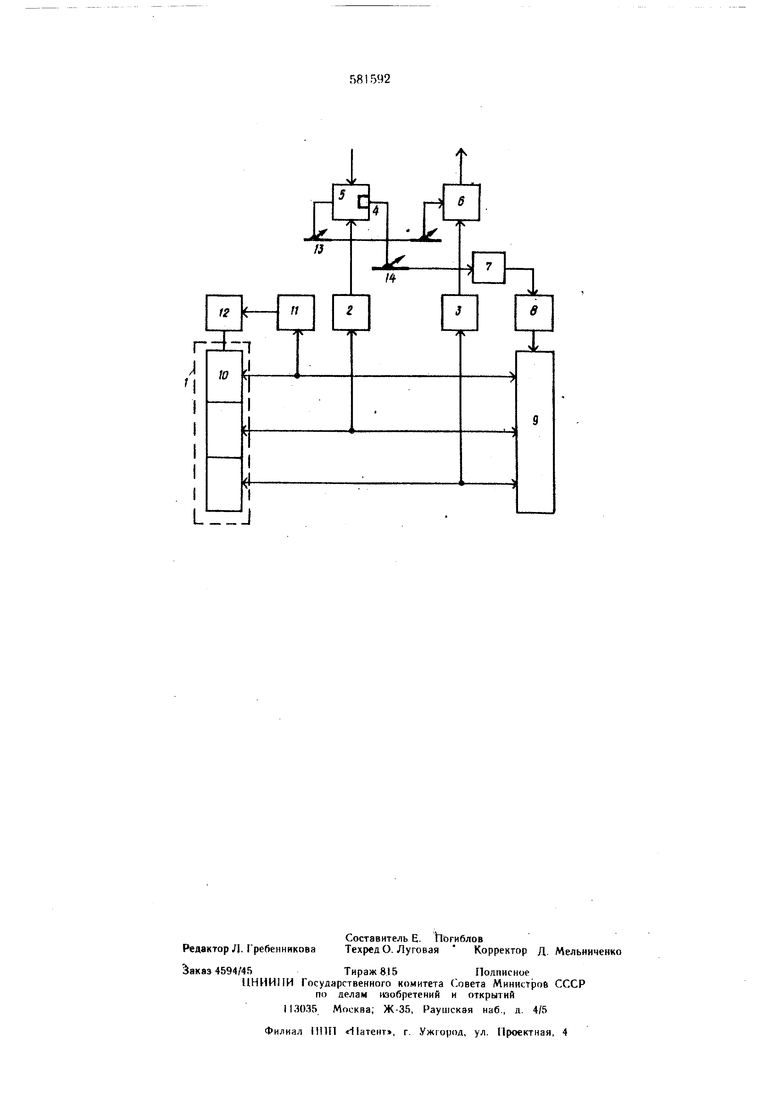

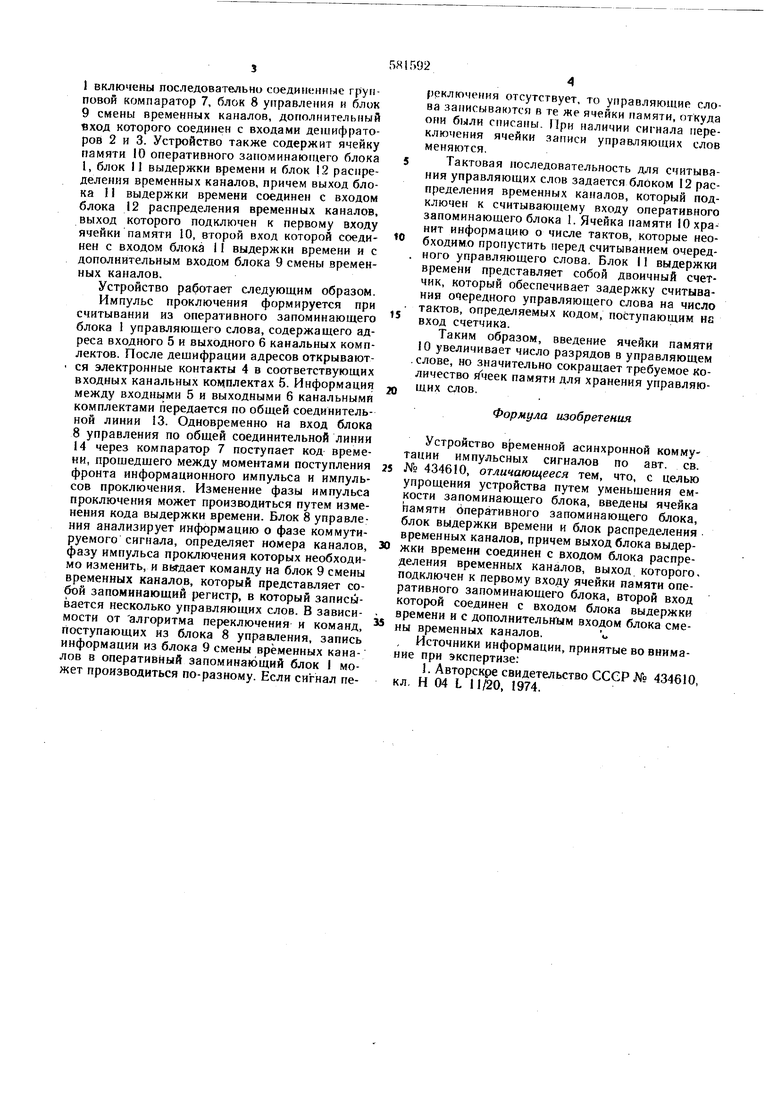

На чертеже дана структурная электрическая схема предлагаемого устройства.

Устройство содержит оператнвиый запоминающий блок 1, два выхода которого через дешифраторы 2 и 3 подключены к управляющим входам электронных контактов 4 входных канальных комплектов 5 и к управляющим входам выходных канальных комплектов 6 соответственно, а между выходами электроиных контактов 4 входных канальных комплектов 5 и входами оперативного запоминающе, о блока 1 включены последовательно соединенные грумповой компаратор 7, блок 8 управления и блок 9 смены временных каналов, дополнительный вход которого соединен с входами де пифраторов 2 и 3. Устройство также содержит ячейку памяти 10 оперативного запоминающего блока 1, блок 11 выдержки времени и блок 12 распределения временных каналов, причем выход блока 11 выдержки времени соединен с входом блока 12 распределения временных каналов, выход которого подключен к первому входу ячейки памяти 10, второй вход которой соединен с входом блока i I выдержки времени и с дополнительным входом блока 9 смены временных каналов. Устройство работает следующим образом. Импульс проключения формируется при считывании из оперативного запоминающего блока 1 управляющего слова, содержащего адреса входного 5 и выходного 6 канальных комплектов. После дешифрации адресов открываются электронные контакты 4 в соответствующих входных канальных комплектах 5. Информация между входными 5 и выходными 6 канальными комплектами передается по общей соединительной линии 13. Одновременно на вход блока 8 управления по общей соединительной линии 14 через компаратор 7 поступает код времени, прошедщего между моментами поступления фронта информационного импульса и импульсов проключеиия. Изменение фазы импульса проключения может производиться путем изменения кода выдержки времени. Блок 8 управления анализирует информацию о фазе коммутируемого сигнала, определяет номера каналов, фазу импульса проключения которых необходимо изменить, и выдает команду на блок 9 смены временных каналов, который представляет собой запоминающий регистр, в который записывается несколько управляющих слов. В зависимости от алгоритма переключения и команд, поступающих из блока 8 упраааения, запись информации из блока 9 смены временных каналов в оперативиый запоминающий блок I может производиться по-разному. Если сигнал переключения отсутствует, то управляющие слова записываются в те же ячейки памяти, откуда они были списаны. При наличии сигнала переключения ячейки записи управляющих слов меняются. 5Тактовая последовательность для считывания управляющих слов задается блоком 12 распределения временных каналов, который подключен к считывающему входу оперативного запоминающего блока 1. Ячейка памяти 10 хранит информацию о числе тактов, которые необходим.о пропустить перед считыванием очеред. ного управляющего слова. Блок 11 выдержки времени представляет собой двоичный счетчик, который обеспечивает задержку считывания очередного управляющего слова на число тактов, определяемых кодом, поступающим не вход счетчика. Таким образом, введение ячейки памяти 10 увеличивает число разрядов в управляющем .слове, но значительно сокращает требуемое количество Ячеек памяти для хранения управляющих слов. Формула изобретения Устройство временной асинхронной коммутации импульсных сигналов по авт. св. № 434610, отличающееся тем, что, с целью упрощения устройства путем уменьщения емкости запоминающего блока, введены ячейка памяти оперативного запоминающего блока, блок выдержки времени и блок распределения временных каналов, причем выход блока выдерки времени соединен с входом блока распрееления временных каналов, выход которого, одключен к первому входу ячейки памяти опеативного запоминающего блока, второй вход оторой соединен с входом блока выдержки ремени и с дополнительным входом блока смеы временных каналов. Источники информации, принятые во внимаие при экспертизе: . Авторскре свидетельство СССР№ 434610, , Н 04 L 11/20, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВРЕМЕННОЙ АСИНХРОННОЙ КОММУТАЦИИ ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU434610A1 |

| Устройство временной коммутации асинхронных импульсных сигналов | 1974 |

|

SU540413A1 |

| Канальное устройство объединенного коммутатора каналов и сообщений | 1975 |

|

SU531295A1 |

| СПОСОБ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105428C1 |

| Устройство временной коммутации асинхронных импульсных каналов | 1975 |

|

SU568194A2 |

| ТЕЛЕФОННАЯ СТАНЦИЯ ОПЕРАТИВНОЙ СВЯЗИ | 2003 |

|

RU2234817C1 |

| ПРИБОР ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПАРАЗИТНЫХ ИМПУЛЬСНЫХ ВОЗМУЩЕНИЙ В СЕТЯХ ЭЛЕКТРОПИТАНИЯ С ПЕРЕМЕННЫМ НАПРЯЖЕНИЕМ | 2002 |

|

RU2239201C2 |

| СИСТЕМА КОНФИДЕНЦИАЛЬНОЙ ТЕЛЕФОННОЙ СВЯЗИ | 2011 |

|

RU2474064C1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Устройство временной коммутации асинхронных импульсных каналов | 1975 |

|

SU581593A1 |

Авторы

Даты

1977-11-25—Публикация

1975-10-27—Подача