Изобретение относится к электроизмерительной технике и предназначено для измерения параметров коротких импульсных возмущений в сетях электропитания с переменным напряжением.

Известно устройство для дискретного измерения длительности электрических импульсов, содержащее элемент И-НЕ, счетчик импульсов и элемент задержки, причем выход элемента И-НЕ подключен к входу счетчика импульсов и входу элемента задержки, выход которого соединен с первым входом элемента И-НЕ, при этом в него введены элемент ИЛИ и инвертор, причем выход элемента И-НЕ через инвертор подключен к первому входу элемента ИЛИ, второй вход которого является входом устройства, а выход подключен ко второму входу элемента И-НЕ (см. а.с. № 1236390, кл. G 01 R 29/02).

Недостатком данного устройства являются ограниченные функциональные возможности, сложность устройства.

Известно устройство для измерения и анализа импульсных перенапряжений, содержащее n пороговых элементов И, дополнительный пороговый элемент и блок вывода информации, при этом в него введены n ключей, блок памяти, электронный коммутатор, переключатель, генератор прямоугольных импульсов, счетчик-делитель, дополнительный логический элемент И и входной блок, вход входного блока соединен с входом устройства, выход с входами n пороговых элементов непосредственно, а с входом дополнительного порогового элемента - через переключатель, выходы n пороговых элементов соединены с первыми входами соответствующих элементов И через ключи, выходы n элементов И подключены к входам электронного коммутатора через блок памяти, блок вывода информации подключен к выходу электронного коммутатора, управляющий вход которого соединен со вторым входом счетчика-делителя, вход счетчика-делителя соединен с выходом генератора прямоугольных импульсов, а первый выход - со вторым входом дополнительного логического элемента И, первый вход которого подключен к выходу дополнительного порогового элемента, а выход - ко вторым входам n логических элементов И, переключатель связан по цепям управления с ключами (см. а.с. № 1242839, кл. G 01 R 19/04).

Недостатком данного устройства являются ограниченные функциональные возможности, невысокая производительность труда.

Наиболее близким по технической сущности и достигаемому положительному эффекту и принятый авторами за прототип является амплитудный анализатор, содержащий N компараторов, первые входы которых соединены с входом устройства, а вторые входы с источниками пороговых напряжений, и N элементов И, при этом в него введены N+1 дифференцирующие цепочки, элемент ИЛИ-НЕ и триггер с раздельным запуском, выход которого подсоединен ко вторым входам элементов И, выходы которых соединены с соответствующими каналами регистрации и через элемент ИЛИ-НЕ с R-входом триггера, S-вход которого через дифференцирующую цепочку подсоединен к выходу первого компаратора, каждый из N компараторов через дифференцирующую цепочку соединен с первым входом соответствующего элемента И (см. а.с. № 1619201, кл. G 01 R 29/02).

Недостатком данного анализатора являются ограниченные функциональные возможности.

Технический результат, который может быть достигнут с помощью предлагаемого изобретения, сводится к совмещению возможностей устройств для измерения амплитуд и длительностей импульсов напряжения с целью их совместного одновременного использования и расширение функциональных возможностей измерителей.

Технический результат достигается с помощью прибора для измерения параметров паразитных импульсных возмущений в сетях с переменным напряжением, состоящего из схем амплитудного анализатора, содержащего N компараторов, N+1 дифференцирующие цепочки, N элементов И, триггер с раздельным запуском и элемент ИЛИ-НЕ, при этом он дополнительно снабжен анализатором длительности и блоком памяти, а в схему амплитудного анализатора дополнительно введены пороговые устройства, состоящие из включенного между фазным и нулевым проводами первичной сети симметричного полупроводникового ограничителя напряжения с порогом срабатывания соответствующим порогу ограничения (регистрации) данного канала, делителя напряжений, состоящего из включенных последовательно двух резисторов, и диодного моста, анодный вывод которого соединен с соответствующим компаратором схемы амплитудного анализатора, N канальных счетчиков, электронный коммутатор амплитудного анализатора со схемой управления, дешифратор амплитудного анализатора, устройство отображения информации и схема индикации, причем анализатор длительности включает последовательный двухтактный интегратор, элемент И, генератор стробирующих импульсов, счетчик стробирующих импульсов со схемой предварительного обнуления, состоящей из дифференцирующей цепочки, электронный коммутатор анализатора длительности со схемой управления, дешифратор анализатора длительности и устройство отображения информации, а блок памяти состоит из шифратора адреса считывания, шифратора адреса записи, запоминающего устройства, электронного коммутатора шины адреса и схемы управления для записи и считывания информации о параметрах каждого из зарегистрированных импульсов и вывода данной информации на устройство отображения информации.

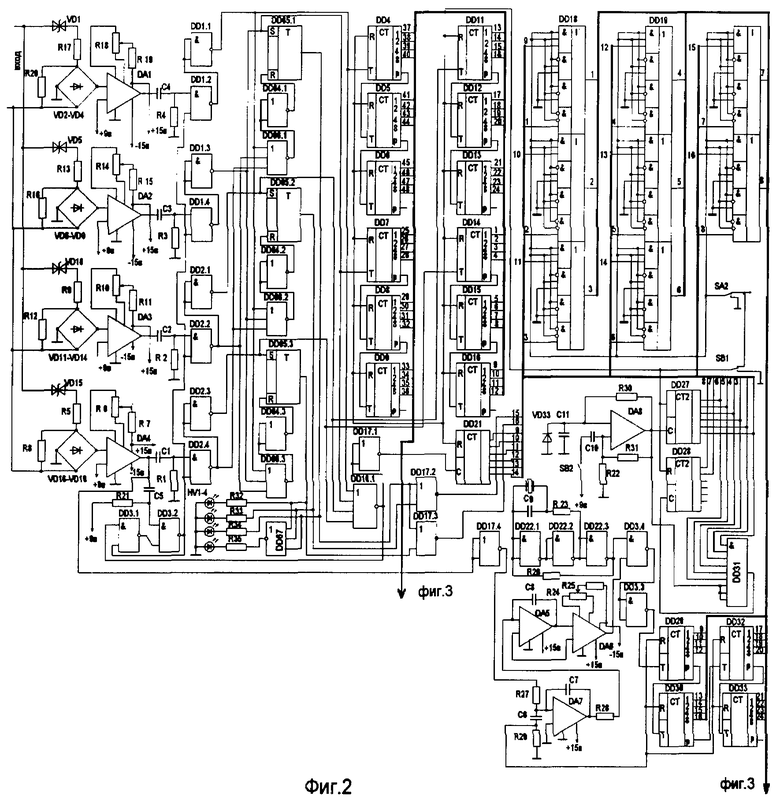

На фиг.1 дана функциональная схема прибора для измерения параметров паразитных импульсных возмущений в сетях электропитания с переменным напряжением.

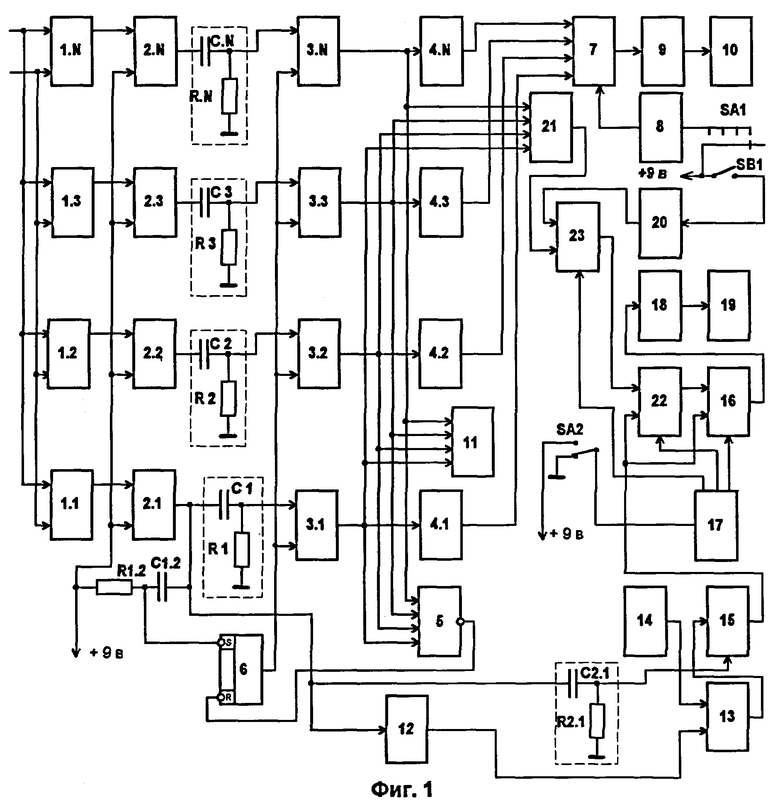

На фиг.2 дана принципиальная схема прибора для измерения параметров паразитных импульсных возмущений в сетях электропитания с переменным напряжением.

На фиг.3 продолжение принципиальной схемы прибора для измерения параметров паразитных импульсных возмущений в сетях электропитания с переменным напряжением.

Прибор для измерения параметров паразитных импульсных возмущений в сетях электропитания с переменным напряжением (фиг.1) состоит из схем амплитудного анализатора, содержащего N пороговых устройств 1.1, ..., 1.K, ..., 1.N, N компараторов 2.1, ..., 2.K, ..., 2.N, N+1 дифференцирующие цепочки R1C1, ..., RkCk, ..., R.NC.N, R1.2C1.2, N элементов И 3.1, ..., 3.K, ..., 3.N, N канальных счетчиков 4.1, ..., 4.K, ..., 4.N, элемент ИЛИ-НЕ 5, триггер 6 с раздельным запуском, электронный коммутатор 7 амплитудного анализатора со схемой управления 8, дешифратор 9 амплитудного анализатора, устройство 10 отображения информации и схему индикации 11; схемы анализатора длительности, включающего последовательный двухтактный интегратор 12, элемент И 13, генератор стробирующих импульсов 14, счетчик 15 стробирующих импульсов со схемой предварительного обнуления, состоящей из дифференцирующей цепочки R2.1C2.1, электронный коммутатор 16 анализатора длительности со схемой управления 17, дешифратор 18 анализатора длительности и устройство 19 отображения информации; блока памяти, включающего шифратор адреса считывания 20, шифратор адреса записи 21, запоминающее устройство 22, электронный коммутатор 23 шины адреса, и схему управления 16 для записи и считывания информации о параметрах каждого из зарегистрированных импульсов и вывода данной информации на устройство отображения.

Пороговое устройство 1.N (фиг.1) состоит из включенного между фазным и нулевым проводами первичной сети симметричного полупроводникового ограничителя напряжения VD1 (фиг.2) с порогом срабатывания, соответствующим порогу ограничения (регистрации) данного канала, делителя напряжений, состоящего из включенных последовательно двух резисторов R17-R20 (фиг.2), и диодного моста VD2-VD4 (фиг.2), анодный вывод которого соединен с канальным компаратором DA1 (фиг.2) схемы амплитудного анализатора.

Канальные счетчики 4.1-4.N (фиг.1) построены по принципу декадного счета на микросхемах DD4-DD9, DD11-DD16 (фиг.2). Максимальное количество декад определяется размерностью числа отображающего количество регистрируемых импульсов, которая в свою очередь определяется условиями удобства использования прибора и условиями экономической целесообразности.

Электронный коммутатор 7 (фиг.1) амплитудного анализатора построен на двенадцати четырехвходовых кодовых ключах DD23-DD26 (фиг.3). Количество ключей в данном случае определяется размерностью двоично-десятичного кода, поступающего с выходов канальных счетчиков 4.1-4.N (фиг.1). Количество входов на ключах определяется соответственно количеством каналов регистрации.

Схема управления 8 (фиг.1) электронным коммутатором 7 (фиг.1) амплитудного анализатора включает в себя четырехпозиционный переключатель SA1 (фиг.3), три двухпозиционных реле Р1-Р3 (фиг.3) и шифратор, собранный на двух элементах ИЛИ-НЕ DD63.1-DD63.2 (фиг.3).

Дешифратор 9 (фиг.1) амплитудного анализатора построен на трех дешифраторах DD37, DD44, DD52 (фиг.3).

Схема индикации 11 (фиг.1) состоит из четырех светодиодов HV1-HV4 (фиг.2), четырех токозадающих резисторов R32-R35 (фиг.2), четырех элементов 3ИЛИ-НЕ DD66.1-DD66.3,DD67 (фиг.2), трех элементов НЕ DD64.1-DD64.3 (фиг.2) и трех RS-триггеров DD65.1-DD65.3 (фиг.2) с прямыми входами.

Последовательный двухтактный интегратор 12 (фиг.1) состоит из двух интеграторов DA7, DA5 (фиг.2) и компаратора DA6 (фиг.2). Интеграторы DA7, DA5 (фиг.2) выполнены на основе использования операционных усилителей, в цепь обратной связи которых включены конденсаторы С7, С8 (фиг.2) и резисторы R27, R28 (фиг.2), постоянные времени которых согласованы между собой, а компаратор DA6 (фиг.2) выполнен по классической схеме на основе использования операционного усилителя.

Генератор стробирующих импульсов 14 (фиг.1) собран по схеме мультивибратора на элементах DD22.1-DD22.3 (фиг.2).

Счетчик 15 (фиг.1) стробирующих импульсов построен на микросхемах DD29, DD30, DD32, DD33 (фиг.2) по принципу декадного счета. Количество декад определяется размерностью числа отображающего длительность входного паразитного импульсного воздействия, которая в свою очередь определяется условиями удобства использования прибора и условиями экономической целесообразности.

Электронный коммутатор 16 (фиг.1) анализатора длительности построен на 16-ти 4-входовых кодовых ключах DD42, DD47, DD50, DD55, DD58, DD62 (фиг.3) по тому же принципу, что и электронный коммутатор 7 (фиг.1) амплитудного анализатора.

Схема управления 17 (фиг.1), представляет собой двухпозиционный переключатель SA2 (фиг.3), который подключается либо к источнику с напряжением логической единицы, либо к источнику с напряжением логического нуля.

Дешифратор 18 (фиг.1) анализатора длительности построен на микросхемах DD36, DD43, DD51, DD59 (фиг.3) аналогично дешифратору 9 (фиг.1) амплитудного анализатора.

Шифратор адреса считывания 20 (фиг.1) включает в себя генератор одиночных импульсов DA8 (фиг.2) и двоичный восьмиразрядный счетчик DD27.DD28 (фиг.2).

Шифратор адреса записи 21 (фиг.1) состоит из шифратора DD17.2, DD17.3 (фиг.2) амплитудного анализатора и счетчика DD21 (фиг.2) количества импульсов. Шифратор DD17.2, DD17.3 (фиг.2) амплитудного анализатора построен на двух элементах ИЛИ-НЕ и работает аналогично шифратору схемы управления 8 (фиг.1) электронным коммутатором 7 (фиг.1) амплитудного анализатора.

Запоминающее устройство 22 (фиг.1) построено на стандартных микросхемах памяти DD34, DD35, DD38-DD41, DD45, DD46, DD48, DD49, DD53, DD54, DD56, DD57, DD60, DD61 (фиг.3), представляющих собой стационарные оперативные запоминающие устройства объемом памяти 256×1 бит.

Электронный коммутатор 23 (фиг.1) шины адреса собран на микросхемах DD18-DD20 (фиг.2) по той же схеме, что и электронный коммутатор 16 (фиг.1) анализатора длительности. Количество ключей определяется размерностью кодовой комбинации, задающей адрес ячейки запоминающего устройства 22 (фиг.1), что в свою очередь определяется объемом памяти выбранной микросхемы памяти.

Прибор работает следующим образом.

В исходном состоянии (до поступления входного импульса) на входах всех каналов амплитудного анализатора напряжение первичной сети ниже порога срабатывания полупроводниковых ограничителей напряжения, ток в шунтирующих цепях полупроводниковых ограничителей напряжения VD1, VD5, VD10, VD15 (фиг.2) минимален и соответствует обратному току полупроводниковых ограничителей напряжения, уровни сравнения компараторов 2.1-2.N (фиг.1) соответствуют нижним порогам каналов регистрации. На выходах всех компараторов 2.1-2.N (фиг.1) напряжения соответствуют напряжению логической единицы, на всех первых и вторых входах элементов И 3.1-3.N (фиг.1) напряжения соответствуют напряжению логического нуля, на всех входах элемента ИЛИ-НЕ 5 (фиг.1) и на всех входах канальных счетчиков 4.1-4.N (фиг.1) напряжение соответствует напряжению логического нуля, а на выходе элемента ИЛИ-НЕ 5 (фиг.1) напряжению логической единицы. Триггер 6 (фиг.1) в этом интервале времени на R- и S-входах имеет напряжение логической единицы, а на Q-выходе напряжение логического нуля. Канальные счетчики 4.1-4.N (фиг.1) находятся в нулевом состоянии. На выходе дешифратора 9 (фиг.1) амплитудного анализатора информация соответствует нулевому состоянию канальных счетчиков 4.1-4.N (фиг.1), устройство 10 (фиг.1) отображения информации амплитудного анализатора отображает нули.

На выходе последовательного двухтактного интегратора 12 (фиг.1) напряжение логического нуля, которое поступает на второй вход элемента И 13 (фиг.1). На первый вход элемента И 13 (фиг.1) поступают стробирующие импульсы с генератора стробирующих импульсов 14 (фиг.1). На выходе элемента И 13 (фиг.1) напряжение соответствует напряжению логического нуля. Счетчик 15 (фиг.1) стробирующих импульсов находится в нулевом состоянии в ждущем режиме. На выходе счетчика 15 (фиг.1) стробирующих импульсов информация соответствует нулевому состоянию счетчика 15 (фиг.1) стробирующих импульсов. Выход счетчика 15 (фиг.1) стробирующих импульсов подключен одновременно к первому входу электронного коммутатора 16 (фиг.1) анализатора длительности и к входу запоминающего устройства 22 (фиг.1), которое находится в нулевом состоянии и готово к записи информации. Второй вход электронного коммутатора 16 (фиг.1) анализатора длительности подключен к выходу запоминающего устройства 22 (фиг.1). В зависимости от управляющего сигнала со схемы управления 17 (фиг.1), выход электронного коммутатора 16 (фиг.1) анализатора длительности коммутируется либо с выходом запоминающего устройства 22 (фиг.1), либо с выходом счетчика 15 (фиг.1) стробирующих импульсов. Информация с электронного коммутатора 16 (фиг.1) анализатора длительности преобразуется дешифратором 18 (фиг.1) анализатора длительности и поступает на вход устройства 19 (фиг.1) отображения информации, которое отображает нули.

При поступлении паразитного импульсного возмущения на вход схемы амплитудного анализатора, напряжение на его входе возрастает и становится равным напряжению порога срабатывания первого полупроводникового ограничителя напряжения VD15 (фиг.2), при этом ток в шунтирующей цепи первого полупроводникового ограничителя напряжения VD15 (фиг.2) резко возрастает, напряжение на делителе напряжения R5, R8 (фиг.2) становится равным порогу срабатывания первого компаратора 2.1 (фиг.1), напряжение на выходе первого компаратора 2.1 (фиг.1) скачком уменьшается до напряжения логического нуля. Продифференцированное напряжение с выхода первого компаратора 2.1 (фиг.1) в виде отрицательного импульса поступает на S-вход триггера 6 (фиг.1) и устанавливает на его Q-выходе состояние логической единицы и, следовательно, на вторых входах всех элементов И 3.1-3.N (фиг.1) - напряжение логической единицы.

Отрицательный импульс на первом входе элемента И 3.1 (фиг.1) не изменяет его состояния.

По мере увеличения напряжения Uимп на входе амплитудного анализатора и последовательном достижении пороговых напряжений полупроводниковых ограничителей напряжения VD1, VD5, VD10, VD15 (фиг.2) происходит срабатывания соответствующих компараторов 2.1-2.N (фиг.1) напряжения, с выхода которых сигналы после дифференцирования в виде отрицательных импульсов напряжения поступают на соответствующие элементы И 3.1-3.N (фиг.1), однако влияния на состояния элементов И 3.1-3.N (фиг.1) эти импульсы не оказывают. Высший номер сработавшего компаратора 2.К (фиг.1) определяется условием Uk<Uимп<Uk+1 и соответствует превышению максимального значения К-го порогового уровня напряжения.

После перехода Uимп через максимальное значение начинается обратное срабатывание компараторов, т.е. переход от напряжения логического нуля к напряжению логической единицы. Первым происходит переброс компаратора 2.К (фиг.1) и далее по порядку убывания номеров. Таким образом, компаратор 2.К (фиг.1) вырабатывает импульс с минимальной длительностью. На выходах дифференцирующих цепочек при этом формируются положительные импульсы, поступающие на первые входы элементов И 3.К-3.1 (фиг.1).

При поступлении положительного импульса на первый вход элемента И 3.К (фиг.1), на втором входе которого также положительное напряжение, на выходе этого элемента формируется импульсное напряжение с длительностью, определяемой постоянной времени дифференцирующей цепочки RkCk, и с амплитудой, соответствующей напряжению логической единицы. Этот импульс поступает на вход канального счетчика 4.К (фиг.1), на вход схемы индикации 11 (фиг.1), на вход шифратора адреса записи 21 (фиг.1) и на вход элемента ИЛИ-НЕ 5 (фиг.1). На выходе элемента ИЛИ-НЕ 5 (фиг.1) образуется импульс с напряжением логического нуля, который поступает на R-вход триггера 6 (фиг.1). Напряжение на Q-выходе триггера 6 (фиг.1) становится равным напряжению логического нуля. На вторых входах всех элементов И 3.1-3.N (фиг.1) устанавливается напряжение логического нуля.

Начиная с этого момента времени, на выходах всех элементов И 3.1-3.N (фиг.1) присутствует напряжение логического нуля независимо от напряжения на их первых входах.

Завершением цикла анализа амплитуды паразитного импульсного возмущения является обратное срабатывание (формирование положительного перепада напряжения) первого компаратора 2.1 (фиг.1) и завершение переходных процессов в дифференциальной цепочке R1,C1 (фиг.1).

Импульс с выхода элемента И 3.К (фиг.1) поступает на вход канального счетчика 4.К (фиг.1), на вход схемы индикации 11 (фиг.1), на вход шифратора адреса записи 21 (фиг.1) и на вход элемента ИЛИ-НЕ 5 (фиг.1). Канальные счетчики 4.1-4.N (фиг.1) осуществляют подсчет количества импульсов, пришедших по каждому из каналов. Информация в двоичном коде с выхода канальных счетчиков 4.1-4.N (фиг.1) поступает на вход электронного коммутатора 7 (фиг.1) амплитудного анализатора. В зависимости от управляющего сигнала со схемы управления 8 (фиг.1) на выход электронного коммутатора 7 (фиг.1) амплитудного анализатора поступает информация с одного из каналов. Эта информация преобразуется дешифратором 9 (фиг.1) амплитудного анализатора в код семисегментных индикаторов устройства 10 (фиг.1) отображения информации. Индикаторы устройства 10 (фиг.1) отображения информации отображают количество импульсов пришедших по скоммутированному каналу, т.е. количества импульсов соответствующих уровню напряжения данного канала. Шифратор адреса записи 21 (фиг.1) в зависимости от того, по какому каналу и каким по счету пришел импульс, формирует адрес ячейки памяти запоминающего устройства 22 (фиг.1), в которую будет записана информация о длительности импульса. Адрес ячейки памяти с шифратора адреса записи 21 (фиг.1) в двоичном коде поступает на первый вход электронного коммутатора 23 (фиг.1) шины адреса. На второй вход электронного коммутатора 23 (фиг.1) шины адреса поступает адрес ячейки памяти с шифратора адреса считывания 20 (фиг.1). В зависимости от управляющего сигнала “запись/считывание” со схемы управления 17 (фиг.1) на выход электронного коммутатора 23 (фиг.1) шины адреса приходит либо адрес для записи, либо адрес для считывания, который подается на адресные входы запоминающего устройства 22 (фиг.1).

Из канала, имеющего наименьший порог срабатывания, импульс отрицательной полярности с длительностью, соответствующей длительности паразитного импульсного воздействия на уровне наименьшего порога регистрации, с выхода компаратора 2.1 (фиг.1) поступает на вход последовательного двухтактного интегратора 12 (фиг.1). Сигнал с выхода последовательного двухтактного интегратора 12 (фиг.1) поступает на второй вход элемента И 13 (фиг.1), на первый вход которого поступают стробирующие импульсы с генератора стробирующих импульсов 14 (фиг.1). С выхода элемента И 13 (фиг.1) сформированная последовательность стробирующих импульсов, пропорциональная длительности входного паразитного импульсного воздействия, поступает на вход счетчика 15 (фиг.1) стробирующих импульсов. Информация о состоянии счетчика 15 (фиг.1) стробирующих импульсов в двоичном коде поступает одновременно на первый вход электронного коммутатора 16 (фиг.1) анализатора длительности и на информационный вход запоминающего устройства 22 (фиг.1). На второй вход электронного коммутатора 16 (фиг.1) анализатора длительности поступает информация с выхода запоминающего устройства 22 (фиг.1). В зависимости от сигнала управления “запись/считывание” со схемы управления 17 (фиг.1) запоминающее устройство 22 (фиг.1) осуществляет запись информации либо ее считывание и выдачу на информационные выводы. В зависимости от управляющего сигнала со схемы управления 17 (фиг.1), на выход электронного коммутатора 16 (фиг.1) анализатора длительности поступает информация о состоянии счетчика 15 (фиг.1) стробирующих импульсов, соответствующая длительности последнего пришедшего паразитного импульсного воздействия, либо информация о состоянии запоминающего устройства 22 (фиг.1), т.е. о длительности паразитных импульсных воздействий, пришедших ранее. Информация с выхода электронного коммутатора 16 (фиг.1) анализатора длительности преобразуется дешифратором 18 (фиг.1) анализатора длительности в код семисегментных индикаторов устройства 19 (фиг.1) отображения информации. Индикаторы устройства 19 (фиг.1) отображения информации отображают длительность паразитного импульсного воздействия.

Для отображения информации о срабатывании конкретного порогового устройства в прибор введена схема индикации 11 (фиг.1). При срабатывании одного из трех пороговых устройств 1.1-1.3 (фиг.1) импульс с выхода соответствующего элемента И 3.1-3.3 (фиг.1) данного канала поступает на S-вход соответствующего RS-триггера DD65.1-DD65.3 (фиг.2). В результате этого данный триггер переходит в единичное состояние, на его выходе напряжение становится равным напряжению логической единицы. Это напряжение поступает на соответствующие последовательно соединенные светодиод HV1, HV2, или HV3 (фиг.2) и токозадающий резистор R32, R34, или R34 (фиг.2) соответственно. В результате этого один из светодиодов HV1, HV2 или HV3 (фиг.2) загорается. Одновременно с этим с выходов элементов 3ИЛИ-НЕ DD66.1-DD66.3 (фиг.2) остальных каналов импульс напряжением логического нуля поступает на входы элементов НЕ DD64.1-DD64.3 (фиг.2) и инвертируется. С выходов элементов НЕ DD64.1-DD64.3 (фиг.2) импульс с напряжением логической единицы поступает на R-входы соответствующих RS-триггеров DD65.1-DD65.3 (фиг.2) и переводит их в нулевое состояние. На выходах RS-триггеров DD65.1-DD65.3 (фиг.2) напряжение равно напряжению логического нуля. Оно поступает на соответствующие последовательно соединенные светодиоды HV1-HV4 (фиг.2) и токозадающие резисторы R32-R35 (фиг.2), однако влияния на их состояние не оказывают, данные светодиоды не горят.

При срабатывании порогового устройства 1.4 импульс напряжением логической единицы с выхода элемента И 3.4 (фиг.1) поступает параллельно на входы элементов 3ИЛИ-НЕ DD66.1-DD66.3 (фиг.2) остальных каналов. С выходов элементов 3ИЛИ-НЕ DD66.1-DD66.3 (фиг.2) импульсы с напряжением логического нуля поступают на входы элементов НЕ DD64.1-DD64.3 (фиг.2) и инвертируются. С выходов элементов НЕ DD64.1-DD64.3 (фиг.2) импульсы с напряжением логической единицы поступают на R-входы соответствующих RS-триггеров DD65.1-DD65.3 (фиг.2) и переводят их в нулевое состояние. На выходах всех трех RS-триггеров DD65.1-DD65.3 (фиг.2) напряжение логического нуля. Это напряжение поступает на входы элемента 3ИЛИ-НЕ DD67 (фиг.2). На выходе элемента 3ИЛИ-НЕ DD67 (фиг.2) напряжение равно напряжению логической единицы. Оно поступает на последовательно соединенные светодиод HV4 (фиг.2) и токозадающий резистор R35 (фиг.2) четвертого канала. Светодиод HV4 (фиг.2) четвертого канала загорается, остальные светодиоды HV1-HV3 (фиг.2) гаснут.

Канальные счетчики 4.1-4.N (фиг.1) построены по принципу декадного счета на микросхемах DD4-DD9, DD11-DD16 (фиг.2). Максимальное количество декад определяется размерностью числа отображающего количество регистрируемых импульсов, которая в свою очередь определяется условиями удобства использования прибора и условиями экономической целесообразности. Например, при использовании трехдекадных счетчиков, они позволяют подсчитывать до 999 импульсов.

Импульсы счета поступают на счетчики 4.1-4.N (фиг.1) с элементов И 3.1-3.N (фиг.1), а информация о состоянии счетчиков 4.1-4.N (фиг.1) выводится в двоично-десятичном коде по двенадцатиразрядной шине (каждому десятичному разряду соответствует 4 разряда двоичного кода) на электронный коммутатор 7 (фиг.1) амплитудного анализатора.

Электронный коммутатор 7 (фиг.1) амплитудного анализатора построен на двенадцати четырехвходовых кодовых ключах DD23-DD26 (фиг.3). Количество ключей в данном случае определяется размерностью двоично-десятичного кода, поступающего с выходов канальных счетчиков 4.1-4.N (фиг.1). Количество входов на ключах определяется соответственно количеством каналов регистрации. Таким образом, разряды с одинаковыми весами всех каналов поступают на один из четырех входов одного ключа. При поступлении со схемы управления 8 (фиг.1) электронным коммутатором 7 (фиг.1) амплитудного анализатора двухразрядной двоичной кодовой комбинации на управляющие входы ключей, выходы ключей коммутируются с одним из входов. Таким образом, на выходе электронного коммутатора 7 (фиг.1) амплитудного анализатора формируется двенадцатиразрядный двоично-десятичный код, который соответствует коду на входе электронного коммутатора 7 (фиг.1) амплитудного анализатора по одному из каналов.

Дешифратор 9 (фиг.1) амплитудного анализатора предназначен для преобразования двоично-десятичного кода канальных счетчиков 4.1-4.N (фиг.1) в код семисегментных индикаторов. Он построен на трех дешифраторах DD37, DD44, DD52 (фиг.3). Двоично-десятичный код С выхода электронного коммутатора 7 (фиг.1) амплитудного анализатора поступает по двенадцатиразрядной шине на входы трех дешифраторов DD37, DD44, DD52 (фиг.3), причем на каждый из дешифраторов DD37, DD44, DD52 (фиг.3) поступают четыре разряда соответствующие одному разряду десятичного числа. Дешифраторы DD37, DD44, DD52 (фиг.3) преобразуют поступивший на их входы двоично-десятичный код в код семисегментных индикаторов устройства 10 (фиг.1) отображения информации. Индикаторы устройства 10 (фиг.1) отображения информации отображают в десятичной системе исчисления количество импульсов прошедших по скоммутированному каналу.

Схема управления 8 (фиг.1) электронным коммутатором 7 (фиг.1) амплитудного анализатора включает в себя четырехпозиционный переключатель SA1 (фиг.3), три двухпозиционных реле Р1-Р3 (фиг.3) и шифратор, собранный на двух элементах ИЛИ-НЕ DD63.1-DD63.2 (фиг.3). Данная схема формирует двухразрядную двоичную кодовую комбинацию, которая и осуществляет управление электронным коммутатором 7 (фиг.1) амплитудного анализатора. При выборе четырехпозиционным переключателем SA1 (фиг.3) первого канала регистрации срабатывает реле Р1 (фиг.3). Его контакты подключаются к источнику с напряжением логической единицы (на фиг. не показан), и, соответственно, на выходе реле Р1 (фиг.3) напряжение становится равным напряжению логической единицы. Остальные реле Р2-Р3 (фиг.3) подключены своими контактами к источнику с напряжением логического нуля (не показан). В результате этого на вход шифратора DD63.1-DD63.2 (фиг.3) поступает унитарный код вида 100, который преобразуется шифратором DD63.1-DD63.2 (фиг.3) в двоичную кодовую комбинацию вида 00.

Данная комбинация поступает на управляющие входы электронного коммутатора 7 (фиг.1) амплитудного анализатора и осуществляет коммутацию первого канала на выход электронного коммутатора 7 (фиг.1) амплитудного анализатора. При выборе четырехпозиционным переключателем SA1 (фиг.3) 2-го или 3-го каналов регистрации происходит срабатывание соответствующего реле Р2 или Р3 (фиг.3) и его контакты подключаются к источнику с напряжением логической единицы, в то время когда контакты остальных двух реле Р1-Р3 (фиг.3) подключены к источнику с напряжением логического нуля. В результате этого на вход шифратора DD63.1-DD63.2 (фиг.3) аналогичным образом поступают унитарные кодовые комбинации видов 010 или 001, которые преобразуются шифратором DD63.1-DD63.2 (фиг.3) в двоичные кодовые комбинации видов 01 или 10. Эти комбинации поступают на управляющие входы электронного коммутатора 7 (фиг.1) амплитудного анализатора и осуществляют коммутацию на его выход второго или третьего каналов соответственно.

При выборе четырехпозиционным переключателем SA1 (фиг.3) четвертого канала ни одно из реле Р1-Р3 (фиг.3) не срабатывает, их контакты подключены к источнику с напряжением логического нуля. В результате этого на входе шифратора DD63.1-DD63.2 (фиг.3) унитарная кодовая комбинация имеет вид 000. Она преобразуется шифратором DD63.1-DD63.2 (фиг.3) в двоичную комбинацию вида 11 и, поступая на управляющие входы электронного коммутатора 7 (фиг.1) амплитудного анализатора, коммутирует на его выход четвертый канал.

Для увеличения длительности входного импульсного возмущения и, соответственно повышения чувствительности прибора в нижней части временного диапазона, в приборе использован способ последовательного интегрирования. Последовательный двухтактный интегратор 12 (фиг.1) состоит из двух интеграторов DA7, DA5 (фиг.2) и компаратора DA6 (фиг.2). Интеграторы DA7, DA5 (фиг.2) выполнены на основе использования операционных усилителей, в цепь обратной связи которых включены конденсаторы С7, С8 (фиг.2) и резисторы R27, R28 (фиг.2), постоянные времени которых согласованы между собой, а компаратор DA6 (фиг.2) выполнен по классической схеме на основе использования операционного усилителя. Инвертирующий вход усилителя соединяется с источником опорного напряжения (в данном случае напряжение логического нуля), а на неинвертирующий вход подается напряжение с интегратора. В схеме компаратора DA6 (фиг.2) используется свойство операционного усилителя изменять полярность (знак) выходного напряжения при изменении полярности на его входах.

Импульс с напряжением логической единицы с выхода последовательного двухтактного интегратора 12 (фиг.1) поступает на второй вход элемента И-НЕ DD3.4 (фиг.2). На первый вход элемента И-НЕ DD3.4 (фиг.2) поступают стробирующие импульсы с генератора стробирующих импульсов 14 (фиг.1). Генератор стробирующих импульсов 14 (фиг.1) собран по схеме мультивибратора на элементах DD22.1-DD22.3 (фиг.2). Стабилизация частоты следования стробирующих импульсов осуществляется кварцем. На выходе элемента И-НЕ DD3.4 (фиг.2) образуется последовательность стробирующих импульсов отрицательной полярности, количество которых пропорционально длительности входного паразитного импульсного воздействия. Данная последовательность поступает на вход инвертора DD3.3 (фиг.2), построенного на элементе И-НЕ. С выхода инвертора DD3.3 (фиг.2) последовательность стробирующих импульсов положительной полярности с напряжением логической единицы поступает на вход счетчика 15 (фиг.1) стробирующих импульсов.

Счетчик 15 (фиг.1) стробирующих импульсов построен на микросхемах DD29, DD30, DD32, DD33 (фиг.2) по принципу декадного счета. Количество декад определяется размерностью числа отображающего длительность входного паразитного импульсного воздействия, которая в свою очередь определяется условиями удобства использования прибора и условиями экономической целесообразности. Например, при использовании четырехдекадного счетчика имеется возможность подсчитывать до 9999 стробирующих импульсов.

В схему счетчика 15 (фиг.1) стробирующих импульсов включена схема предварительного обнуления счетчика, представляющая собой дифференцирующую цепочку С6, R29 (фиг.2). Импульс прямоугольной формы отрицательной полярности из канала регистрации с наименьшим порогом срабатывания с выхода компаратора 2.1 (фиг.1) через инвертор DD17.4 (фиг.2) поступает на дифференцирующую цепочку С6, R29 (фиг.2). На выходе дифференцирующей цепочки С6, R29 (фиг.2) формируется импульс напряжения положительной полярности с длительностью, определяемой постоянной времени дифференцирующей цепочки С6, R29 (фиг.2), и с амплитудой, соответствующей напряжению логической единицы. Этот импульс поступает на обнуляющий вход счетчика 15 (фиг.1) стробирующих импульсов и переводит его в нулевое состояние.

Информация о состоянии счетчика 15 (фиг.1) стробирующих импульсов выводится в двоично-десятичном коде по 16-ти разрядной шине, поступает на информационный вход запоминающего устройства 22 (фиг.1) и на вход электронного коммутатора 16 (фиг.1) анализатора длительности.

Электронный коммутатор 16 (фиг.1) анализатора длительности построен на 16-ти 4-входовых кодовых ключах DD42, DD47, DD50, DD55, DD58, DD62 (фиг.3) по тому же принципу, что и электронный коммутатор 7 (фиг.1) амплитудного анализатора. На первые входы ключей электронного коммутатора 16 (фиг.1) анализатора длительности поступают разряды со счетчика 15 (фиг.1) стробирующих импульсов, на четвертые - соответственно разряды из запоминающего устройства 22 (фиг.1). Вторые и третьи входы ключей не используются.

Управление электронным коммутатором 16 (фиг.1) анализатора длительности осуществляется при помощи схемы управления 17 (фиг.1), представляющей собой двухпозиционный переключатель SA2 (фиг.3), который подключается либо к источнику с напряжением логической единицы, либо к источнику с напряжением логического нуля.

Шестнадцатиразрядный двоично-десятичный код с выхода электронного коммутатора 16 (фиг.1) анализатора длительности поступает на дешифратор 18 (фиг.1) анализатора длительности. На выходе дешифратора 18 (фиг.1) анализатора длительности формируется код семисегментных индикаторов устройства 19 (фиг.1) отображения информации. Индикаторы устройства 19 (фиг.1) отображения информации отображают длительность паразитного импульсного воздействия.

С целью длительного хранения информации о длительности и амплитуде паразитного импульсного воздействия в прибор введена схема запоминающего устройства 22 (фиг.1). Запоминающее устройство 22 (фиг.1) построено на стандартных микросхемах памяти DD34, DD35, DD38-DD41, DD45, DD46, DD48, DD49, DD53, DD54, DD56, DD57, DD60, DD61 (фиг.3), представляющих собой стационарные оперативные запоминающие устройства объемом памяти 256×1 бит. Оно построено по следующему принципу: одна ячейка микросхемы памяти хранит в себе информацию лишь об одном разряде слова, вся микросхема способна запомнить 256 одноразрядных слов. Таким образом, N микросхем памяти способны хранить информацию о 256 N-разрядных двоичных кодовых комбинациях. Количество разрядов N в данном случае определяется количеством декад счетчика 15 (фиг.1) стробирующих импульсов, т.е. размерностью числа, отображающего длительность входного паразитного импульсного воздействия. Например, при использовании четырехдекадного счетчика количество микросхем будет равно 16.

Каждый из 16 разрядов поступает на вход соответствующей микросхемы памяти. Информация о содержимом запоминающего устройства 22 (фиг.1) выводится с информационных выходов также поразрядно и поступает на четвертые входы ключей электронного коммутатора 16 (фиг.1) анализатора длительности.

Переключение запоминающего устройства 22 (фиг.1) из режима записи в режим считывания и наоборот осуществляется при помощи схемы управления 17 (фиг.1), которая является единой для запоминающего устройства 22 (фиг.1), электронного коммутатора 16 (фиг.1) анализатора длительности и электронного коммутатора 23 (фиг.1) шины адреса и представляет собой двухпозиционный переключатель SA2 (фиг.3).

Для задания адреса обращения к конкретной ячейке запоминающего устройства 22 (фиг.1) в схему прибора введены шифратор адреса записи 21 (фиг.1), шифратор адреса считывания 20 (фиг.1) и электронный коммутатор 23 (фиг.1) шины адреса.

Электронный коммутатор 23 (фиг.1) шины адреса собран на микросхемах DD18-DD20 (фиг.2) по той же схеме, что и электронный коммутатор 16 (фиг.1) анализатора длительности. Количество ключей определяется размерностью кодовой комбинации, задающей адрес ячейки запоминающего устройства 22 (фиг.1), что в свою очередь определяется объемом памяти выбранной микросхемы памяти. В данном случае для микросхемы 256×1 бит количество разрядов шины адреса равно 8, следовательно, и электронный коммутатор 23 (фиг.1) шины адреса будет иметь 8 ключей. На первые входы электронного коммутатора 23 (фиг.1) шины адреса подаются разряды с шифратора адреса записи 21 (фиг.1), а на четвертые - с шифратора адреса считывания 20 (фиг.1). Вторые и третьи входы ключей остаются незадействованными.

При переключении двухпозиционного переключателя SA2 (фиг.2) схемы управления 17 (фиг.1) в положение “запись” его контакты подключаются к источнику с напряжением логической единицы. Запоминающее устройство 22 (фиг.1) переходит в режим записи, электронный коммутатор 23 (фиг.1) шины адреса, на управляющих входах которого напряжение логической единицы, коммутирует на адресные входы запоминающего устройства 22 (фиг.1) соответствующие разряды шифратора адреса записи 21 (фиг.1), а электронный коммутатора 16 (фиг.1) анализатора длительности, на управляющих входах которого также напряжение логической единицы, коммутирует выходы счетчика 15 (фиг.1) стробирующих импульсов на соответствующие входы дешифратора 18 (фиг.1) анализатора длительности.

При переключении двухпозиционного переключателя SA1 (фиг.2) в положение “считывание” его контакты подключаются к источнику с напряжением логического нуля. Запоминающее устройство 22 (фиг.1) переходит в режим “считывание”, электронный коммутатор 23 (фиг.1) шины адреса, на управляющих входах которого напряжение логического нуля, коммутирует на адресные входы запоминающего устройства 22 (фиг.1) соответствующие разряды шифратора адреса считывания 20 (фиг.1), а электронный коммутатор 16 (фиг.1) анализатора длительности, на управляющих входах которого также напряжение логического нуля, коммутирует информационные выходы запоминающего устройства 22 (фиг.1) на соответствующие входы дешифратора 18 (фиг.1) анализатора длительности.

Для задания конкретного адреса ячейки памяти в устройство введены схемы шифратора адреса записи 21 (фиг.1) и шифратора адреса считывания 20 (фиг.1).

Шифратор адреса записи 21 (фиг.1) состоит из шифратора DD17.2, DD17.3 (фиг.2) амплитудного анализатора и счетчика DD21 (фиг.2) количества импульсов. Шифратор DD17.2, DD17.3 (фиг.2) амплитудного анализатора построен на двух элементах ИЛИ-НЕ и работает аналогично шифратору схемы управления 8 (фиг.1) электронным коммутатором 7 (фиг.1) амплитудного анализатора. Информация о состоянии каналов приходит с RS-триггеров DD65.1, DD65.2, DD65.3 (фиг.2) на три входа шифратора DD17.2, DD17.3 (фиг.2). В зависимости от того, по какому из 4-х каналов прошел паразитный импульс, шифратор DD17.2, DD17.3 (фиг.2) вырабатывает двухразрядную двоичную кодовую комбинацию. Данная комбинация подается на два старших разряда шины адреса. Именно эти разряды и несут информацию об амплитуде входного воздействия. Импульсы со схемы ИЛИ-НЕ 5 (фиг.1) амплитудного анализатора через инвертор DD17.1 (фиг.2) поступают на вход счетчика DD21 (фиг.2) количества импульсов. Данный счетчик DD21 (фиг.2) количества импульсов представляет собой двоичный шестиразрядный счетчик. Информация о состоянии счетчика DD21 (фиг.2) количества импульсов по шестиразрядной шине подается на младшие разряды шины адреса. Таким образом, адрес ячейки запоминающего устройства 22 (фиг.1), к которой осуществляется обращение, определяется порядковым номером входного паразитного воздействия и его амплитудой.

Шифратор адреса считывания 20 (фиг.1) включает в себя генератор одиночных импульсов DA8 (фиг.2) и двоичный восьмиразрядный счетчик DD27, DD28 (фиг.2). Он работает следующим образом. При однократном запуске генератор одиночных импульсов DA8 (фиг.2) формирует импульс с напряжением логической единицы. Генератор одиночных импульсов DA8 (фиг.2) построен по схеме одновибратора на операционном усилителе. При отсутствии внешнего управляющего импульса по неинвертирующему входу схема обладает устойчивым состоянием. Напряжение на выходе схемы меньше напряжения логического нуля. С приходом кратковременного внешнего управляющего импульса на неинвертирующий вход потенциал этого входа становится положительным, и операционный усилитель DA8 (фиг.2) переходит в новое состояние. На выходе схемы напряжение становится равным напряжению логической единицы. Это состояние будет неустойчивым, потому что с этого момента начинается зарядка конденсатора С11 по цепи R30, С11, корпус (фиг.2). В процессе зарядки конденсатора С11 напряжение на инвертирующем входе возрастает. В момент времени, когда напряжение на инвертирующем входе превысит напряжение на неинвертирующем входе, операционный усилитель DA8 (фиг.2) возвращается в исходное состояние. Напряжение на его выходе становится меньше напряжения логического нуля. При этом конденсатор С11 быстро разряжается до нуля по цепи R30, выход операционного усилителя DA8 (фиг.2). Это состояние будет устойчивым до тех пор, пока не появится очередной управляющий импульс.

Импульс с выхода генератора одиночных импульсов DA8 (фиг.2) поступает на вход счетчика DD27,DD28 (фиг.2) и переводит его из нулевого состояния в единичное. Информация о состоянии счетчика DD27, DD28 (фиг.2) снимается по восьмиразрядной шине и поступает на адресные входы запоминающего устройства 22 (фиг.1). При повторных запусках генератора одиночных импульсов DA8 (фиг.2) счетчик DD27.DD28 (фиг.2) производит подсчет импульсов и изменяет свое состояние. Таким образом, происходит пошаговый просмотр содержимого памяти.

Предлагаемое изобретение по сравнению с прототипом и другими известными техническими решениями имеет следующие преимущества:

- обеспечение возможности совмещения устройств для измерения амплитуды и длительности импульсов напряжения;

- расширение функциональных возможностей измерителей;

- обеспечение возможности автоматизации процесса измерения;

- обеспечение возможности проведения измерений в сетях электропитания с переменным напряжением;

- обеспечение возможности измерения высоких уровней импульсных возмущений;

- повышение производительности труда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для контроля черно-белого изображения | 1983 |

|

SU1282358A1 |

| Цифроаналоговая система сбора и обработки информации | 1986 |

|

SU1363271A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ НАПРЯЖЕНИЯ | 1990 |

|

RU2018147C1 |

| МНОГОКАНАЛЬНЫЙ ПАНОРАМНЫЙ ПРИЕМНИК | 1996 |

|

RU2115997C1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

Изобретение относится к электроизмерительной технике и предназначено для измерения параметров коротких импульсных возмущений в сетях электропитания с переменным напряжением. Технический результат - совмещение возможностей устройств для измерения амплитуд и длительностей импульсов напряжения с целью их совместного одновременного использования и расширение функциональных возможностей измерителей. Совмещение возможностей устройств для измерения амплитуд и длительностей импульсов напряжения обеспечивается введением в канал с минимальным порогом амплитудного анализатора схемы анализатора длительности. Необходимость расширения функциональных возможностей обусловлена случайным характером паразитных импульсных возмущений в сетях электропитания с переменным напряжением, большим разбросом амплитуд паразитных импульсных возмущений, наложением их на переменное напряжение первичной сети электропитания, и обеспечивается введением в схему амплитудного анализатора пороговых устройств, созданием возможности хранения информации о параметрах импульсных возмущений и вывода информации из устройства памяти по окончании цикла измерения. Прибор для измерения параметров паразитных импульсных возмущений в сетях электропитания с переменным напряжением состоит из схем амплитудного анализатора, содержащего N пороговых устройств 1.1, ..., 1.К, ..., 1.N, N компараторов 2.1, ..., 2.К, ..., 2.N, N+1 дифференцирующие цепочки R1C1, ..., RkCk, ..., R.NC.N, R1.2C1.2, N элементов И 3.1, ..., 3.N, N канальных счетчиков 4.1, ... 4.К, ..., 4.N, элемент ИЛИ-НЕ 5, триггер 6, с раздельным запуском, электронный коммутатор 7 амплитудного анализатора со схемой управления 8, дешифратор 9 амплитудного анализатора, устройство 10 отображения информации и схему индикации 11; схемы анализатора длительности, включающего последовательный двухтактный интегратор 12, элемент И 13, генератор стробирующих импульсов 14, счетчик 15 стробирующих импульсов со схемой предварительного обнуления, состоящей из дифференцирующей цепочки R2.1C2.1, электронный коммутатор 16 анализатора длительности со схемой управления 17, дешифратор 18 анализатора длительности и устройство 19 отображения информации; блока памяти, включающего шифратор адреса считывания 20, шифратор адреса записи 21, запоминающее устройство 22, электронный коммутатор 23 шины адреса, и схему управления 16 для записи и считывания информации о параметрах каждого из зарегистрированных импульсов и вывода данной информации на устройство отображения. 3 ил.

Прибор для измерения параметров паразитных импульсных возмущений в сетях электропитания с переменным напряжением, состоящий из схем амплитудного анализатора, содержащего N компараторов, N+1 дифференцирующие цепочки, N элементов И, триггер с раздельным запуском и элемент ИЛИ-НЕ, при этом импульс с выхода каждого элемента И поступает на вход элемента ИЛИ-НЕ, с выхода которого импульс поступает на R-вход триггера, напряжение с выхода первого компаратора через дифференцирующую цепочку поступает на S-вход триггера, Q-выход которого соединен со вторыми входами всех элементов И, сигналы с выходов компараторов напряжения через дифференцирующие цепочки поступают на соответствующие элементы И, отличающийся тем, что он дополнительно снабжен анализатором длительности и блоком памяти, при этом в схему амплитудного анализатора дополнительно введены пороговые устройства, состоящие из включенного между фазным и нулевым проводами первичной сети симметричного полупроводникового ограничителя напряжения с порогом срабатывания, соответствующим порогу ограничения (регистрации) данного канала, делителя напряжения, состоящего из включенных последовательно двух резисторов, и диодного моста, анодный вывод которого соединен с соответствующим компаратором схемы амплитудного анализатора, N канальных счетчиков, электронный коммутатор амплитудного анализатора со схемой управления, дешифратор амплитудного анализатора, устройство отображения информации и схема индикации, при этом импульс с выхода каждого элемента И поступает на вход соответствующего канального счетчика и на вход схемы индикации, информация с выхода канальных счетчиков поступает на вход электронного коммутатора амплитудного анализатора, управляющий вход которого подключен к выходу схемы управления, и с выхода которого информация через дешифратор амплитудного анализатора поступает на устройство отображения информации, причем анализатор длительности включает последовательный двухтактный интегратор, элемент И, генератор стробирующих импульсов, счетчик стробирующих импульсов со схемой предварительного обнуления, состоящей из дифференцирующей цепочки, электронный коммутатор анализатора длительности со схемой управления, дешифратор анализатора длительности и устройство отображения информации, при этом импульс с выхода первого компаратора поступает на вход последовательного двухтактного интегратора, с выхода которого сигнал поступает на второй вход элемента И, на первый вход которого поступают импульсы с генератора стробирующих импульсов, с выхода элемента И импульсы поступают на вход счетчика стробирующих импульсов, при этом с выхода первого компаратора импульс поступает на схему предварительного обнуления, представляющую собой дифференцирующую цепочку, с выхода которой импульс поступает на обнуляющий вход счетчика стробирующих импульсов, с выхода которого информация поступает на первый вход электронного коммутатора анализатора длительности, на управляющий вход которого поступает управляющий сигнал со схемы управления, при этом информация с выхода электронного коммутатора анализатора длительности через дешифратор анализатора длительности поступает на устройство отображения, а блок памяти состоит из шифратора адреса считывания, шифратора адреса записи, запоминающего устройства, электронного коммутатора шины адреса и схемы управления, при этом импульс с выхода элемента И поступает на вход шифратора адреса записи, с выхода которого адрес ячейки памяти поступает на первый вход электронного коммутатора шины адреса, на второй вход которого поступает адрес с шифратора адреса считывания, а на управляющий вход поступает управляющий сигнал со схемы управления, с выхода электронного коммутатора шины адреса адрес подается на адресные входы запоминающего устройства, а на информационный выход запоминающего устройства поступает информация с выхода счетчика стробирующих импульсов, при этом на управляющий вход запоминающего устройства поступает управляющий сигнал со схемы управления, а с выхода запоминающего устройства информации поступает на второй вход анализатора длительности.

| Устройство для измерения и анализа импульсных перенапряжений | 1985 |

|

SU1242839A1 |

| SU 19843822648 А, 07.06.1986 | |||

| US 6307375 В1, 23.10.2001. | |||

Авторы

Даты

2004-10-27—Публикация

2002-08-02—Подача