Изобретение относится к устройствам связи широкополосных сигналов с временным уплотнением, точки связи которых используются в режиме временного уплотнения по мере необходимости для большого количества соединений.

Известен способ соединения двух линий с помощью логического вентильного элемента, который включается и отключается выполненной в виде бистабильного опрокидывающего D-звена индивидуальной в отношении точек связи ячейки памяти, причем эта индивидуальная в отношении точек связи ячейка памяти, на тактовый вход которой подается соответствующий тактовый сигнал, работает с управлением только в одном направлении координат, а именно с управлением через ее D - вход (Пфаншмидт, "Пределы скорости работы сетей связи для широкополосных цифровых сигналов", диссертация, г. Брауншвейг, 1978, рис. 6.7 и 6.4). С учетом достигаемого при скорости передачи данных 140 Мбит/с коэффициента временного уплотнения порядка 4-8 и необходимой при этом дорогостоящей технологии в настоящее время для передачи широкополосных сигналов предпочтительными являются, конечно, устройства чисто пространственного сопряжения, в случае использования которых коммутируемые через отдельные точки соединения отделены друг от друга пространственно.

Чисто пространственное устройство связи широкополосных сигналов может быть выполнено в виде снабженной входными и выходными усилителями точечной матрицы связи в технике КМОП, в точках связи которой управление элементами связи осуществляется с помощью управляемой декодером, индивидуальной в отношении точек связи удерживающей ячейки памяти, причем элементы связи также выполнены в виде вентильных схем передачи техники КМОП (документы конференции ISS' 84 31C3, фиг.12); индивидуальные в отношении точек связи удерживающие ячейки памяти чисто пространственного многократного узла сопряжения могут управляться декодером строк и декодером столбцов по двум координатам через одну являющуюся по мере необходимости индивидуальной в отношении строк или столбцов управляющую линию (Пфаншмидт, рис. 6.4). Предусмотренные в матрице связи выходные усилители могут активироваться также в зависимости от активации (по меньшей мере) одной точки сопряжения соответствующей линии матрицы (описание заявки Франции N 365263, фиг.5).

Кроме того ("Electronics" 1983, N 1(дек), стр. 88-89) в общей форме известно предусмотрение в матрице связи широкополосных сигналов цифровых точек связи в форме инверторов с тремя состояниями, конкретная реализация которых известна, однако требует использования большого количества транзисторов.

Особо малым расходом транзисторов при конкретной реализации отдельных точек связи характеризуется (описанное в патенте ФРГ N 3604651 (VPA 86P1060) пространственное устройство связи широкополосных сигналов с матрицей точек связи на полевых транзисторах, элементы связи которой работают с управлением от управляемой декодером, индивидуальной в отношении точек связи ячейки памяти, в случае которого элементы связи образованы единственным n -канальным транзистором, нагружаемым на его затворе накопительной ячейкой потенциалом проключения, превышающим верхнее значение подлежащего проключению сигнала больше, чем на напряжение запирания, который является меньше уровня, получающегося за счет повышения нижнего (граничного) значения подлежащего проключению сигнала на напряжение запирания транзистора.

Таким образом, с уменьшенной потребностью в площади и соответственно меньшей емкостью схемы (что особенно важно при интеграции) можно реализовать предусмотренные в матрице точек связи, управляемые несложным образом с помощью индивидуальной в отношении точек связи удерживающей ячейки памяти элементы связи при минимальном количестве транзисторов, без использования инверторов и без предусматриваемого в вентильной схеме передачи техники КМПО и нуждающегося в существенной установочной площади вследствие его высокого удельного сопротивления p-канального транзистора.

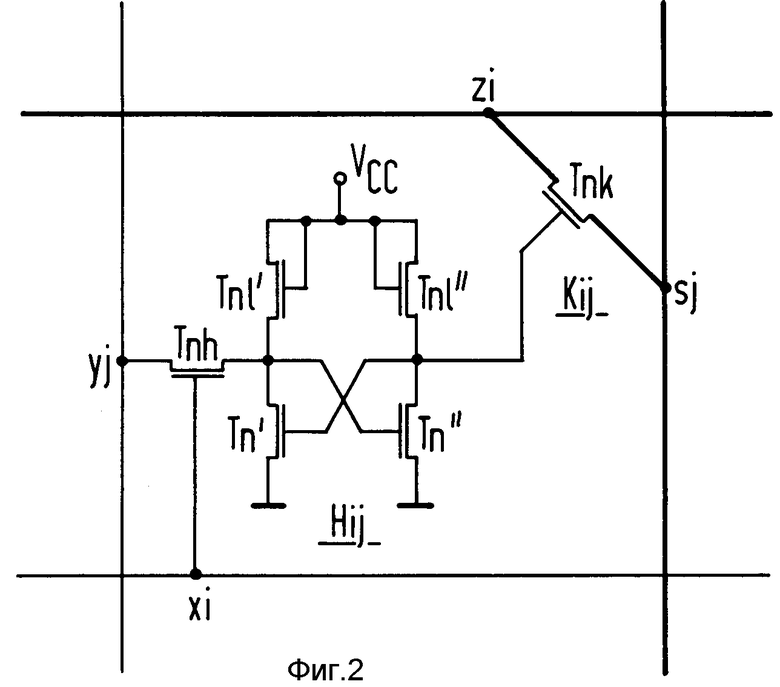

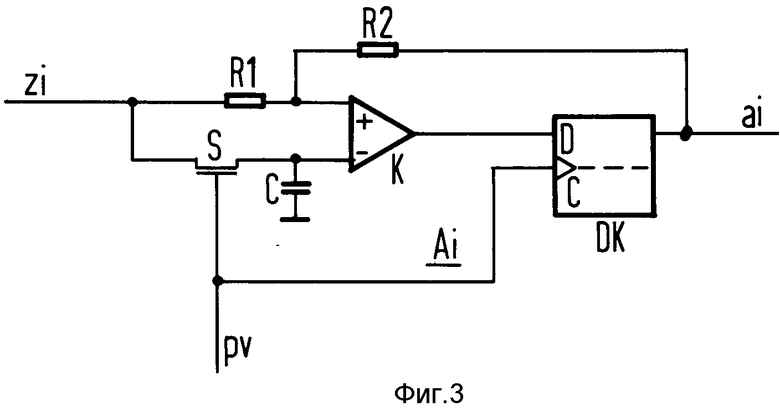

Дополнительное уменьшение размеров схемы и, следовательно, необходимой площади для такой точки сопряжения обеспечивается при использовании управляемой по двум координатам (декодер строк, декодер столбца), индивидуальной в отношении точек связи ячейки памяти, которая образована n-канальным транзистором и двумя инвертирующими схемами с перекрестной связью, одна из которых на стороне входа соединена с соответствующим выходом управляющего декодера через n -канальный транзистор, который в свою очередь принимает на свой управляющий электрод выходной сигнал с соответствующего выхода другого управляющего декодера, а другая подключена на стороне выхода к управляющему входу соответствующего элемента связи.

Такое предложенное пространственное устройство связи широкополосных сигналов, снабженное, например, матрицей точек связи на полевых транзисторах с 64 входами и 32 выходами, может использоваться для коммутации любых асинхронных сигналов со скоростью передачи данных до 170 Мбит/с и, таким образом, заполняющего т. н. канал H4 сигнала (приблизительно 140 Мбит/с) по мере необходимости между одним входом и одним выходом (или при обслуживании распределительных служб - также несколькими выходами). Вследствие этого возникает требование к обеспечению возможности передачи не только всего канала 4H в целом, но также и вспомогательных каналов, например, так называемых каналов H3 для сигналов, передаваемых с (приблизительной) скоростью 34 Мбит/с. Такая передача вспомогательных каналов может быть в принципе достигнута с помощью разбивающих тот или иной канал (H4) на его вспомогательные каналы (H3) демультиплексоров перед устройством связи и вновь объединяющих вспомогательные каналы в один канал мультиплексоров, включенных после устройства связи, причем само устройство связи обеспечивает передачу отдельных вспомогательных каналов; это предполагает, конечно, соответствующее умножение входов и выходов матрицы точек связи, которая вместо первоначально указанных в примере 256 х 32 точек связи должна содержать в данном случае, например, 256 х 128 точек связи. При этом требование к полной способности матрицы использоваться в интересах распределенных служб одновременно обуславливает возникновение проблемы, суть которой заключается в том, что каждый из (например, 256) входов такого рода матрицы точек связи должен одновременно отличаться возможностью нагружения всеми выходами матрицы точек сопряжения (например, 128). Это потребовало бы использования 256 входных задающих схем с чрезмерным объемом, уравнительные токи и мощность потерь которых в результате этого существенно усложнили бы возможность реализации такого модуля матрицы точек связи.

Целью изобретения является создание способа и устройства для коммутации широкополосных сигналов, которые могут удовлетворять выше указанным требованиям без появления каких-либо затруднений.

В способе коммутации широкополосных сигналов матрицей связи на полевых транзисторах, который заключается в подведении сигналов к соответствующей вертикали матрицы, проключении определенного элемента коммутации и снятии сигнала с соответствующей усилительной схемы горизонтали матрицы, эта задача решается согласно изобретению за счет того, что время проключения элемента коммутации разделяют на предварительную фазу (pV) и фазу коммутации (ph), при этом во время предварительной фазы запоминают мгновенное значение сигнала на горизонтали матрицы, а во время фазы коммутации формируют разностный сигнал между сигналом, установившимся на горизонтали, и запомненным сигналом.

В устройстве коммутации широкополосных сигналов, содержащем матрицу коммутации, причем каждая точка коммутации содержит элемент коммутации, включенный между соответствующей вертикалью и горизонталью матрицы точек коммутации, при этом горизонтали матрицы точек коммутации соединены с входами соответствующих выходных усилителей, эта задача решается согласно изобретению за счет того, что выходные усилители содержат последовательно соединенные компаратор и накопительный элемент, при этом первый вход компаратора соединен с соответствующей горизонталью и первым выводом переключателя, второй вывод которого соединен с первым выводом накопителя потенциала и вторым входом компаратора, второй вывод накопителя потенциала заземлен, а управляющий вход переключателя соединен с тактовым входом накопительного элемента и линией тактового сигнала, при этом сопротивление элементов коммутации больше, чем входной сопротивление вертикалей матрицы.

В этом месте следует отметить, что (как следует из описания изобретения к патенту США N 3938049, фиг.11) для корректировки базиса амплитуды в оптоэлектронном устройстве считывания известен способ, в соответствии с которым выработанный при считывании сигнал поступает непосредственно на один вход и через замкнутый в течение "темного" периода и вновь размыкаемый незадолго до конца этого периода переключатель с последующим удерживающим конденсатором подводится к другому входу дифференциального усилителя.

При этом не рассматривались проблемы целесообразного использования устройства связи широкополосных сигналов, которые решаются изобретением.

Изобретение отличается тем преимуществом, что уже одного размаха сигнала, который еще не является чрезмерным требованием ко входным задающим схемам и их поперечным токам и мощности потерь, и обусловленного этим незначительного изменения заряда ведущего к блоку сравнения участка линии достаточно для того, чтобы привести на том или ином выходе блока сравнения (который в следующей форме исполнения изобретения работает с использованием эффекта гистерезиса) и, следовательно, на участке проходящей от него выходной линии к однозначному переходу цифрового сигнала из одного состояния в другое.

Запоминающее звено может быть образовано в следующей форме конструктивного исполнения изобретения релаксационным звеном D, на тактовый вход которого подается тактовая частота коммутации поля сопряжения.

Дальнейшие особенности изобретения вытекают из последующего более подробного описания изобретения, поясняемого на основании фигур.

Фиг. 1 и 2 показывают схему устройства связи широкополосных сигналов с его точками связи; фиг. 3 - подробности технической реализации устройства в соответствии с изобретением.

На фиг. 1 схематически и в необходимом для понимания изобретения объеме изображено устройство связи широкополосных сигналов, на ведущих к линиям Si. . .Sj...Sn столбцов матрицы точек связи выходах l1...lj...ln которого предусмотрены входные задающие схемы E1...Ej...En, и их проходящие от линий Z1... Zi. . . Zm строк матрицы точек связи выходы a1...ai...am оснащены выходными усилительными схемами A1...Ai...Am. Матрица точек связи содержит точки КР11. ..КРij...КРmn связи, элементы связи которых, как это показано более подробно для точки КРij связи применительно к его элементу Kij связи, работают с управлением от индивидуальной в отношении точек связи удерживающей ячейки Hij памяти (применительно к точке KPij связи), выход которой подключен к управляющему входу того или иного элемента связи (Kij применительно к точке связи KPij).

Управление удерживающими ячейками ... Hij... памяти осуществляется в соответствии с фиг. 1 при помощи двух управляющих декодеров, а именно декодера DX строк и декодера DY столбцов по двум координатам через соответствующие управляющие линии Y1...Yj...Yn.

С этой целью, как это видно из изображенного на фиг. 1, оба управляющих декодера DX, DY могут нагружаться поступающим от входных регистров Reg X, Reg Y общим для ряда матриц (строка или столбец) точек связи адресом строк точек связи или столбцов точек связи, по которому они по мере необходимости применительно к тому или иному адресу рядов точек связи соответствующей управляющей линии выдают управляющий сигнал 1. Поступление управляющего сигнала 1 строк и управляющего сигнала 1 столбцов в точку пересечения соответствующей строки матрицы с соответствующим столбцом матрицы при установлении соответствующего соединения обуславливает после этого активацию находящейся там удерживающей ячейки памяти, например, удерживающей ячейки Hij памяти, в результате чего управляемый соответствующей удерживающей ячейкой (Hij) памяти элемент связи, например элемент Kij связи, переходит в проводящее состояние.

Для того чтобы обеспечить повторное запирание рассматривающегося в примере элемента связи при установлении соответствующего соединения, управляющий декодер DX нагружается в свою очередь от входного регистра Reg X соответствующим адресом строки, так что декодер DX строк выдает в свою выходную линию Xi сигнал 1 управления строками и одновременно декодер DY столбцов нагружается со своего выходного регистра Reg Y, например, холостым адресом или адресом столбца некоммутированных точек связи, в результате чего он выдает в свою исходную линию управляющий сигнал 1 управления строками, и сигнал О управления столбцами обуславливает после этого сброс удерживающей ячейки Hij памяти, в результате чего блокируется управляемый ею элемент Kij связи.

Как видно из фиг. 2, управляемая с помощью обоих управляющих декодеров (декодер DX строк и декодер DY столбцов) на фиг. 1 по двум координатам ячейка Hij памяти может быть образована n - канальным транзистором Tnh и двумя перекрестно связанными инвертирующими схемами  , Tn1; Tn", Tn1", одна из которых (

, Tn1; Tn", Tn1", одна из которых ( , Tn1') соединена на стороне входа с соответствующим выходом Ji управляющего декодера (DY на фиг. 1) через n - канальный транзистор Tnh, который в свою очередь принимает на свой управляющий электрод выходной сигнал соответствующего выхода Х другого управляющего декодера (DX на фиг. 1), в том время как другая из двух перекрестно связанных инвертирующих схем подключена на стороне выхода к управляющему входу соответствующего элемента Kij связи.

, Tn1') соединена на стороне входа с соответствующим выходом Ji управляющего декодера (DY на фиг. 1) через n - канальный транзистор Tnh, который в свою очередь принимает на свой управляющий электрод выходной сигнал соответствующего выхода Х другого управляющего декодера (DX на фиг. 1), в том время как другая из двух перекрестно связанных инвертирующих схем подключена на стороне выхода к управляющему входу соответствующего элемента Kij связи.

Элемент Kij связи может быть образован, например, с задающим каскадом с тремя состояниями, или, как это видно также из изображенного на фиг. 2, единственным n - канальным транзистором Tnk, нагружаемым на его затворе потенциалом проключения, превышающим верхнее (граничное) значение подлежащего проключению между линией столбцов (входная линия) Sj и линией строк (выходная линия) Zi сигнала, больше чем на напряжение запирания транзистора (уровень H) или соответственно потенциалом запирания (уровень L), который меньше уровня, получающегося за счет повышения нижнего (граничного) значения подлежащего проключению между линией столбцов (входная линия) Sj и линией строк (выходная линия) Zi сигнала на напряжение запирания транзистора. Такие способы реализации удерживающей ячейки Hij памяти и элемента Kij связи описываются уже в другом источнике (патент ФРГ N 36046051), так что отпадает необходимость в дальнейшем пояснении. Наконец, важно то, что сопротивление пропускания такого элемента связи является большим по сравнению с действующим в линии столбцов матрицы внутренним сопротивлением предусмотренной там входной задающей схемы Ej (на фиг.1), что может быть легко реализовано за счет соответствующего исполнения геометрии транзистора.

На фиг. 1 дополнительно указано, что к выходам декодера DY столбцов подключены переключатели WR записи, которые могут подключаться к линии деблокирования только при поступлении команды записи, а затем коммутировать возникающий при необходимости на выходе декодера управляющий сигнал 1 уровень 1 и возникающие на прочих выходах декодера управляющие сигнала O (уровень Н) по отдельным управляющим линиям Y1..., Yj',..., Yn, в результате чего уже описанным образом те или иные управляемые элементы связи переходят в состояние коммутации или блокировки.

Если, напротив, возникает необходимость исключительно в выводе состояния связи одной строки точек связи матрицы точек связи, для чего соответствующая управляющая линия строк, например, линия xi, в свою очередь - аналогично случаю установления или его устранения - нагружается управляющим сигналом 1 (уровень H), то в этом случае переключатели WR записи остаются разомкнутыми вследствие отсутствия возникающей в линии Wr деблокирования команды записи, в результате чего в линии Y1...Yj,...Yn от декодера DY столбцов не поступает более управляющего потенциала. Через упомянутые уже деблокированные вследствие поступления управляющего сигнала H строк на затвор n - канальных транзисторов Tnh (фиг. 2) удерживающих ячеек Hij соответствующих строк ... Крij. .. точек сопряжения непосредственно существующее в удерживающей ячейке Hij памяти состояние сигнала может переключаться на ту или иную управляющую линию столбцов Yj (на фиг.2), причем при правильной работе не более, чем в одной управляющей линии yj...Yj,...Yn столбцов на фиг. 1 может возникать потенциал 1. Как указано также на фиг.1, адрес этой управляющей линии столбцов и, следовательно, адрес соответствующей точки сопряжения могут вырабатываться с помощью кодирующего устройства с Z и передаваться от него на следующий регистр Reg Z.

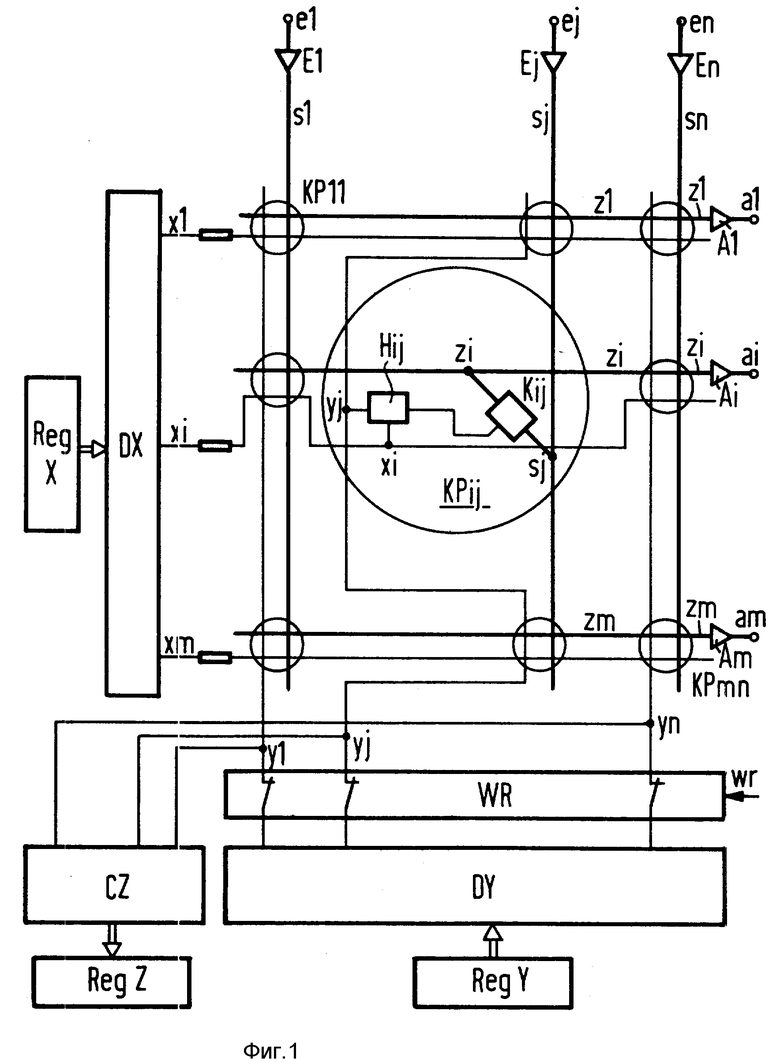

Предусмотренная между линией Zi строк на фиг. 1 и 2 и последующим выходам ai (на фиг. 1) матрицы точек сопряжения выходная усилительная схема Ai (фиг. 1) содержит, как это уже пояснялось на фиг. 3, введенную между соответствующими участками выходных линий Ziи ai каскадную схему (реализованного в соответствии с фиг. 3 с дифференциальным усилителем) блока K сравнения и (образованного в случае примера исполнения по фиг. 3C с использованием опрокидывающего звена 1 K с управлением по фронту) запоминающего звена, а также схему "Sample-and Hold" с образованной на фиг. 3 конденсатором удерживающей памятью C и с выполненным в соответствии с фиг. 3 на транзисторе техники МОП переключателем, которые соединяют проходящий от соответствующих элементов .. . Kij ... связи на фиг. 1 и 2 к одному входу (+) блока сравнения участок выходной линии Zi с другим входом (-) блока сравнения; сопротивление пропускания транзисторного переключателя может быть при этом меньше сопротивления пропускания элемента Kij связи (на фиг. 1 и 2), управляющий электрод транзистора переключателя подключен вместе с тактовым входом C опрокидывающего D - звена DK к тактовой линии pv, в которую может поступать тактовая частота, подразделяющая период времени коммутации двоичного разряда на предварительную фазу и основную фазу.

В течение времени действия предварительной фазы транзистор переключателя находится в проводящем состоянии, так что удерживающая память C заряжается до потенциала, который в данный момент времени действует в линии Zi строк матрицы. Входная задающая схема Ej (на фиг. 1) может переключаться в течение этой предварительной фазы в состояние покоя (три устойчивых состояния) или также создать на ее выходе потенциал, соответствующий подлежащему переключению двоичному разряду.

В течение следующей основной фазы, в течение которой транзистор S переключателя заперт, удерживаемый удерживающей памятью C потенциал сохраняется на названном следующем входе (-) блока сравнения, в то время как одновременно от соответствующей линии Sj столбцов (на фиг. 1 и 2) через элемент Kij (на фиг.1 и 2) связи ведущая к названному входу (+) блока K сравнения линия строк матрицы продолжает заряжаться до потенциала, соответствующего коммутируемому тем самым двоичному разряду. При этом уже небольшого изменения заряда линии Zi строк матрицы достаточно для того, чтобы обусловить при необходимости на выходе блока сравнения (вход D опрокидывающегося D - звена DK) однозначный переход цифрового сигнала из одного состояния в другое, которое затем в конце фазы коммутации принимается с фронтом тактовых импульсов от опрокидывающего D - звена DK и, следовательно, присутствует на выходе ai устройства сопряжения; элемент Kij связи (на фиг. 1 и 2) может по этой причине, как уже было сказано выше, быть выполнен с относительно высоким сопротивлением пропускания.

Как уже было отменено выше, блок K сравнения работает в целесообразном случае с использованием эффекта гистерезиса, который достигается в случае примера исполнения по фиг. 3 с помощью содержащей сопротивления R1, R2 схемы положительной обратной связи. С помощью такого гистерезиса блока K сравнения обеспечивает нормальную коммутацию цифровых сигналов даже в том случае, если в цифровом сигнале возникают весьма длительные последовательности одного и того же двоичного разряда, так что с течением времени потенциал на участке выходной линии достигает соответствующего этому двоичному разряду полного уровня сигнала, а затем между обоими входами блока сравнения не сохраняется более разности потенциалов, которая присутствует до этого момента также при поочередном следовании одних и тех же двоичных разрядов сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2106755C1 |

| УСТРОЙСТВО СВЯЗИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2013877C1 |

| ШИРОКОПОЛОСНОЕ УСТРОЙСТВО КОММУТАЦИИ | 1991 |

|

RU2103841C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2103832C1 |

| Устройство коммутации широкополосных сигналов | 1989 |

|

SU1838888A3 |

| УСТРОЙСТВО ПРОСТРАНСТВЕННОЙ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1986 |

|

RU2011304C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2105430C1 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1738105A3 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1991 |

|

RU2105431C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1986 |

|

RU2098922C1 |

В устройстве коммутации широкополосных сигналов с оснащенной входными задающими схемами и выходными усилительными схемами матрицей точек связи на полевых транзисторах предусмотрены элементы связи с относительно большим сопротивлением пропускания; выходные усилительные схемы содержат по одной каскадной схеме работающего с использованием явления гистерезиса блока сравнения и опрокидывающего D - звена, а также удерживающую память и переключатель, через который по мере надобности в течение предварительной фазы периода времени коммутации двоичных разрядов удерживающая память перезаряжается по меньшей мере приблизительно до потенциала, мгновенно действующего на отходящем от элемента связи участке выходной линии, который затем в течение последующей фазы переключения сохраняется на втором входе блока сравнения. 2 с.и 1 з.п. ф-лы 3 ил.

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1998-02-20—Публикация

1987-06-09—Подача