(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации м-последовательности с инверсной модуляцией | 1974 |

|

SU702534A1 |

| Устройство для синхронизации псевдослучайных сигналов | 1975 |

|

SU553754A1 |

| Устройство для поиска псевдослучайного сигнала по задержке | 1974 |

|

SU492883A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| Устройство синхронизации источников сейсмических сигналов | 1981 |

|

SU972428A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| РЕЛЕЙНЫЙ КОРРЕЛЯТОР | 1973 |

|

SU374610A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

| Устройство для кодирования и декодирования циклических кодов | 1985 |

|

SU1302440A1 |

Изобретение относится к устройствам дискретной обработки информации и может быть использовано в связных и радиолокационных системах различного назначения, модулирующий сигнал которых представляет собой линейную двоичную последовательность.

Известно устройство синхронизации генератора М-последовательности, содержащее коррелятор и регистр сдвига с обратной связью через сумматор по модулю два.

Из известных устройств наиболее близким по технической сущности является устройство для передачи информации, содержащее регистр сдвига, выход которого подключен к первому входу сумматора, второй вход которого соединен с первым выходом переключателя, второй выход первого переключателя подключен к одному из входов счетчика и входу коррелятора, третий выход переключателя .подключен к одному из ВхХодов регистра, другие входы которого подсоединены к выходам второго переключателя, блок управления, соединены с выходом счетчика, другой вход которого соединен с выходом сумматора через элемент ИЛИ-НЕ.

Увеличение уровня шума приводит к увеличению длины запоминаемого отрезка. Например, если число символов , то для исправления 7-10 ошибок требуется анализировать отрезок последовательности .

Другое препятствие, которое возникает при реализации этой схемы, заключается в том, что регистр сдвига для запоминания / символов должен иметь много отводов. Последнее

обстоятельство сильно затрудняет использование унифицированных больших интегральных регистров, которые, как правило, имеют мало выводов. Целью изобретения является повышение помехоустойчивости устройства.

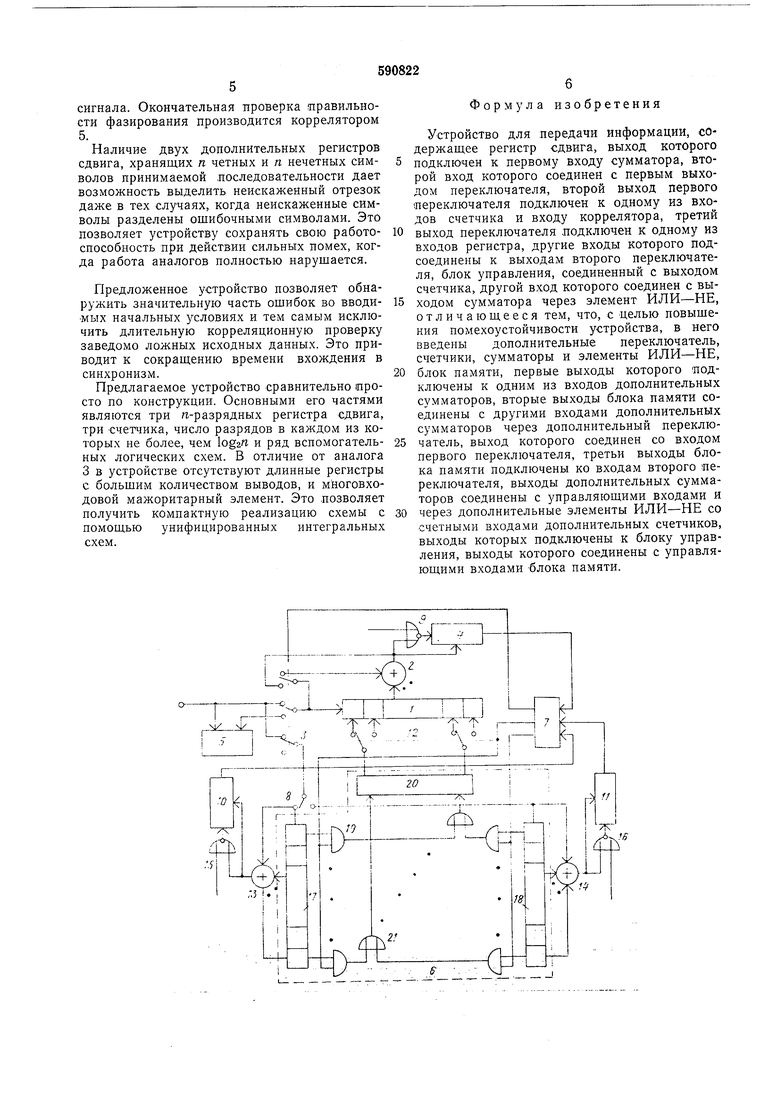

Поставленная цель достигается тем, что в устройство введены дополнительные переключатель, счетчики, сумматоры и элементы ИЛИ-НЕ, блок памяти, первые выходы которого подключены к одним из входов дополнительных сумматоров, вторые выходы блока памяти соединены с другими входами дополнительных сумматоров через дополнительный переключатель, выход которого соединен со

входом первого .переключателя, третьи выходы блока памяти подключены ко входам второго переключателя, выходы дополнительных сумматоров соединены с управляющими входами и через дополнительные элементы

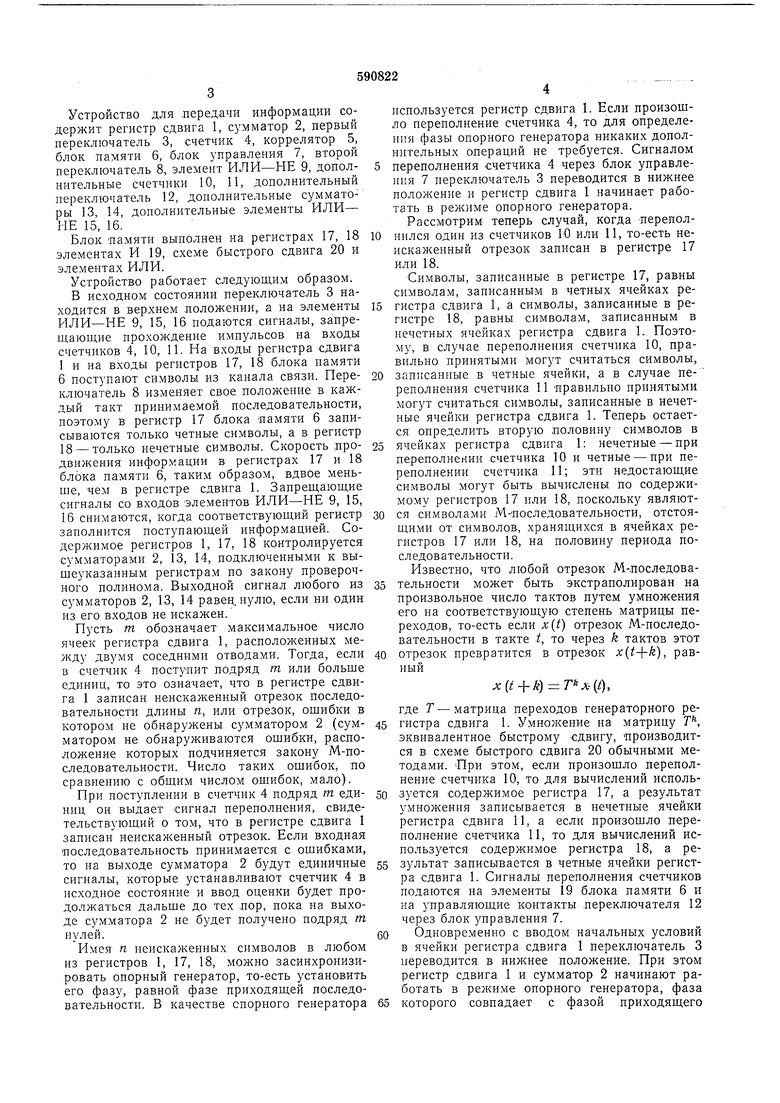

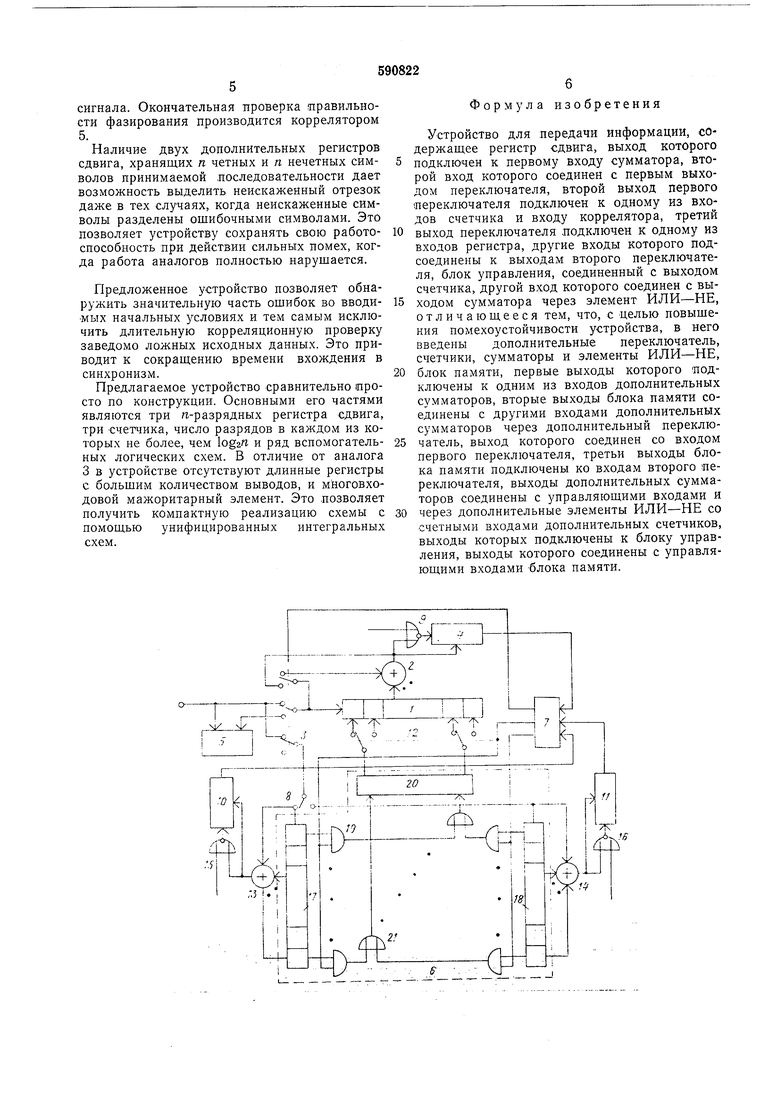

ИЛИ-НЕ со счетными входами дополнительных счетчиков, выходы которых подключены к блоку управления, выходы которого соединены с управляющими входами блока памяти. На чертеже приведена блок-схема устройства.

Устройство для .передачи информации содержит регистр сдвига 1, сумматор 2, первый переключатель 3, счетчик 4, коррелятор 5, блок памяти 6, блок управления 7, второй переключатель 8, элемент ИЛИ-НЕ 9, дополнительные счетчики 10, 11, дополнительный переключатель 12, дополнительные сумматоры 13, 14, дополнительные элементы ИЛИ- НЕ 15, 16.

Блок памяти выполнен на регистрах 17, 18 элементах И 19, схеме быстрого сдвига 20 и элементах ИЛИ.

Устройство работает следующим образом.

В исходном состоянии переключатель 3 находится в верхнем .положении, а на элементы ИЛИ-НЕ 9, 15, 16 подаются сигналы, запрещающие прохождение импульсов на входы счетчиков 4, 10, 11. На входы регистра сдвига 1 и на входы регистров 17, 18 блока памяти 6 поступают символы из канала связи. Переключатель 8 изменяет свое положение в каждый такт принимаемой последовательности, поэтому в регистр 17 блока памяти 6 записываются только четные символы, а в регистр 18 - только нечетные символы. Скорость .продвижения информации в регистрах 17 и 18 блока памяти 6, таким образом, вдвое меньше, чем в регистре сдвига 1. Запрещающие сигналы со входов элементов ИЛИ-НЕ 9, 15, 16 снимаются, когда соответствующий регистр заполнится поступающей информацией. Содерл имое регистров 1, 17, 18 контролируется сумматорами 2, 13, 14, подключенными к выщеуказанным регистрам по закону проверочного полинома. Выходной сигнал любого из сумматоров 2, 13, 14 равен, нулю, если ни один из его входов не искажен.

Пусть т обозначает максимальное число ячеек регистра сдвига 1, расположенных между двумя соседними отводами. Тогда, если в счетчик 4 постз.пит подряд т или больще единиц, то это означает, что в регистре сдвига 1 за.писан неискаженный отрезок последовательности длины п, или отрезок, ощибки в котором не обнаружены сумматором 2 (сумматором не обнаруживаются ошибки, расположеиие которых подчиняется закону М-последовательности. Число таких ошибок, по сравнению с общим числом ощибок, мало).

При поступлении в счетчик 4 подряд т единиц он выдает сигнал переполнения, свидетельствующий о том, что в регистре сдвига 1 записан неискаженный отрезок. Если входная последовательность принимается с ошибками, то на выходе сумматора 2 будут единичные сигналы, которые устанавливают счетчик 4 в исходное состояние и ввод оценки будет продолжаться дальше до тех .пор, пока на выходе сумматора 2 не будет получено подряд т нулей.

Имея п неискалсенных символов в любом из регистров 1, 17, 18, можно засиихронизировать опорный генератор, то-есть установить его фазу, равной фазе приходящей последовательности. В качестве спорного генератора

используется регистр сдвига 1. Если произошло переполнение счетчика 4, то для определения фазы опорного генератора никаких дополнительных операций не требуется. Сигналом переполнения счетчика 4 через блок управления 7 переключатель 3 переводится в нижнее полол ение и регистр сдвига 1 начинает работать в опорного генератора.

Рассмотрим теперь случай, когда переполнился один из счетчиков 10 или 11, то-есть неискаженный отрезок записан в регистре 17 или 18.

Символы, записанные в регистре 17, равны символам, записанным в четных ячейках регистра сдвига 1, а символы, за.писанные в регистре 18, равны символам, записанным в нечетных ячейках регистра сдвига 1. Поэтому, в случае переполнения счетчика 10, правильно принятыми могут считаться символы, записанные в четные ячейки, а в случае переполнения счетчика 11 правильно принятыми могут считаться символы, записанные в нечетные ячейки регистра сдвига 1. Теперь остается определить вторую .половину символов в ячейках регистра сдвига 1: нечетные - при переполнении счетчика 10 и четные - при переполнении счетчика 11; эти недостающие символы могут быть вычислены по содержимому регистров 17 пли 18, поскольку являются символами М-последовательности, отстоящими от символов, хранящихся в ячейках регистров 17 или 18, на половину периода последовательности.

Известио, что любой отрезок М-.последовательности может быть экстраполирован на произвольное число тактов путем умножения его на соответствующую степень матрицы переходов, то-есть если x.(t отрезок М-последовательности в такте t, то через k тактов этот отрезок превратится в отрезок x(), равиый

x(t+k) T(t,

где Т - матрица переходов генераторного регистра сдвига 1. Умнол ение на матрицу Г , эквивалентное быстрому сдвигу, производится в схеме быстрого сдвига 20 обычными методами. При этом, если произошло переполнение счетчика 10, то для вычислений используется содержимое регистра 17, а результат умножения записывается в нечетные ячейки регистра сдвига И, а если произошло переполнение счетчика 11, то для вычислений используется содержимое регистра 18, а результат записывается в четные ячейки регистра сдвига 1. Сигналы переполнения счетчиков подаются на элементы 19 блока памяти 6 и на управляющие контакты .переключателя 12 через блок управления 7.

Одновременно с вводом начальных условий в ячейки регистра сдвига 1 переключатель 3 переводится в нижнее положение. При этом регистр сдвига 1 и сумматор 2 начинают работать в .ме опорного генератора, фаза которого совпадает с фазой приходящего

Авторы

Даты

1978-01-30—Публикация

1974-11-29—Подача