1

Изобретение относится к специализированным средствам цифровой вычислительной техники и может быть использовано для вычисления релейных взаимных и автокорреляционных функций случайных процессов, представленных частотно-модулированными сигналами.

Известные устройства для вычисления релейных корреляционных функций случайных процессов, представленных частотно-модулированными сигналами, содержащие счетчик малой емкости, генератор импульсов, сдвиговый регистр, реверсивные счетчики, не позволяют получить первую точку корреляционной функции, так как информация о знаке и величине частотного сигнала поступает на вход первого реверсивного счетчика со сдвигом на шаг задержки. Кроме того, в известных устройствах используются реверсивные счетчики, которые вносят погрешность, так как в них происходит потеря информации при совпадении счетных импульсов на входах реверсивных счетчиков с моментами изменения направления счета.

Для повышения точности в предлагаемом устройстве входные логические элементы «И соединены с первым выходом тактового триггера, второй выход которого подключен к логическому двоичному умножителю, две группы входов которого соединены соответственно с триггерами первого счетчика и с триггерами делителя частоты, а два выхода умножителя подключены к одному из входов четных и нечетных логических элементов «И, соединенных вторыми входами с регистром сдвига.

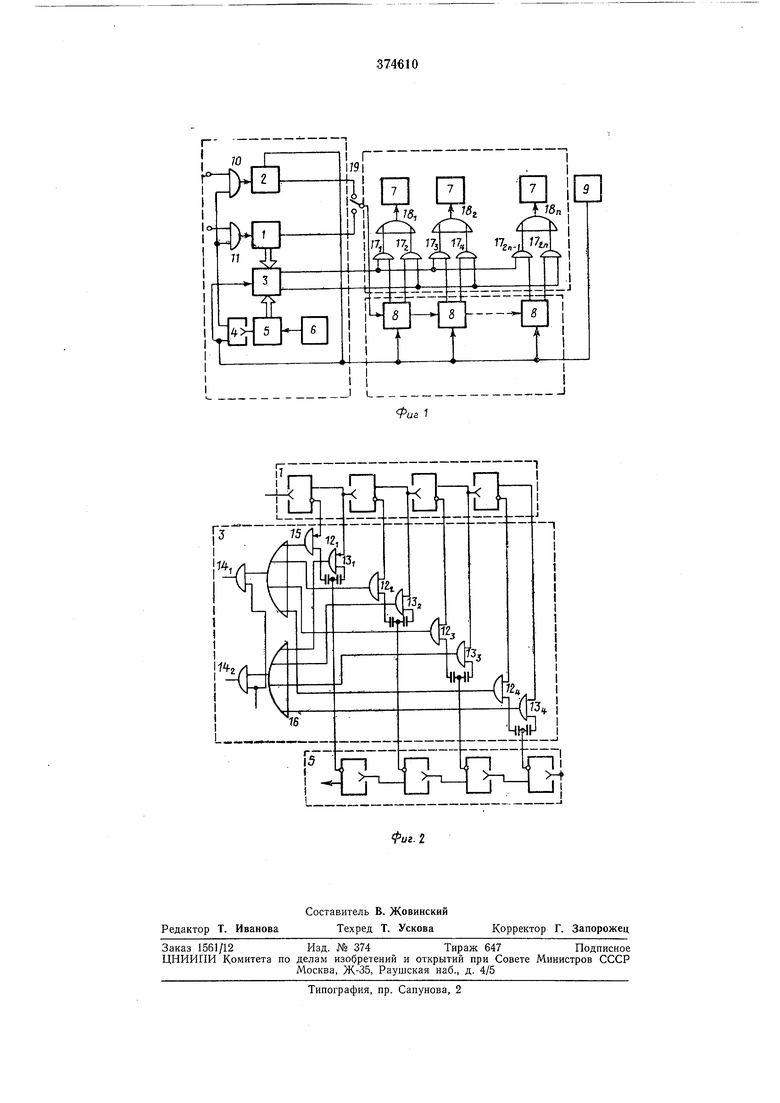

Кроме того, в предлагаемом устройстве логический двоичный умножитель содержит входные логические элементы «И по два на каждые одноименные входы групп, выходы нечетных логических элементов подключены через первый логический элемент «ИЛИ к первому выходному элементу «И, выходы четных логических элементов «И подключены к входам второго элемента «ИЛИ, соединенного со вторым выходным элементом «И, первые входы входных логических элементов «И подключены к первой группе входов; входы второй группы соединены со вторыми входами входных логических элементов «И через дифференцирующие цепочки.

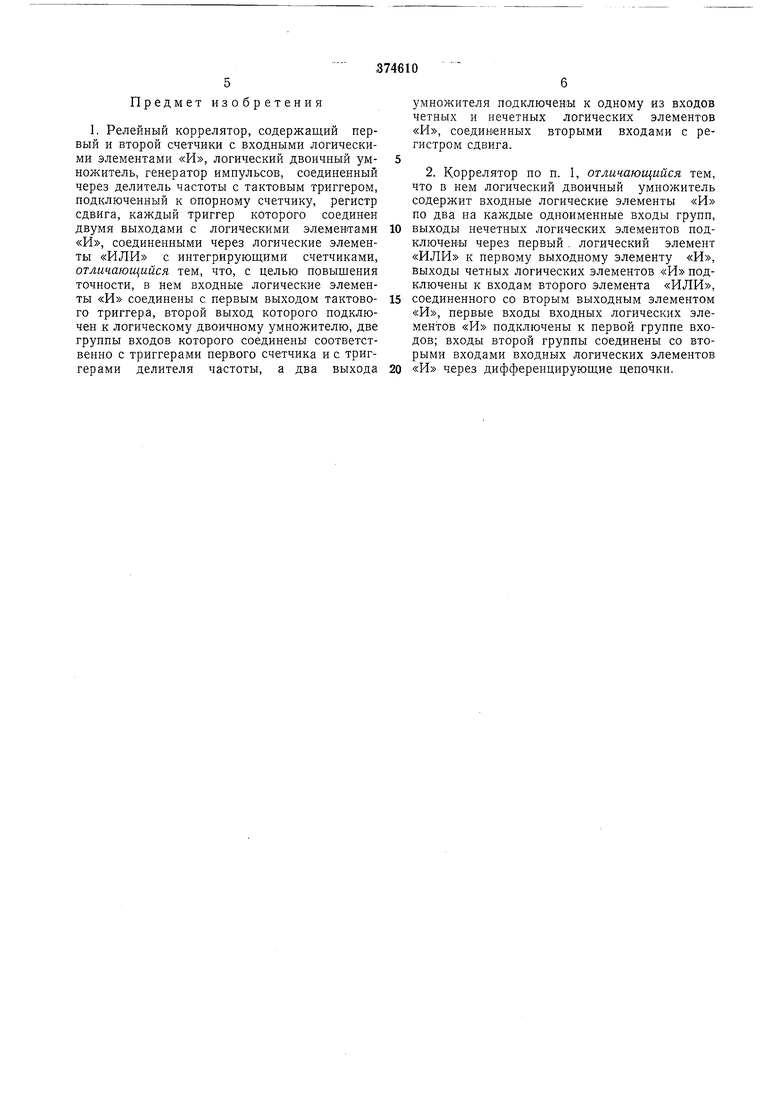

На фиг. 1 приведена блок-схема предлагаемого коррелятора; на фиг. 2 - функциональная схема логического двоичного умножителя для двойного преобразования частота-код-частота на примере четырехразрядных двоичных счетчиков.

Коррелятор содержит счетчики 1 и 2 малой емкости, двоичный логический умножитель 3, тактовый триггер 4, делитель 5 частоты считывания, генератор 6 частоты считывания, интегрируюш,ие счетчики 7, ячейки сдвигового

регистра 8, опорный счетчик 9, логические элементы «И 10, 11 входного устройства; элементы «И 12i-12, и элементы «ИЛИ 15 и 16 прямого и дополнительного кодов логического двоичного умножителя 3, элементы «И 17i-IJzn элементы «ИЛИ 18i-18п интегрирующего устройства; переключатель 19 (конденсаторы на фиг. 2 обозначают дифференцирующие цепочки).

Коррелятор работает в два такта (записи и считывания), которые многократно повторяются в течение времени интегрирования. Длительность тактов определяется периодом следования импульсов, которые подаются на триггер 4 от делителя 5 частоты считывания, поступающей от генератора 6.

В течение такта записи на вход счетчика 1 через элемент «И 11 поступают импульсы частотно-модулированнюго сигнала, частота которого содержит некоторую постоянную составляющую, соответствующую нулевому значению сигнала, и девиацию частоты, пропорциональную сигналу. Емкость счетчика / выбрана равной удвоенному отнощению постоянной составляющей (несущей или начальной частоты) частотно-модулированного сигнала к частоте тактовых импульсов. Поэтому при отрицательных входных сигналах счетчик заполняется до значений, меньших его половинной емкости. При этом старший триггер счетчика / не опрокидывается, и в момент окончания такта записи на первую ячейку сдвигового регистра 8 информация не поступает. Продвигающим импульсом она ставится в положение, соответствующее отрицательному значению входного сигнала. При положительных сигналах счетчик / заполняется до емкости, большей половины, но меньшей его полной емкости. Старший триггер счетчика / опрокидывается. В момент окончания такта записи на первую ячейку 8 сдвигового регистра поступает сигнал, который ставит ее в положение, соответствующее положительному значению входного сигнала. В качестве продвигающих импульсов в сдвиговом регистре используются тактовые импульсы.

При вычислении автокорреляционной функции переключатель 19 устанавливается в нижнее положение, и на сдвиговый регистр поступает информация о знаке входного процесса. При вычислении взаимной корреляционной функции переключатель 19 устанавливается в верхнее положение, и на сдвиговый регистр со счетчика поступает информация о знаке второго процесса.

В течение такта считывания элементы 10 и 11 закрыты, а сигналы с частотой считывания постоянно поступают с генератора 6 на делитель 5 частоты. Последний связан со счетчиком 1 схемой двоичного логического умножителя 3. Цифровой код числа, записанный в счетчике / через элементы , 15, преобразуется в число импульсов, соответствующее прямому коду записанного числа, а через ячейки 13i-ISt, 16 - в число импульсов, соответствующее дополнительному коду этого числа.

Импульсы, соответствующие прямому и дополнительному кодам, поступают на интегрирующие счетчики 7, причем прямой или дополнительный код выбирается через элементы 17i-//271, а также через элементы в зависимости от знака, записанного в соответствующей ячейке 8 сдвигового регистра.

Операция интегрирования в счетчиках производится по алгоритму

f(N, + N,slgnl N l-l,l)) 1 1

(nN, +i АЛ/ sign A/V(, +1)),

где я - количество выборок за время измерения;

/ - номер ячейки сдвигового регистра; NO - половина емкости счетчика 1 или 2; ЛЛ - число, пропорциональное сигналу. A/V - число, пропорциональное сигналу.

Первый член правой части равенства представляет собой квадрат математического ожидания частотного сигнала и является величиной, одинаковой для всех интегрирующих счетчиков 7. Второй член представляет собой

значения корреляционной функции.

Применение прямого и дополнительного кодов позволяет использовать в качестве интегрирующих элементов нереверсивные счетчики 7, так как запись в них прямого кода соответствует умножению числа на положительный знак, а запись дополнительного кода - умножению на отрицательный знак. Разравнивание импульсов во времени лосгическим умножителем 3 позволяет использовать в качестве интегрирующих счетчиков более экономичные накопительные ячейки.

Продвижение знака по регистру сдвига, тактование работы коррелятора, сброс счетчиков / или 2 по окончании такта считывания,

а также запрещение прохождения импульсов через элементы 12 и 13 логического умножителя 3 в режиме записи осуществляется тактовыми импульсами от триггера 4. Для вывода результатов интегрирования

со счетчиков 7 на индикацию или на печать необходимо сравнение результатов интегрирования с числом импульсов, равным первому слагаемому правой части приведенного выше равенства. Для этой операции служит опорный

счетчик 9, емкость которого выбрана пропорционально этому слагаемому таким образом, что переполнение счетчика свидетельствует об окончании времени измерения ГизмДля непрерывного преобразования частотного сигнала в цифровой код, входное устройство может быть выполнено двухканальным с тем, чтобы в один из каналов в течение такта записывались числа, а с другого одновременно считывались записанные в предыдущем

такте числа.

Предмет изобретения

1. Релейный коррелятор, содержащий первый и второй счетчики с входными логическими элементами «И, логический двоичный умножитель, генератор имиульсов, соединенный через делитель частоты с тактовым триггером, подключенный к опорному счетчику, регистр сдвига, каждый триггер которого соединен двумя выходами с логическими элементами «И, соединенными через логические элементы «ИЛИ с интегрирующими счетчиками, отличающийся тем, что, с целью повышения точности, в нем входные логические элементы «И соединены с первым выходом тактового триггера, второй выход которого подключен к логическому двоичному умножителю, две группы входов которого соединены соответственно с триггерами первого счетчика и с триггерами делителя частоты, а два выхода

умножителя подключены к одному из входов четных и нечетных логических элементов «И, соединенных вторыми входами с регистром сдвига.

2. Коррелятор по п. 1, отличающийся тем, что в нем логический двоичный умножитель содержит входные логические элементы «И по два на каждые одноименные входы групп,

выходы нечетных логических элементов подключены через первый . логический элемент «ИЛИ к первому выходному элементу «И, выходы четных логических элементов «И подключены к входам второго элемента «ИЛИ,

соединенного со вторым выходным элементом «И, первые входы входных логических элементов «И подключены к первой группе входов; входы второй группы соединены со вторыми входами входных логических элементов

«И через дифференцирующие цепочки.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯТОРВ ПТ БФшд mm? | 1972 |

|

SU424155A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОМПЛЕКСНЫХВЕЛИЧИН | 1972 |

|

SU354355A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Частотно-цифровое устройство для определения дисперсии и математического ожидания | 1974 |

|

SU468252A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство автоматической подстройки частоты | 1985 |

|

SU1298915A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| Устройство для селекции изображений объектов | 1989 |

|

SU1777651A3 |

r-tM3

r

Авторы

Даты

1973-01-01—Публикация