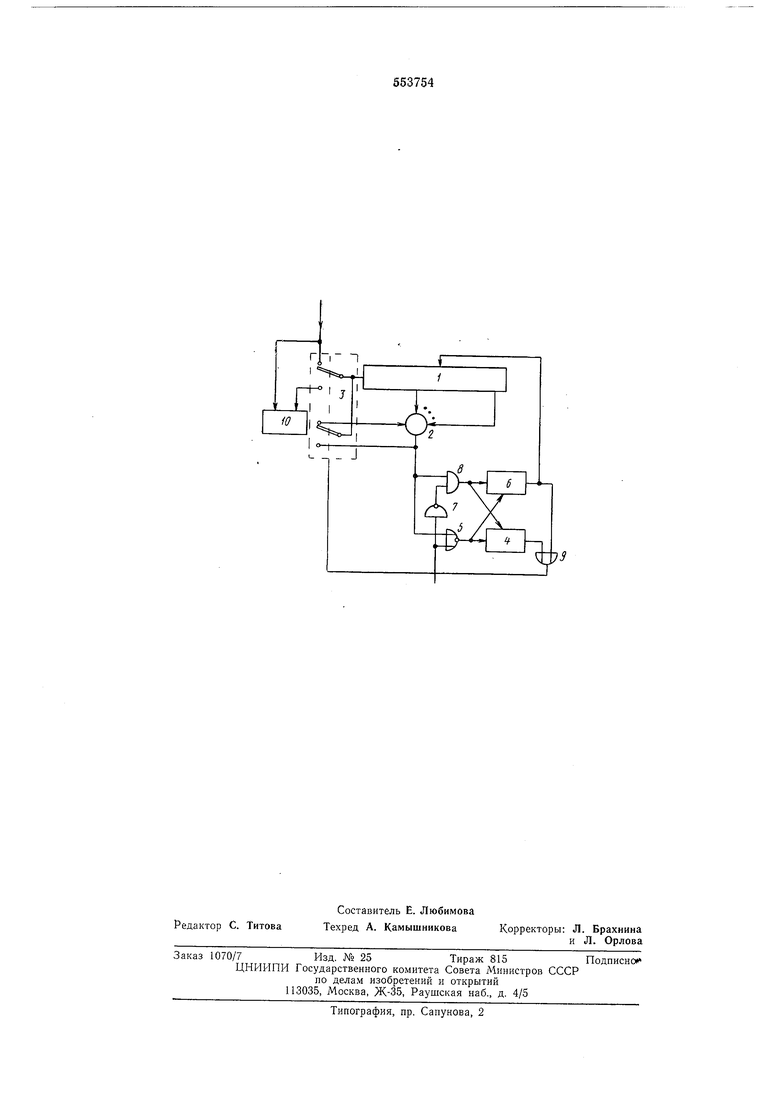

через сумматор 2 подключены к входному коммутатору 3, включенному между входами регистра 1 сдвига и сумматора 2, и к входу основного счетчика 4 через элемент ИЛИ- НЕ 5, на управляющий вход которого подан соответствующий сигнал, дополнительный счетчик 6, инвертор 7, и элементы И и ИЛИ 8 н 9, при этом выход сумматора 2 через последовательно соединенные элемент И 8, управляющий вход которого соединен с управляющим входом элемента ИЛИ-НЕ 5 через инвертор 7, дополнительный счетчик 6 подключен к инвертирующему входу регистра 1 сдвига и к одному из входов элемента ИЛИ 9, к другому входу которого подключен выход основного счетчика 4, а выход элемента ИЛИ 9 подключен к управляющему входу входного коммутатора 3, кроме того, выход элемента ИЛИ-НЕ 5 подключен к установочному входу дополнительного счетчика 6, а выход элемента И 8 - к установочному входу основного счетчика 4, и один из контактов входного коммутатора 3 - к коррелятору 10. Устройство работает следующим образом. В исходном состоянии элементы И и ИЛИ -НЕ заперты управляющим сигналом, переключатели входного коммутатора 3 находятся в верхнем положении и регистр 1 заполняется символами последовательности, поступающей на вход. Через п тактов, когда все ячейки регистра заполняются, управляющий сигнал снимается. Иоступающая из канала и записываемая в регистр 1 информация контролируется сумматором 2. Нри отсутствии ощибок во входной последовательности на выходе сумматора 2 появляются нулевые сигналы, поскольку его подключение к регистру 1 выполняется на основе проверочного полинома. Нусть т - максимальное расстояние между отводами регистра 1. Тогда, через т тактов после снятия управляющего сигнала все содержимое регистра 1 будет проконтролировано сумматором 2. Ири приеме без ошибок это соответствует появлению на выходе сумматора 2 подряд т нулей (при приеме прямой последовательности) или т единиц (при приеме инвертированной последовательности) . Единичные сигналы подсчитываются дополнительным счетчиком б, а нулевые основным счетчиком 4. Появление сигнала переполнения любого из этих счетчиков 4 и 6 свидетельствует о том, что в регистре 1 находится неискаженный отрезок входной последовательности. Сигнал переполнения через элемент ИЛИ 9 переводит переключатели входного коммутатора 3 в нижнее положение. При этом регистр 1 и сумматор 2 образуют опорный генератор и начинается проверка правильности синхронизации с помощью коррелятора 10.

Если входная последовательность принимается с ощибками, то счетчики 4 и б устанавливаются в нулевое положение сигналами с выходов элементов И и ИЛИ-НЕ 8 и 5 и ввод

символов продолжается до тех пор, пока не будет получено подряд т или т единиц. Норог счетчиков 4 и 6 может быть сделан больше, чем т, при этом некоторые или все символы будут проконтролированы сумматором 2 более одного раза.

Если принимается инвертированная последовательность, то содержимое регистра I при переводе его в режим опорного генератора необходимо инвертировать. Это делается путем подачи на его инвертирующий вход сигнала переполнения дополнительного счетчика 6.

Предлагаемое устройство позволяет обеспечить синхронизацию при приеме инверсномодулированных последовательностей простыми техническими средствами.

Формула изобретения

Устройство для синхронизации псеадослучайных сигналов, содержащее регистр сдвага, выходы соответствующих разрядов которого через сумматор подключены к входному коммутатору, включенному между входами регистра сдвига и сумматора, и к ьход основного счетчика через элемент ИЛИ-НЕ, на управляющий вход которого подан соответствующий сигнал, отличающееся тем,

что, с целью обеспечения синхронизации при приеме инверсно-модулированных последовательностей, введены дополнительный счетчик, инвертор и элемент И и ИЛИ, при этом выход сумматора через последовательно соединенные эле.мент И, управляющий вход которого соединен с управляющим входом элемепта ИЛИ-НЕ через инвертор, и дополнительный счетчик подключен к инвертирующему входу регистра сдвига и к одному из входов элемента ИЛИ, к другому входу которого подключен выход основного счетчика, а выход элемента ИЛИ подключен к управляющему входу входного коммутатора, кроме того, выход элемента ИЛИ-НЕ подключен к установочному входу дополнительного счетчика, а выход элемента И - к установочному входу основного счетчика.

Источники информации, принятые во внимание при экспертизе изобретения:

1.Авторское свидетельство СССР Я 486481, кл. Н 04L 7/08, 1974.

2.Авторское свидетельство СССР №488353, кл. Н 04L 7/08, G 06F 15/36, 1973.

Г--I

ТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство поиска широкополосного сигнала | 1986 |

|

SU1453601A2 |

| Устройство синхронизации сложного сигнала | 1987 |

|

SU1518901A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| МОДУЛЯТОР ДИСКРЕТНОГО СИГНАЛА ПО ВРЕМЕННОМУ ПОЛОЖЕНИЮ | 2018 |

|

RU2677358C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2011 |

|

RU2470459C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство для синхронизации м-последовательности | 1975 |

|

SU544156A1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

Авторы

Даты

1977-04-05—Публикация

1975-03-04—Подача