жемня, а выход - к одному из входов компаратора, другим входом соединенного с выходом генератора пилообразноного напрж ния, входом подключенного к прямому выходу генератора тактовых импульсов, инверсный выход которого подкгаочев к счетному входу т-триггера, к выходам которого и к прямому выходу генератора тактовых импульсов попарно подключены входы генератора тактовых импульсов, попарно подключены входы логического блока И-ИЛИ-НЕ, выходами соедасненного со входами триггера, приче;ч к выводам Т-триггера и RS - триггера подключены входы усилителей мощности с трансформаторными) 1вых6дами,Ьгикдый из которых подключен к базовым цепям транзисторов двухтактного силового преобразователя, и узел пуска-останова 4Л.

Недостатком этого устройства является то, что на обмотках трансформаторов усилителей мощности при их запирании возникает противо-ЭДС, в результате чего к базам транзисторов преобразователя, котос ые к данному моменту находились в запертом состоянии, прикладывается отпирающий импульс. В то же время транзисторы, находившиеся к этому моменту в насыщенном состояний из-за конечного времени запирания некоторое время продолжают пропускать коллекторный ток. Таким образом, может возникнуть сквозной ток значительной величины, который существенно снижает надежность работы транзисторов силового преобразователя вплдть до выхода их из строя. Особенно опасен режим сквозного тока в силовых преобразователях, собранных по мостовой схеме,

Целью изобретения является исключение сквозных токов и тем самым повышение надежности работы стабилизатора.

Для достижения этой цели в импульсном стабилизаторе постоянного напряжения , содержащем двухтактный силовой преобразователь напряжения на транзисторах, выполненный по мостовой схеме и подсоединенный через фильтр низких частот и резисторный датчик тока, соединенный со входом блока для защиты oi аварийных режимов, к выходу для подключения нагрузки, соединенному с одним их входов усилителя рассогласования, другой вход которого подключен к источнику опорного напряжения, а вь1ход - к одному из входов компаратора, другим входим соединенного с выходом генератора пилообразного напряжения , входом подключенного к прямому выходу генератора тактовых импульсов, инверсный выход которого подключен к счетному входу Т-триггера, к выходам которого и к прямому выходу генератора тактовых импульсов попарно подключены входы логического блока

И-ИЛИ-НЕ, выходами соединенного со входами RS -триггера, -причем к выходам Т -триггера и ЯЗ - триггера подключены входы двух усилителей g мощности с Трансформаторными выходами, каждый из которых подключен к базовым цепям транзисторов двухтактного силового преобразователя, и узел пуска-останова, новым является то, что, стабилизатор снабжен логическим блоком

10 совпадения, входы которого подключены к выходам компаратора, блока для защиты от аварийных режимов и блока пуска-останова, а выходы - к двум входам логического блока И-ИЛИ-НЕ.

5 На фиг.1 представлена принципиальная схема импульсного стабилизатора постоянного напряжения; на фиг.2 временные диаграммы импульсов на выходе блоков стабилизатора.

Силовая часть схемы импульсного стабилизатора содержит двухтактный силовой преобразователь напряжения на транзисторах 1-4, трансформаторе Ь и демодуляторе 6, в состав которого

S входит фильтр низких частот на дросселе . 7 и конденсаторе 8. выходное напряжение подается на нагрузку 9.

Управлякнцая часть состоит из усилителей мощности 10 и 11 с трансформаторами 12, 13 на выходе, обмотки 12i 13 и 12, 13 которых включены в базовые цепи транзисторов 1-4, генератора 14 тактовых импульсов, инверсный выI m I I

ход которого подключен ко входу

триггера 15, управляющая

часть также

ewnmtiaOT T)€t -friMTT- n

включает RS-триггер. 16, входы которого соединены с выходами логического блока И-ИЛИ-НЕ 17, источника 18 опорного напряжения, подключенного к одному из входов усилителя рассогласования 19, выход которого наряду с выходом генератора 20 пилообразного напряжения подключен ко входу компаратора 21. Выход компаратора 21 и выход блока 22 для защиты от аварийных режимов подключены к логическому блоку совпадения 23, ко входу которого подключен также исполнительный элемент 24 блока пуска-останова (который на схеме не показан).Блок дня защиты от аварийных режимов под ключен к резисторному датчику тока 25.

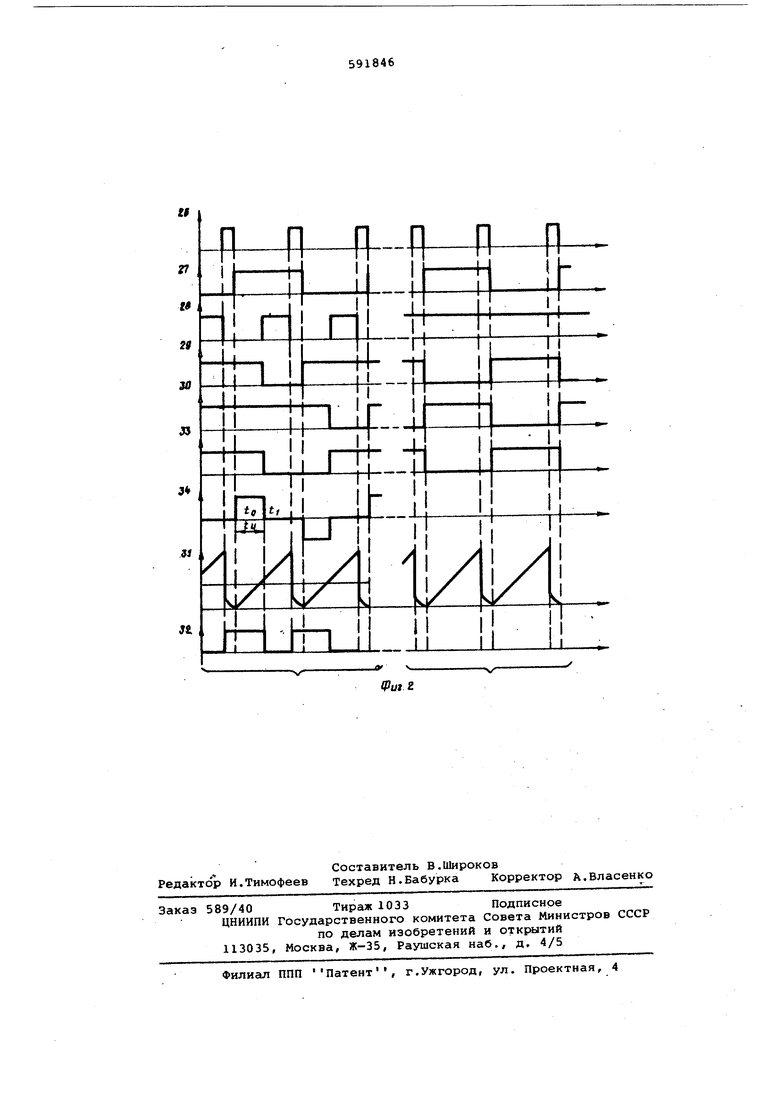

На фиг.2 представлены временные диаграммы импульсов на выходе блоков

стабилизатора: 26 - генератора 14 (прямой выход), 27 - Т триггера 15 (прямой выход), 28 - логического блока совпадения 23, 29 - логического .блока И-ИЛИ-НЕ 17 (первый выход),30 логического блока И-ИЛИ-НЕ 17 (второй выход), 31 - генератора 20, 32 -компаратора 21, 33 - R3-триггера 16 (инверсный выход), 34 - на базе одного из транзисторов силового преобразования, например 3. Стабилизатор работает следующим образом. В нормальн6ми( при .отсутствии ава рий) режиме с выхода (22) и (24) на выходы (23) подаются сигналы а виде логической :1.I При равенстве напряжения пильз и усилителя рассогласования в момент tj на выходе компаратора 21 появляteTCH логический О , а на выходе блока совпадения 23 - логическая i В этот момент происходит переключение триггера 16 и, как видно из временных диаграмм, длительность импульса управ ления на базах транзисторов преобра;3ователя (3 или 4).-tg равно длительности хода пилообразного напря жения до момента сравнения . , При аварийном режиме на выходе (2 ПОСТОЯННО имеется логический О , а на выходе 23.Ll. В результате этого переключение RS- триггера 16 будет происходить практически одновременно с т - триггером 15. Физйровка усилителей 10 и 11 и трансформаторов 12 и 13 выбирается так, чтобы напряжения на базовых обмотках (12 и 13) имели фазовый сдвиг аналогичный сигналам на диаграммах 27 и 33. Таким Образом, в аварийном режиме происходит сдвиг по фазе напряжения на выходах (16 и 11) так, Что напряжения на обмотках (12 и 13) находятся в противофазе, в то же вре мя режим работы усилителей 10 и 11 и трансформаторов 13, 12 не меняется. Аналогичным образом работает схеМа управления при размыкании контак га (24) (режим - останов), когда на этот вход (23) подается логический О. Реализация предлагаемой схемы и испытания .макета показали, что надеж ность работы преобразователя существенно повысилась в то время, как без введения блока совпадения, имели мес то выходы из строя транзисторов сило вого преобразователя по причине возникновения сквозныхтоков при вклю чении усилителей мощности по известным схемам. Формула изобретения Импульсный стабилизатор постоянно го напряжения, содержащий двухтактный с иловой преобразователь напряжения на транзисторах, выполненный по мосто вой схеме и подсоединенный через фильтр низких частот и резисторный датчик тока, соединенный- со входом блока для зсициты от аварийных режимов к выходу для подключения нагрузки,соединенному с одним из входов усилителя рассогласования, другой вход которого подключен к источнику опорного напряжения, а выход - к одному из входов компаратора, другим входом соединенного с выходом генератора пилообразного напряжения, входом подключенного к прямому выходу генератора тактовых импульсов, инверсный выход которого подключен к счётному входу Т - триггера, к выходам которого и к прямому выходу генератора тактовых импульсов попарно подключены входы логического блока И-ИЛИ-НЕ, выходами соединенного со входами RSтриггера, причем к выходам Т-триггера и RS - триггера подключены входы двух усилителей мощности с трансформаторными выходами, каждый из которых подключен к базовым цепям транзисторов двухтактного i силового преобразователя и узел пуска-юстанова о т л и ч ю |д и и с я тем, что, с Ьёлью повышення надёжности работы стабилизатора путем исключения сквозных ,токов транзисторов, стабилизатор снабжен логическим блоком совпадения, входы которого подключены к выходам компаратора, блока для защиты от аварийных режимов и блока пуска-останова, а выходы - к двум входам логического блока И-ИЛИ-НЕ. Источники информации, принятые во внимание при экспертизе: 1.Схема стабилизации выходного напряжения статического преобразователя частоты постоянного напряжения или инвертора. Патент ФРГ 1961705, кл. 21 е 7/10, 1967. 2.Схема защиты, обеспечивающая плавное включение импульсного регулятора. Патент США № 3733540,кл.321-47, 1968. . 5. Стабилизированный преобразователь напряжения. Авторское свидетель ство СССР №419873,кл. G 05 F 1/56, 1970. 4. Стабилизатор с широтноимпульсной модуляцией. Патент США 367Q234, кл. 321-18, 1970.

FJVA../ т- ,л...-jw/v I

L.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный стабилизатор постоянного напряжения | 1980 |

|

SU978130A1 |

| Преобразователь постоянного напряжения в постоянное | 1985 |

|

SU1418869A1 |

| Релейно-импульсный стабилизатор постоянного напряжения | 1990 |

|

SU1758640A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Стабилизированный источник постоянного напряжения | 1978 |

|

SU771641A1 |

| Стабилизированный преобразователь постоянного напряжения | 1981 |

|

SU982164A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| МНОГОКАНАЛЬНЫЙ ШИРОТНО-ИМПУЛЬСНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2733782C1 |

| МНОГОКАНАЛЬНЫЙ ИМПУЛЬСНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ | 2024 |

|

RU2838912C1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

Авторы

Даты

1978-02-05—Публикация

1975-10-08—Подача