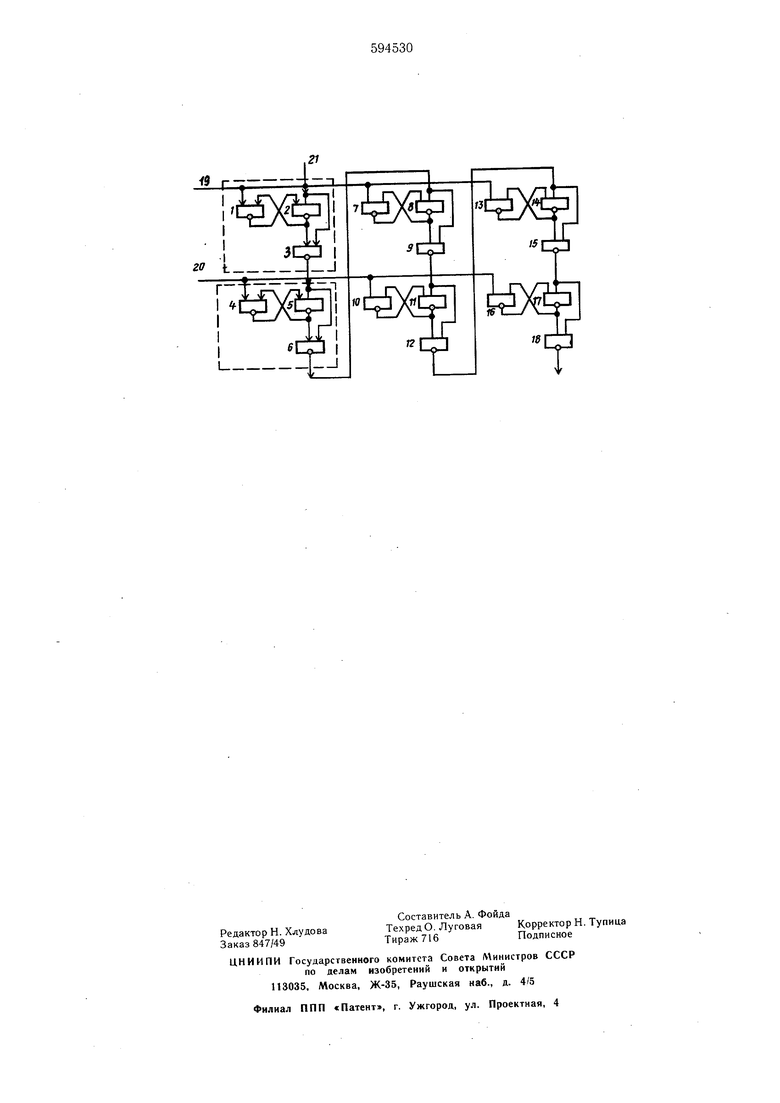

Изобретение относится к вычислительной технике и может быть использовано для построения регистров сдвига. Известен регистр сдвига, построенный по системе М-S и содержащий два RS-триггера, один из которых является основным, а второй дополнительным, каждый из этих триггеров имеет два элемента управления, вместе с которыми образует ячейку памяти 1. Каждая ячейка состоит из четырех элементов И-НЕ (ИЛИ-НЕ). Недостаток этого регистра - большое число элементов и большое число входов в элементах, что усложняет схему сдвигового регист ра. Наиболее близкой к предлагаемой по технической сущности является ячейка памяти, содержащая элементы И-НЕ, выход первого элемента И-НЕ соединен с одним из входов второго элемента И-НЕ, выход которого соединен с одним из входов первого элемента И-НЕ, и шину синхроимпульсов 2. Недостатком данной ячейки памяти является большое число элементов на разряд. На каждый разряд используется восемь двухвходовых элементов И-НЕ. упрощение ячейки паЦель изобретения мяти. Это достигается тем, что в ячейке памяти другой вход первого эле.мента И-НЕ подключен к щине синхроимпульсов, другой вход второго элемента И-НЕ подключен к входу ячейки и к одному из входов третьего элемента И-НЕ, другой вход которого подсоединен к выходу второго элемента И-НЕ, а выход третьего элемента И-НЕ соединен с выходом ячейки. На чертеже представлена принципиальная схема предлагаемого устройства. Ячейка памяти содержит три элемента И-НЕ. Возможно применение равноценных им элементов ИЛИ-НЕ. Каждый разряд регистра выполнен на двух ячейках памяти. Первый разряд выполнен на ячейке, содержащей элементы И-НЕ 1, 2 и 3, и на ячейке, содержащей элементы И-НЕ 4, 5 и 6. Второй выполнен на ячейке на элементах И-НЕ 7, 8 и 9 и на ячейке на элементах И-НЕ 10, 11 и 12, третий разряд - на элементах И--Н1;-: 13, И, 15, 16. 17 и 18. Устройство содержит IIHIHI I синхроимпульсов 19, 20 и в.ход peiHCTpa 21.

В каждой ячейке выход первого элемента соединен с входом второго элемента, выход которого .соединен с одним из входов первого элемента. Каждая ячейка содержит шину синхроимпульсов 19, 20, причем входы первых элементов 1, 7 и 13 нечетных ячеек подсоединены к шине 19 синхроимпульсов, а входы первых элементов 4, 10 и 16 четных ячеек подсоединены к шине 20 синхроимпульсов. В ячейке вход второго элемента 2 подсоединен к входу ячейки и входу третьего элемента 3, так вход элемента 2 подсоединен к входу регистра 21 и к входу элемента 3, вход элемента 5 подсоединен к входу второй ячейки, который подсоединен к выходу первой ячейки, т. е. к выходу элемента 3 и входу третьего

элемента 6 ячейки. Второй вход третьего элемента 3 ячейки подсоединен к выходу второго элемента 2 ячейки. Выходом ячейки является выход третьего элемента 3.

Параллельный код с регистра может сниматься с выходов элементов 1, 7, 13, 2, 8, 14 и с элементов 4, 10 и 16, 5, 11 и 17.

Рассмотрим работу устройства при условии, что в схеме применены элементы И-НЕ для положительных импульсов на входе.

Особенностью регистра на предлагаемых ячейках памяти является то, что в каждой его ячейке памяти на выходе третьего элемента с момента прихода отрицательного синхроимпульса на тактовую шину (синхроимпульсов) данной ячейки и до момента прихода отрицательного импульса на тактовую шину предыдуш,ей ячейки памяти действует высокий потенциал.

Действительно, если ячейка памяти, предположим 7, 8, 9, находилась в состоянии с высоким потенциалом на выходе элемента 7 и низким на выходе элемента 8, то на выходе элемента 6 должен был действовать высокий потенциал и после прихода отрицательного импульса на шину 19 состояние триггера (на чертеже не выделен) на элементах 7 и 8 не изменится и на выходе элемента 9 за счет действия низкого потенциала на выходе элемента 8 будет высокий потенциал.

Если же триггер на элементах 7 и 8 находился с низким потенциалом на выходе элемента 7, то возможны два варианта потенциала на выходе элемента 6. При высоком потенциале на выходе элемента 6 с приходом отрицательного импульса на шину 19 на выходе элемента 7 появится высокий потенциал, на выходе элемента 8 - низкий, который вызовет на выходе элемента 9 высокий потенциал.

При низком потенциале па выходе элемен.та; 6 на выходе элемента 9 за счет действия данного Ьотенциала на его вход будет поддерживаться высокий потенциал независимо от потенциала на выходе элемента 8.

Теперь предположим, что предыдушая ячейка памяти находилась в состоянии с низким потенциалом на выходе элемента 5 и высоким на выходе элементов 4 и 6, то тогда с приходом отрицательного импульса на шину 19 следуюшая за ней ячейка на элементах 7, 8, 9

примет то же состояние, т. е. на выходе элементов 7 и 9 будет высокий потенциал, а на

выходе элемента 8 - низкий. С приходом тактового импульса на шину 20 это же состояние перепишется в следующую ячейку на элементах 10, 11, 12.

Если же предыдущая ячейка памяти на элементах 4, 5, 6 находилась в состоянии с высоким потенциалом на выходе эле.мента 5 и низким на выходе элемента 4, то при приходе импульса на шину 19 на всех входах элемента 6 будут действовать высокие потенциалы и на выходе элемента 6 будет низкий потенциал, который по окончании импульса на шине 19 установит ячейку на эле.ментах 7, 8, 9 в состояние с высокими потенциалами на выходах элементов 7 и 9 и низким на выходе элемента 8.

Следующий импульс, приходяший на шину 20, перепишет информацию с ячейки 7, 8, 9 в ячейку 10, И, 12.

Таким образом, после каждого прихода тактовых импульсов на шину 19 и 20 информация смен ается на две ячейки памяти.

Количество элементов в предлагаемой ячейке памяти по сравнению с количеством элементов в известных ячейках памяти уменьшено на 25%. В предлагаемой ячейке используются три элемента, в то время как в известных используются четыре.

Экономия элементов в ячейках памяти уменьшает объем оборудования, стоимость, пот ребляемую мощность и увеличивает надежность устройства.

Формула изобретения

Ячейка памяти для регистра сдвига, содержащая элементы И-НЕ, выход первого элемента И-НЕ соединен с одним из входов второго элемента И-НЕ, выход которого соединен с одним из входов первого элемента И-НЕ, и шину синхроимпульсов, отличающаяся тем, что, с целью упрощения ячейки, в ней другой вход первого элемента И-НЕ подключен к шине синхроимпульсов, другой вход второго элемента И-НЕ подключен к входу ячейки и к одному из входов третьего элемента И-НЕ, другой вход которого подсоединен к выходу второго элемента И-НЕ, а выход третьего элемента И-НЕ соединен с выходом ячейки.

Источники информации, принятые во внимание при экспертизе:

1. Букреев И. Н., Мансуров Б. М. и Горячев В. И. Микроэлектронные схемы цифровых устройств. М., «Сов. радио, 1975, с. 85, рис. 3.7. и рис. 3.8.

2. Букреев И. Н., Мансуров Б. М. и Горячев В. И. Микроэлектронные схемы цифровых устройств. М., «Сов. радио, 1975. с. 82, рис. 3.3.

19

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1979 |

|

SU851495A1 |

| Счетчик на кольцевом регистре | 1977 |

|

SU738177A1 |

| Регистр сдвига | 1975 |

|

SU631992A1 |

| Счетчик на кольцевом регистре | 1978 |

|

SU733111A1 |

| Ячейка памяти сдвигового регистра | 1976 |

|

SU652618A1 |

| Распределитель импульсов | 1976 |

|

SU610301A1 |

| Регистр сдвига | 1979 |

|

SU855732A1 |

| Сдвиговый регистр | 1973 |

|

SU643974A1 |

| Измеритель линейных перемещений | 1986 |

|

SU1401273A1 |

| Двухтактный регистр сдвига | 1975 |

|

SU744732A1 |

Авторы

Даты

1978-02-25—Публикация

1975-11-17—Подача