(54) РЕГИСТР СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1988 |

|

SU1539841A1 |

| Распределительное устройство | 1982 |

|

SU1088074A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| Устройство для считывания изображений | 1986 |

|

SU1429142A1 |

| Устройство для считывания и обработки изображений | 1988 |

|

SU1513486A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР С ЗАПОМИНАЮЩИМ УСТРОЙСТВОМ НА МАГНИТНОМ БАРАБАНЕ | 1966 |

|

SU182414A1 |

| Устройство для цифровой магнитной записи | 1988 |

|

SU1589318A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении регистров сдвига.

Известен сдвигающий регистр, каж- . дый разряд ячейки которого состоит нз двух синхронных элементов, а к первому элементу каждого разряда присоединяется дополнительный расширитель из элементо1 И-ИЛИ. Регистр имеет общую шину установки нуля и две шинУ сдвигающих импульсов, по одной из которых поступает прямой сигнал, а по другой - инвертирс5ванный 11 .

Наиболее близким по технической сущности к изобретению является однофазный двухтактный регистр с параллельно-последовательным сдвигом, содержащий разрядные шины и подключенные к ним разрядные ячейки, каждая из которых выполнена из двух вхо.довых элементов И с инвертором на первом входе и соединены последовательно с элементом ИЛИ С2.

Недостатком таких сдвигающих регистров является сложность схемного выполнения.

Цель изобретения - упрощение регистра сдвига.

Поставленная цель достигается тем,; что в регистре сдвига, содержащем ячейки памяти, каждая из KOTOJ JX выполнена на последовательно соединенных элементах ИЛИ и И, формирователь тактовых импульсов, первый и второй входы которого соединены соответственно с тактовой шиной и шиной сброса, вторые входы элементов И

10 четных ячеек памяти подключены к первому выходу формирователя тактовых импульсов, ко второму выходу которого подсоединены вторые входы элементов И нечетных ячеек памяти, выход

15 элемента И каждой ячейки памяти :соединен с первым входом элемента ИЛИ 1данной ячейки памяти н с первым входом элемента ИЛИ последующей ячейки памяти.

20

Кроме того, формирователь тактовых импульсов содержит последовательно включенные первый элемент И, первый элемент ИЛИ и Т-тригг«р, элементы задержки, второй и третий элементы ИЛИ,

25 инвертор, второй и третий элементы И, выходы которых соединены с выходами формирователя тактошлс импульсов, одни из входов второго и третьего элементов И подключены, соответст30венно к выходам второго и третьего

элементов ИЛИ, первые входы которых соединены с выходами элементов задержки, а вторые входы - с выходами Т-триггера, другие входы второго и третьего элементов И подсоединены к выходу инвертора, вход которого подключен ко второму входу формирователя тактовых импульсов и к одному из входов первого элемента И другой вход которого соединен с одним из выходов Т-триггера, второй вход первого элемента ИЛИ соединен с первым входом формирователя тактовых импульсов.

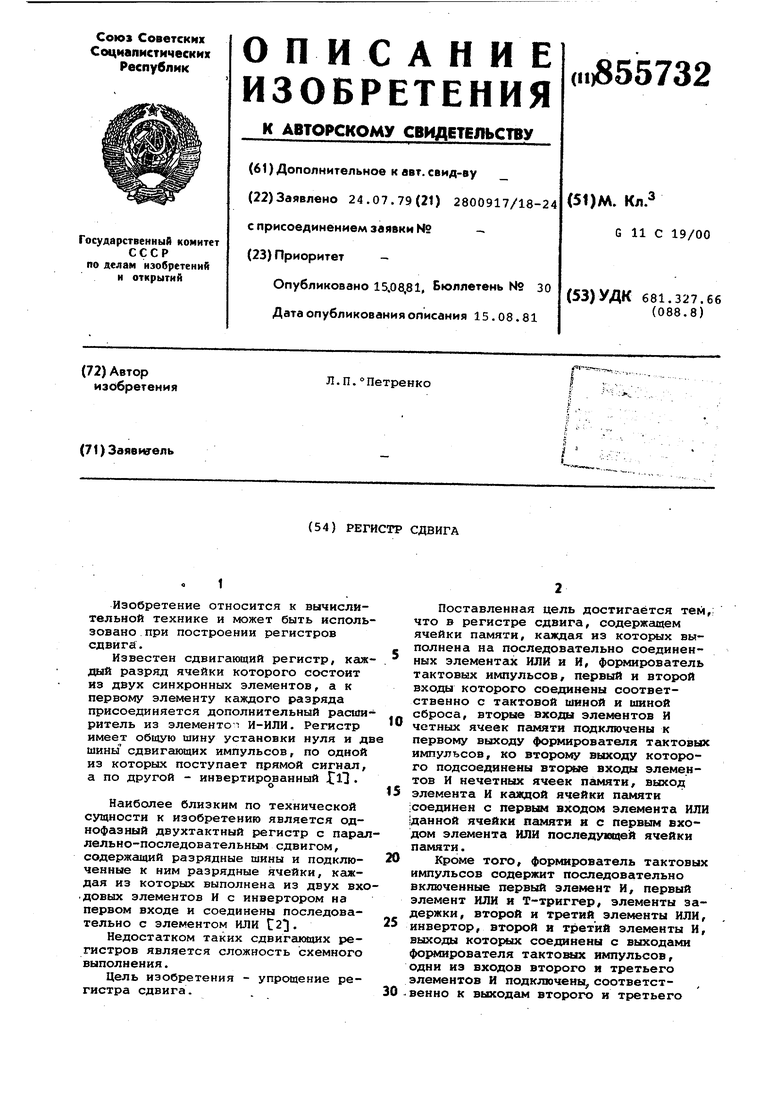

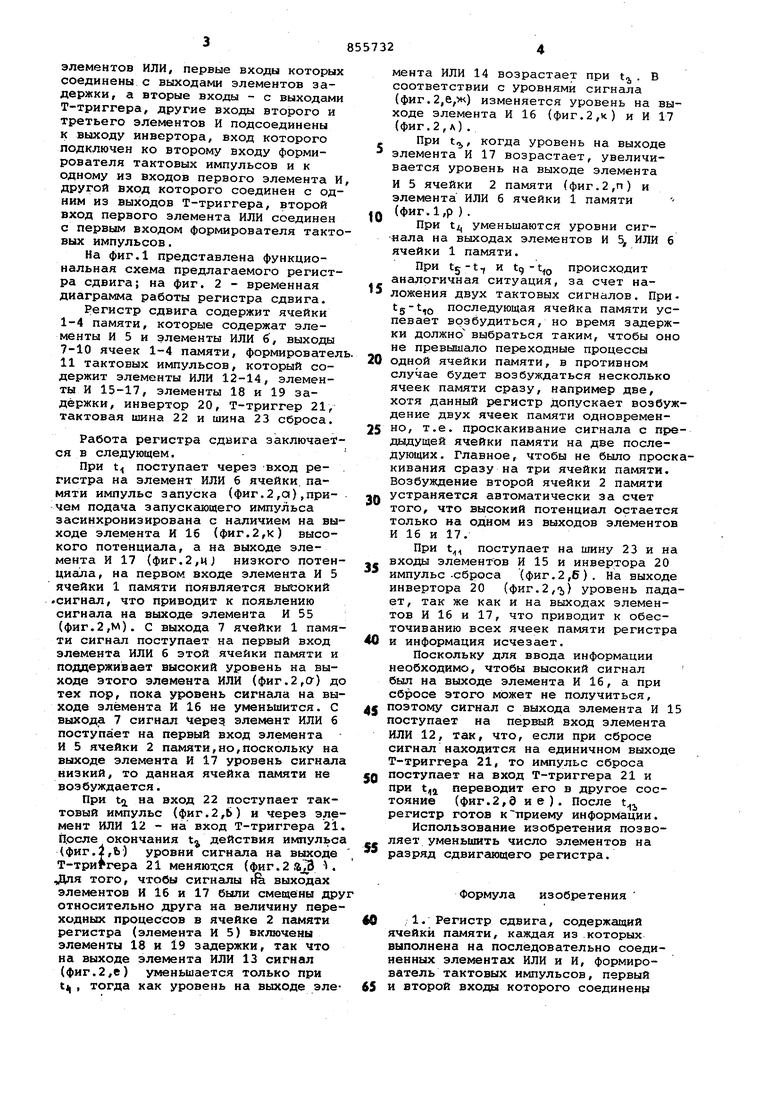

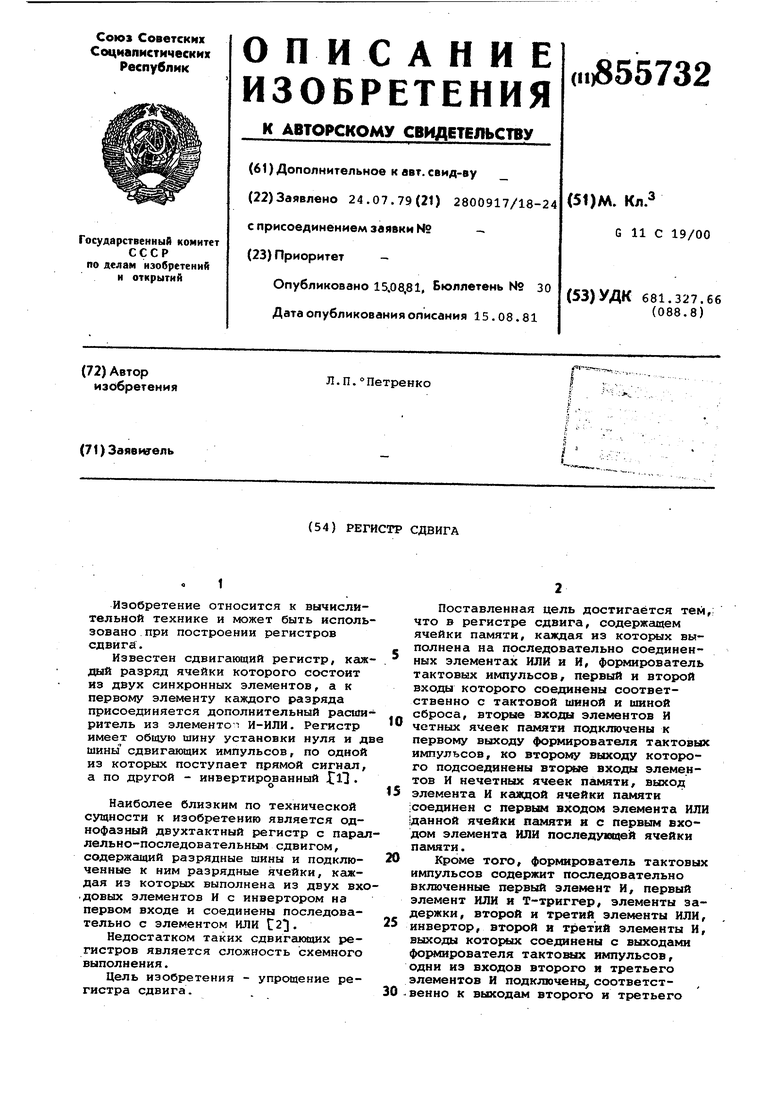

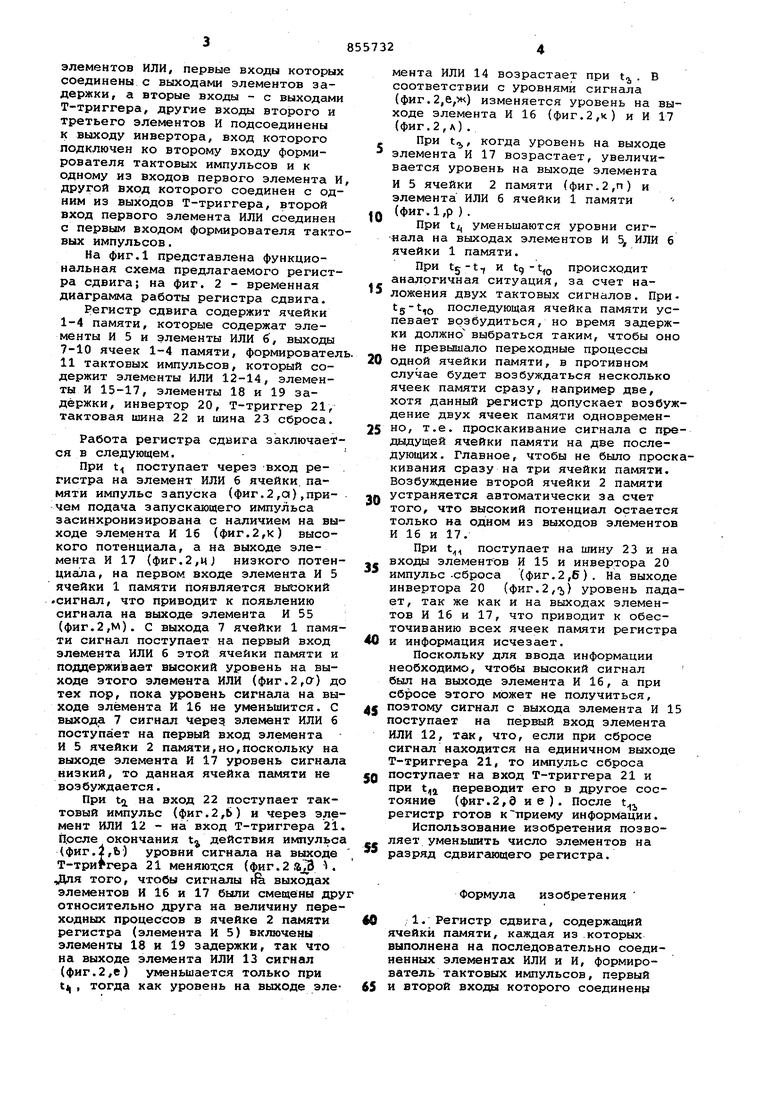

На фиг.1 представлена функциональная схема предлагаемого регистра сдвига; на фиг. 2 - временная диаграмма работы регистра сдвига.

Регистр сдвига содержит ячейки 1-4 памяти, которые содержат элементы И 5 и элементы ИЛИ б , выходы 7-10 ячеек 1-4 памяти, формировател 11 тактовых импульсов, который содержит элементы ИЛИ 12-14, элементы И 15-17, элементы 18 и 19 задержки, инвертор 20, Т-триггер 21, тактовая шина 22 и шина 23 сброса.

Работа регистра сдвига заключается в следующем.

При t поступает через вход регистра на элемент ИЛИ б ячейки, памяти импульс запуска (фиг.2,а).причем подача запускающего импульса засинхронизирована с наличием на выходе элемента И 16 (фиг.2,к) высокого потенциала, а на выходе элемента И 17 (фиг.2,и; низкого потенциала, на первом входе элемента И 5 ячейки 1 памяти появляется высокий .сигнал, что приводят к появлению сигнала на выходе элемента И 55 (фиг.2,М). С выхода 7 ячейки 1 памяти сигнал поступает на первый вход элемента или 6 этой ячейки памяти и поддерживает высокий уровень на выходе этого элемента ИЛИ (фиг.2,а) до тех пор, пока уровень сигнала на выходе элемента И 16 не уменьшится. С выхода 7 сигнал черед элемент ИЛИ б поступает на первый вход элемента И 5 ячейки 2 памяти,но,поскольку на выходе элемента И 17 уровень сигнал низкий, то данная ячейка памяти не возбуждается.

При ti на вход 22 поступает тактовый импульс (фиг.2,6) и через элемент ИЛИ 12 - на вход Т-триггера 21 После окончания t. действия импульс (фиг.|,Ь) уровни сигнала на выходе Т-триггера 21 меняю11ся (фиг.2Я13 К .Для того, чтобы сигналы rfa выходах элементов И 16 и 17 были смещены др относительно друга на величину переходных процессов в ячейке 2 памяти регистра (элемента И 5) включены элементы 18 и 19 задержки, так что на выходе элемента ИЛИ 13 сигнал (фиг.2,е) уменьшается только при tj| , тогда как уровень на выходе элемента ИЛИ 14 возрастает при t,, . В соответствии с уровнями сигнала (фиг.2,е,ж) изменяется уровень на выходе элемента И 16 (фиг.2,ч) и И 17 (фиг.2,л).

При t,,, когда уровень на выходе элемента И 17 возрастает, увеличивается уровень на выходе элемента И 5 ячейки 2 памяти (фиг.2,п) и элемента ИЛИ 6 ячейки 1 памяти (фиг.1,р ) .

При tji, уменьшаются уровни сигнала на выходах элементов И 5, ИЛИ б ячейки 1 памяти.

При tg-t и происходит

аналогичная ситуация, за счет наложения двух тактовых сигналов. При. tg-t,o последующая ячейка памяти успевает возбудиться, но время задержки должно выбраться таким, чтобы оно не превышало переходные процессы одной ячейки памяти, в противном случае будет возбуждаться несколько ячеек памяти сразу, например две, хотя данный регистр допускает возбуждение двух ячеек памяти одновременно, т.е. проскакивание сигнала с предыдущей ячейки памяти на две последующих. Главное, чтобы не было просккивания сразу на три ячейки памяти. Возбуждение второй ячейки 2 памяти устраняется автоматически за счет того, что высокий потенциал остается только на одном из выходов элементов И 15 и 17.

При t поступает на шину 23 и на входы элементов И 15 и инвертора 20 импульс -сброса (фиг.2,6). На выходе инвертора 20 (фиг.2,,) уровень падает, так же как и на выходах элементов И 16 и 17, что приводит к обесточиванию всех ячеек памяти регистра и информация исчезает.

Поскольку для ввода информации необходимо, чтобы высокий сигнал был на выходе элемента И 16, а при сбросе этого может не получиться, поэтому сигнал с выхода элемента И 1 поступает на первый вход элемента ИЛИ 12, так, что, если при сбросе сигнал находится на единичном выходе Т-триггера 21, то импульс сброса поступает на вход Т-триггера 21 и при t,4 переводит его в другое состояние (фиг.2,д ие). После t регистр готов к приему информации.

Использование изобретения позволяет уменьшить число элементов на разряд сдвигающего регистра.

Формула изобретения

и второй входы которого соединен

соответственно с тактовой шиной и шиной сброса,о тличающийся тем,что, с целью упрощения регистра сдвига, в нем вторые входы элементов И четных ячеек памяти подключены, к первому выходу формирователя тактовых импульсов, ко второму выходу которого подсоединены вторые входы элементов И нечетных ячеек памяти, выход элемента И каяодой ячейки памяти соединен с первым входом элемента ИЛИ данной ячейки и с первым входом элемента ИЛИ последующей ячейки памяти.

и, другой вход которого соединен

с одним из выходов Т-триггера, вто- . рой вход первого элемента ИЛИ соединен с первым входом формирователя тактовых импульсов.

Источники информации,

принятью во внимание при экспертизе

Авторы

Даты

1981-08-15—Публикация

1979-07-24—Подача