(54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1982 |

|

SU1136217A1 |

| Ячейка памяти для регистра сдвига | 1978 |

|

SU752491A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU868836A1 |

| Элемент памяти для регистра сдвига | 1979 |

|

SU847373A1 |

| Устройство согласования | 1983 |

|

SU1138942A1 |

| Трехтактный регистр сдвига | 1976 |

|

SU752490A1 |

| Ячейка памяти | 1977 |

|

SU637866A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU902243A1 |

| Регистр сдвига | 1979 |

|

SU830579A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

I

Изобретение относится к вычислительной и импульсной технике и может быть использовано для построения сдвиговых регистров.

Известен трехтактный регистр, содержащий в каждом разряде регистра два триггера с принудительным обнулением, которые выполнены на элементах И-НЕ. Вход разряда подсоединен на вход установки в «1 первого триггера разряда. Сдвиговый регистр содержит также две шины тактовых импульсов, первая из которых служит для установки в «О нечетных, а вторая - чет ных триггеров регистра, а также содержит элемент установки в единицу второго триггера, а выход - с одним из входов установки нуля первого триггера. Третья тактовая шина подключена к выходам элементов установки в единицу второго триггера 1.

Недостатком регистра является большое число тактов, равное трем.

Известна ячейка памяти, выполненная на интегральных инжекционных логических () схемах.

Ячейка памяти содержит шесть многокол лекторных п-р-п-транзисторов, к базам ко-торых подключены инжекторы, при этом логическая развязка обеспечивается использованием коллекторных выходов в качестве независимых входов для следующих каскадов. Первый коллектор первого транзистора разряда соединен с базой второго транзистора первым тактовым входом и первым

коллектором шестого транзистора. Второй коллектор первого транзистора соединен с базой пятого транзистора и вторым коллектором щестого транзистора. Первый коллектор второго транзистора подсоединен к

,д базе первого транзистора и к выходу ячейки памяти. База третьего транзистора подсоединена к первому коллектору четвертого транзистора и второму коллектору второго. Первый коллектор третьего транзистора соединен с базой четвертого транзистора и с

15 третьим коллектором шестого транзистора. Коллектор пятого транзистора соединен с базой щестого транзистора и с вторым тактовым входом. Второй коллектор четвертого транзистора соединен с первым выходом ячейки памяти 2.

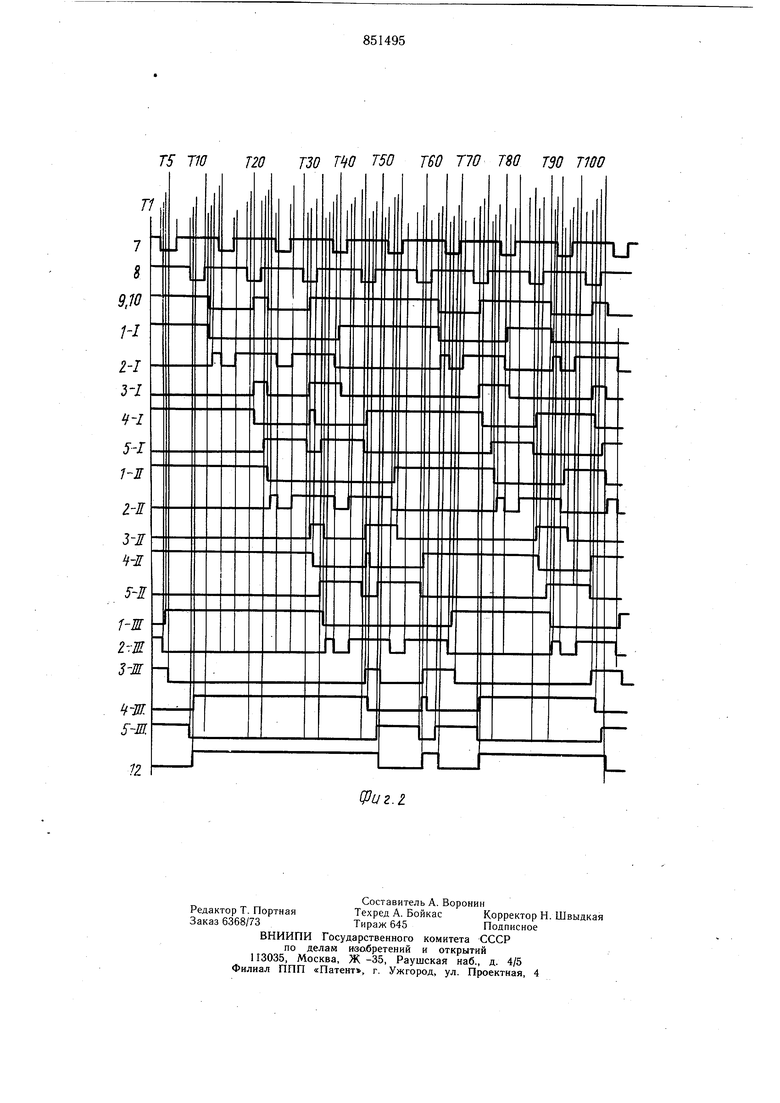

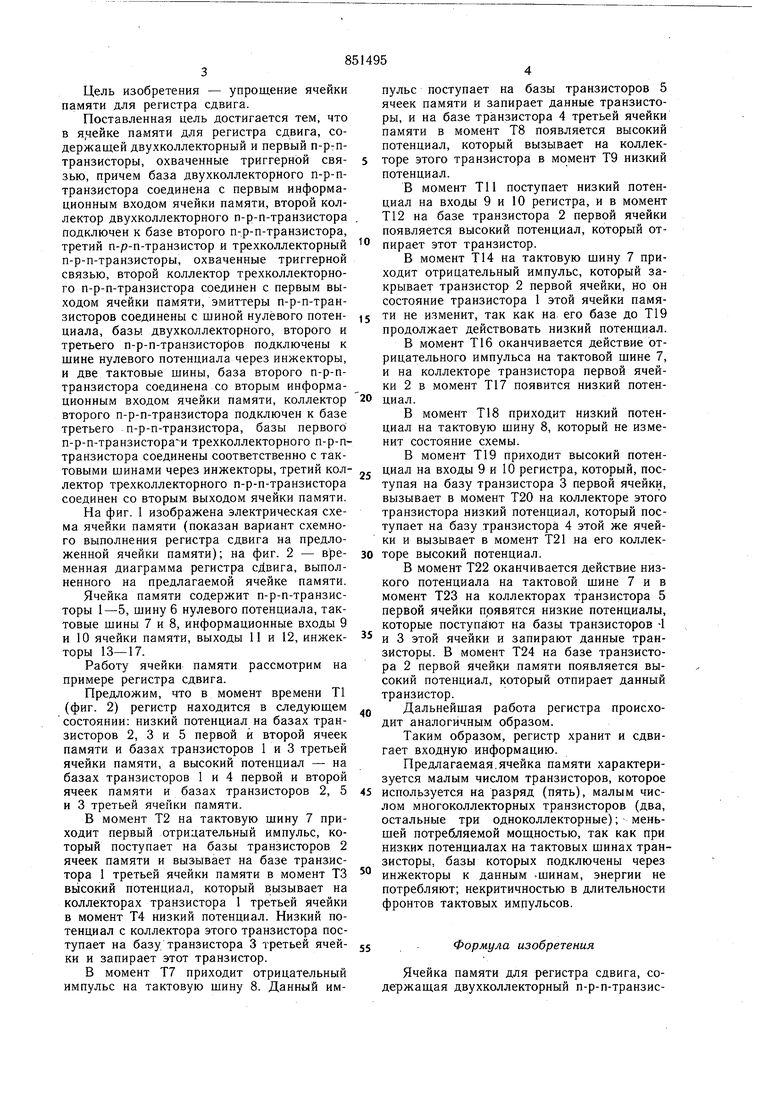

20 Недостатком данной ячейки памяти является большое число многоколлекторных транзисторов, равное шести, и большое число связей между транзисторами. Цель изобретения - упрощение ячейки памяти для регистра сдвига. Поставленная цель достигается тем, что в я,чейке памяти для регистра сдвига, содержащей двухколлекторный и первый п-р-птранзисторы, охваченные триггерной связью, причем база двухколлекторного п-р-птранзистора соединена с первым информационным входом ячейки памяти, второй коллектор двухколлекторного п-р-п-транзистора подключен к базе второго п-р-п-транзистора, третий п-р-п-транзистор и трехколлекторный п-р-п-транзисторы, охваченные триггерной связью, второй коллектор трехколлекторного п-р-п-транзистора соединен с первым выходом ячейки памяти, эмиттеры п-р-п-транзисторов соединены с шиной нулевого потенциала, базы двухколлекторного, второго и третьего п-р-п-транзисторов подключены к щине нулевого потенциала через инжекторы, и две тактовые шины, база второго п-р-птранзистора соединена со вторым информационным входом ячейки памяти, коллектор второго п-р-п-транзистора подключен к базе третьего п-р-п-транзистора, базы первого п-р-п-транзистораи трехколлекторного п-р-птранзистора соединены соответственно с тактовыми шинами через инжекторы, третий кол.. . лектор трехколлекторного п-р-п-транзистора соединен со вторым выходом ячейки памяти. На фиг. 1 изображена электрическая схема ячейки памяти (показан вариант схемного выполнения регистра сдвига на предложенной ячейки памяти); на фиг. 2 - временная диаграмма регистра сДвига, выполненного на предлагаемой ячейке памяти. Ячейка памяти содержит п-р-п-транзисторы 1-5, щину 6 нулевого потенциала, тактовые шины 7 и 8, информационные входы 9 и 10 ячейки памяти, выходы 11 и 12, инжекторы 13-17. Работу ячейки памяти рассмотрим на примере регистра сдвига. Предложим, что в момент времени Т1 (фиг. 2) регистр находится в следующем состоянии: низкий потенциал на базах транзисторов 2, 3 и 5 первой и второй ячеек памяти и базах транзисторов 1 и 3 третьей ячейки памяти, а высокий потенциал - на базах транзисторов 1 и 4 первой и второй ячеек памяти и базах транзисторов 2, 5 и 3 третьей ячейки памяти. В момент Т2 на тактовую шину 7 приходит первый отрицательный импульс, который поступает на базы транзисторов 2 ячеек памяти и вызывает на базе транзистора 1 третьей ячейки памяти в момент ТЗ высокий потенциал, который вызывает на коллекторах транзистора 1 третьей ячейки в момент Т4 низкий потенциал. Низкий потенциал с коллектора этого транзистора поступает на базу/транзистора 3 третьей ячейки и запирает этот транзистор. В момент Т7 приходит отрицательный импульс на тактовую шину 8. Данный импульс поступает на базы транзисторов 5 ячеек памяти и запирает данные транзисторы, и на базе транзистора 4 третьей ячейки памяти в момент Т8 появляется высокий потенциал, который вызывает на коллекторе этого транзистора в момент Т9 низкий потенциал. В момент Т11 поступает низкий потенциал на входы 9 и 10 регистра, и в момент Т12 на базе транзистора 2 первой ячейки появляется высокий потенциал, который отпирает этот транзистор. В момент Т14 на тактовую шину 7 приходит отрицательный импульс, который закрывает транзистор 2 первой ячейки, но он состояние транзистора 1 этой ячейки памяти не изменит, так как на его базе до Т19 продолжает действовать низкий потенциал. Б момент Т16 оканчивается действие отрицательного импульса на тактовой шине 7, и на коллекторе транзистора первой ячейки 2 в момент Т17 появится низкий потенциал. В момент Т18 приходит низкий потенциал на тактовую шину 8, который не изменит состояние схемы. В момент Т19 приходит высокий потенциал на входы 9 и 10 регистра, который, поступая на базу транзистора 3 первой ячейки, f fiа вызывает в момент Т20 на коллекторе этого транзистора низкий потенциал, который поступает на базу транзистора 4 этой же ячейки и вызывает в момент Т21 на его коллекторе высокий потенциал. В момент Т22 оканчивается действие низкого потенциала на тактовой шине 7 и в момент Т23 на коллекторах транзистора 5 первой ячейки появятся низкие потенциалы, которые поступают на базы транзисторов -1 jj 3 этой ячейки и запирают данные транзисторы. В момент Т24 на базе транзистора 2 первой ячейки памяти появляется высокий потенциал, который отпирает данный транзистор. Дальнейщая работа регистра происходит аналогичным образом. Таким образом, регистр хранит и сдвигает входную информацию. Предлагаемая.ячейка памяти характеризуется малым числом транзисторов, которое используется на разряд (пять), малым числом многоколлекторных транзисторов (два, остальные три одноколлекторные); меньшей потребляемой мощностью, так как при низких потенциалах на тактовых шинах транзисторы, базы которых подключены через инжекторы к данным .шинам, энергии не потребляют; некритичностью в длительности фронтов тактовых импульсов. Формула изобретения Ячейка памяти для регистра сдвига, содержащая двухколлекторный п-р-п-транзистор и. первый п-р-п-транзистор, охваченные триггерной связью, причем база двухколлекторного п-р-п-транзистора соединена с первым информационным входом ячейки памяти, второй коллектор двухколлекторного п-р-п-транзисТора подключен к базе второго п-р-п-транзистора, третий п-р-п-транзистор и трехколлекторный п-р-п-транзисторы, охваченные триггерной связью, второй коллектор трехколлекторного п-р-п-транзистора соединен с первым выходом ячейки памяти, эмиттеры п-р-п-транзисторов соединены с шиной нулевого потенциала, базы двухколлекторного, второго и третьего п-р-п-транзисторов подключены к шине нулевого потенциала через инжекторы, и две тактовые шины, отличающаяся тем, что, с целью упрощения ячейки памяти, в ней база второго 8 iir

П-р-п-транзистора, соединена со вторым информационным входом ячейки памяти, коллектор второго п-р-п-транзистора подключен к базе третьего п-р-п-транзистора, базы первого п-р-п-транзистора и трехколлекторного п-р-п-транзистора соединены соответственно с тактовыми шинами через инжекторы, третий коллектор трехколлекторного п-р-птранзистора соединен со вторым выходом ячейки памяти.

Источники информации, принятые во внимание,при экспертизе

Г5 по Г20 ТЗО TW Т50 Т60 Г70 780 ТЗО 7100

(риг. 2.

Авторы

Даты

1981-07-30—Публикация

1979-10-02—Подача